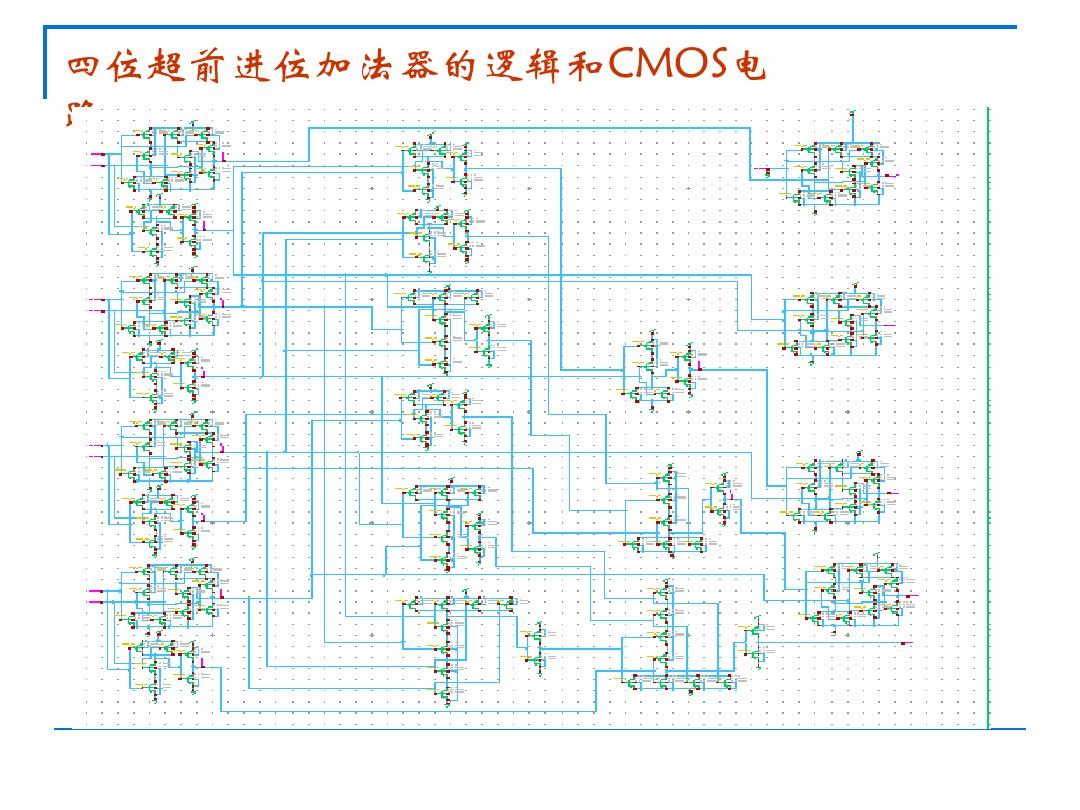

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器是通過增加了一個不是十分複雜的邏輯電路來做到這點的。

基本介紹

- 中文名:超前進位加法器

- 外文名:carry look ahead adder

簡介

原理

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器是通過增加了一個不是十分複雜的邏輯電路來做到這點的。

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器...

先行進位加法器,各級的進位彼此是獨立產生,只與輸入數據A,B和C_in有關,將各級間的進位級聯傳播給去掉了,這樣就可以減小進位產生的延時。...

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用...

1 簡介 ▪ 半加器 ▪ 全加器 2 更複雜的加法器 ▪ 波紋進位加法器 ▪ 超前進位加法器 電子加法器簡介 編輯 儘管...

實現多為二進制數相加的電路,稱為加法器。根據進位方式不同,有串列進位加法器和超前進位加法器之分。(1)串列加法進位從最低位進到最高位,即整個進位是分若干...

實現多位數相加的具體電路是很多的,其中有一種就是採用所謂並行相加、逐位進位的方式。逐位進位的加法器,邏輯電路比較簡單,缺點是運算速度比較慢,因為最高位的加法...

多位加法器是兩個多位數相加時每一位都是帶進位相加的,因而必須使用。...... 多位加法器是兩個多位數相加時每一位都是帶進位相加的,因而必須使用。...

我們知道,超前進位並行加法器74LS283可以實現四位二進制數的相加,於是,我們需要兩個74LS283進行串聯,這樣我們就得到一個新的九位二進制數,其範圍在000到510之間...

②超前進位加法器:所謂超前進位,就是在作加法運算時,各位數的進位信號由輸入的二進制數直接產生 [1] 。組合邏輯電路編碼器 1.基本概念用代碼表示特定信號的過程...

6.3.3 超前進位與異步進位加法器的組合 1816.4 比較器 1826.4.1 相等 1826.4.2 不相等 1836.5 解碼器 1856.5.1 基本二進制解碼器 185...

組合邏輯電路函式、鎖存器、計數器、移位暫存器、存儲器、數位訊號處理、積體電路...6.1 基本加法器6.2 並行二進制加法器6.3 異步進位與超前進位加法器...

實例7-2—超前進位加法器 165實例7-3—移位除法器模型 1697.7 習題 174第8章 有限狀態機設計 1758.1 有限狀態機簡介 1758.2 兩種紅綠燈電路的狀態機模型 ...

觸發器,時序邏輯電路,脈衝波形的產生與變換,數字系統設計基礎,數模與模數轉換,...4.7.3 超前進位加法器74283 82*4.8 組合邏輯電路的競爭冒險 84...

7.4 實驗3 交通燈控制器 7.5 實驗4 超前進位加法器和算術邏輯單元 7.6 實驗5 數字乘法器 7.7 實驗6 CRC信道編解碼電路 附錄一 常用數字積體電路 附錄二 基...

3.4快速加法器1453.4.1超前進位加法器1463.5用CAD工具設計算術電路1513.5.1用原理圖編輯工具設計算術電路1513.5.2用Verilog設計算術電路152...

5.1 藥片瓶裝系統1535.2 半加器與全加器1575.3 並行加法器1595.4 串列進位與超前進位加法器1635.5 比較器1655.6 解碼器1675.7 編碼器1735.8 碼轉換器176...

布爾代數與邏輯設計、布爾函式的化簡、存儲器、暫存器、處理器等元器件的設計和...5.2 超前進位加法器 5.3 加法器/減法器 5.4 邏輯單元 5.5 算術邏輯單元...

10.2.2 超前進位加法器10.2.3 上溢出和下溢出10.3 乘法運算功能單元10.3.1 組合(並行)二進制乘法器10.3.2 時序二進制乘法器...