基本介紹

- 中文名:電子加法器

- 外文名:Electronic adder

- 領域:電子計算機

簡介

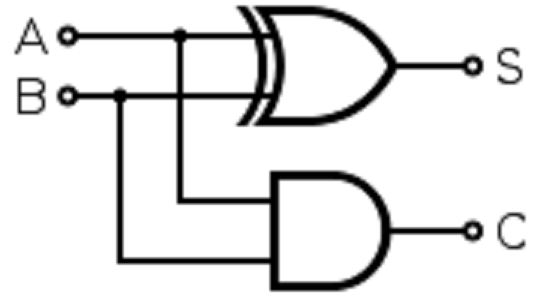

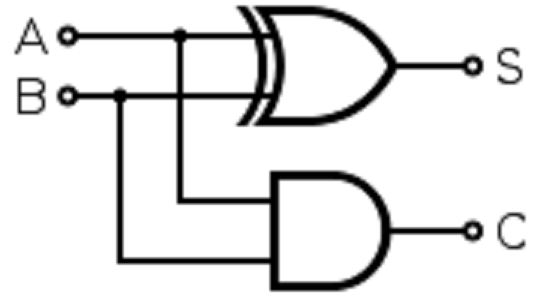

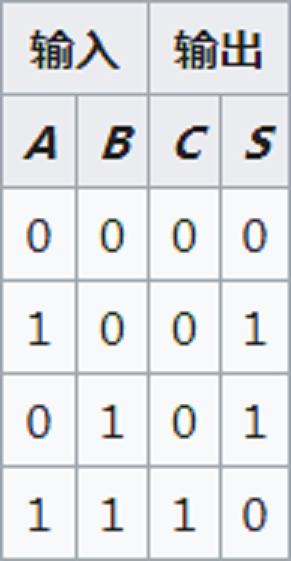

半加器

一位半加器的符號

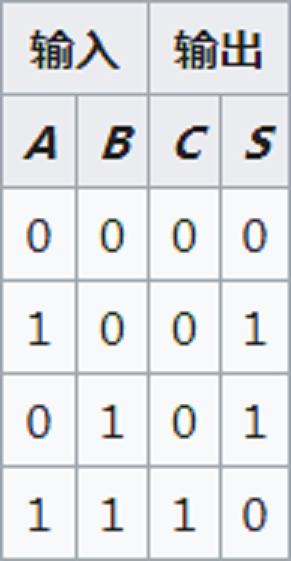

一位半加器的符號 半加器的真值表

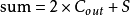

半加器的真值表全加器

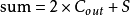

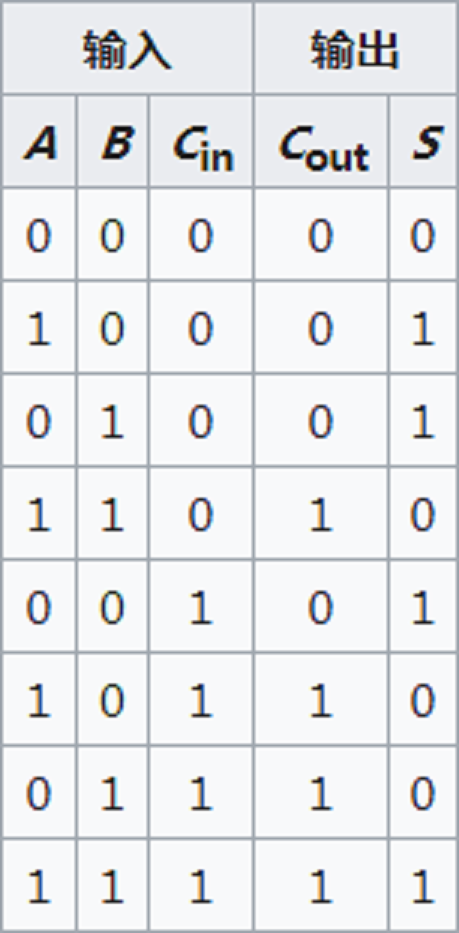

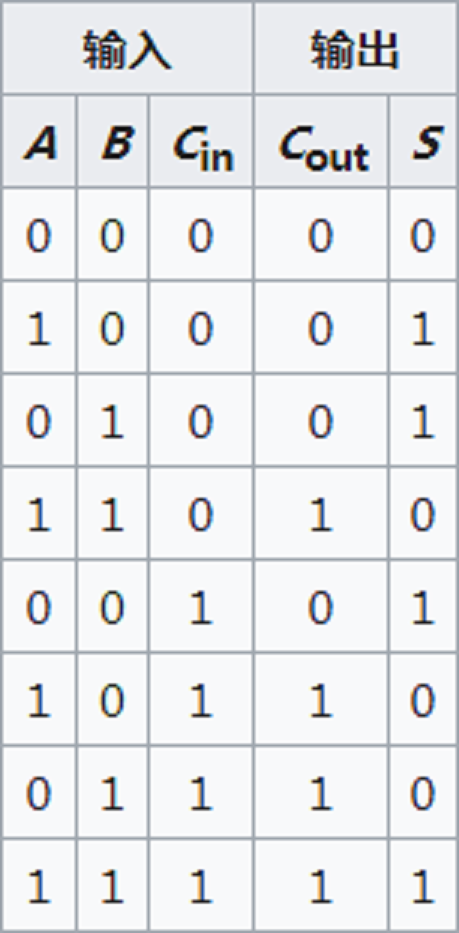

全加器真值表

全加器真值表

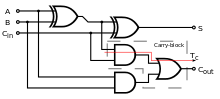

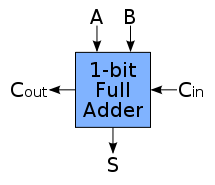

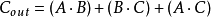

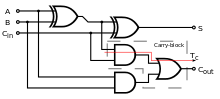

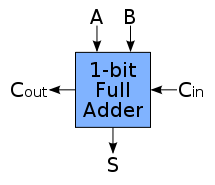

全加器的符號

全加器的符號

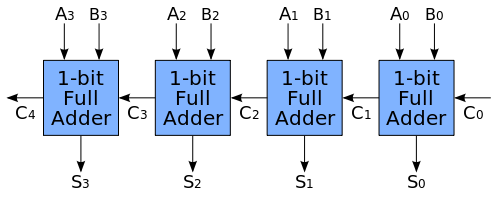

多位二進制數加法器

多位二進制數加法器

更複雜的加法器

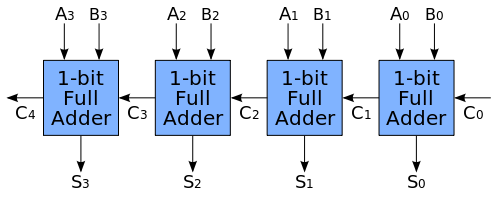

波紋進位加法器

波紋進位加法器

波紋進位加法器

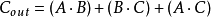

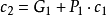

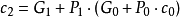

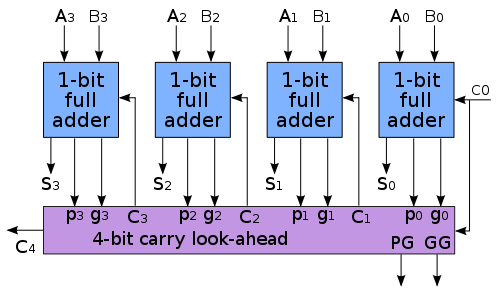

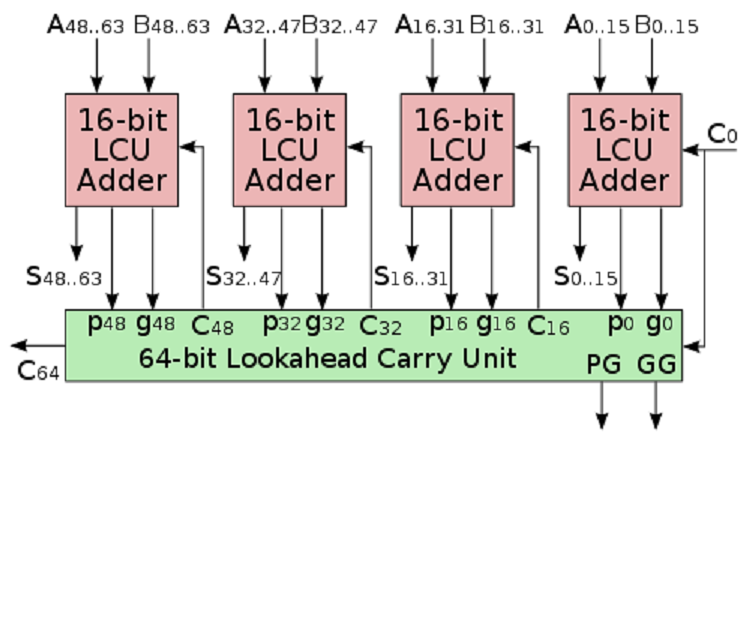

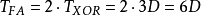

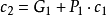

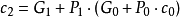

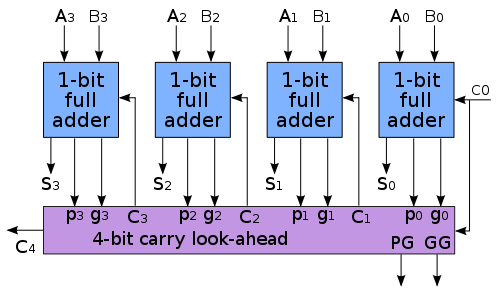

超前進位加法器

四位超前進位加法器

四位超前進位加法器

一位半加器的符號

一位半加器的符號 半加器的真值表

半加器的真值表

全加器真值表

全加器真值表

全加器的符號

全加器的符號

多位二進制數加法器

多位二進制數加法器

波紋進位加法器

波紋進位加法器

四位超前進位加法器

四位超前進位加法器電子加法器是一種用於執行加法運算的數字電路部件,是構成電子計算機核心微處理器中算術邏輯單元的基礎。在這些電子系統中,加法器主要負責計算地址、索引等數據。除此...

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用...

多位加法器是兩個多位數相加時每一位都是帶進位相加的,因而必須使用。...... 多位加法器是兩個多位數相加時每一位...1. 閻石.數字電子技術基礎(第五版):高...

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加並求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,並輸出本位加法進位。多個一位...

加法器是常用的組合邏輯電路之一,可分為半加器和全加器。計算機對所有數據的處理本質上是對二進制數的處理。而人類熟悉的數據是十進制的,故我們需要設計出來十...

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器...

《電子技術基礎(3)》作為我國高等教育組成部分的自學考試,其職責就是在高等教育...6.4.1 加法器 6.4.2 編碼器 6.4.3 解碼器 6.4.4 數據選擇器 6.4....

《電子技術基礎(李效芳)》是2015年西安電子科技大學出版社出版的圖書,作者是李...10.4.4 解碼器的套用 20610.5 加法器 20710.5.1 半加器 207...

6.2 加法器設計6.3 時序邏輯電路設計6.4 TTL與CMOS的接口電路設計第三篇 抗干擾設計第七章 抗溫度干擾設計7.1 溫度干擾對電子電路的影響...

《數字電子》根據中等職業學校電氣控制與維修專業理論實踐一體化課程教學大綱,參照國家職業標準編寫。主要內容包括:組合邏輯電路、觸發器、時序邏輯電路、脈衝信號的產生...

《圖解電子電路的計算》簡介:本套叢書系引進歐姆社著作權翻譯出版的中文版圖書。...5.6 加法器Ⅵ 調製解調及其基本電路6.1 調製(把聲音載入到電波上)...

串列二進制加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。...

項目實施12 用運放構成的比例放大器和加法器的設計與調試項目拓展4 電子秤壓力信號放大電路的分析與測試思考與練習題5課外閱讀22 國產三極體的命名方法...

人類第一台電子數字計算機ENIAC(Elec-tronic Numerical Integrator And Computer埃...年,法國數學家帕斯卡採用與鐘錶類似的齒輪傳動裝置,製成了最早的十進制加法器。...

《電子技術基礎(數字部分)》可作為全國招收國中五年制高職和中等專業學校工科電工...3.5.2 全加器3.5.3 多位二進制加法器3.6 數據選擇器和數據分配器...

《電子線路設計與套用》是為高等學校工科電類專業編寫的一本寬口徑、厚基礎的...2.5 十進制加法器設計2.6 四位乘法器2.7 集成觸發器的功能測試...

《電子技術》是2010年人民郵電出版社出版的圖書,作者是劉進鋒。本書可作為高等...項目二 加法器的識別及功能測試 174一、項目導入 174二、相關知識 174...

《電工電子學(王智忠)》是2015年西安電子科技大學出版社出版的圖書,作者是王智忠...14.3.2 全加器 330 [1] 14.4 編碼器 33114.4.1 二進制編碼器 332...

《電子電路計算機仿真設計與分析》是2006年電子工業出版社出版的圖書。本書基於...8.2 編碼器電路8.3 解碼器電路8.4 數據選擇器及其套用8.5 加法器...

《電子技術》是機電一體化技術等專業重要的技術基礎課,包括“模擬電子、數字電子...3.3.1 加法器3.3.2 編碼器3.3.3 解碼器*3.3.4 比較器...