減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網路所構成的運算電路來實現。

基本介紹

- 中文名:減法器

- 外文名:subtracter

- 學科:計算機科學與技術

- 類別:基本集成運放電路

- 分類:半減器、全減器

- 電路構成:差分電路

基本概念,加法電路,減法電路的實現,利用反相信號求和以實現減法運算,利用差分式電路以實現減法電路,減法器的設計,半減器,全減器,四位二進制減法器的設計與實現,總體方案設計,被減數模組的設計,減數模組的設計,差模組的設計,

基本概念

信號處理電路的內容比較廣泛,包括有源濾波、精密二極體整流電路、電壓比較器和取樣-保持電路等。而這些信號處理電路都是由最基本的集成運放電路經過綜合設計而成的。因此對基本集成運放電路的熟悉和應運尤為重要。 基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網路所構成的運算電路來實現。

減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。

加法電路

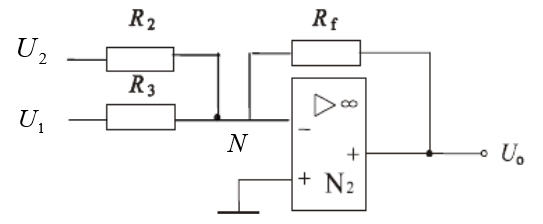

如果將兩個電壓相加,可以利用圖1所示電路來實現,這個電路接成反相放大器。

圖1

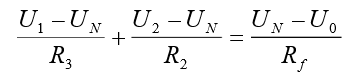

利用虛短和虛斷的概念,N接點的接點方程為:

當 時,

時,

如圖1所示的電路可以擴展到多個輸入電壓相加。

減法電路的實現

利用反相信號求和以實現減法運算

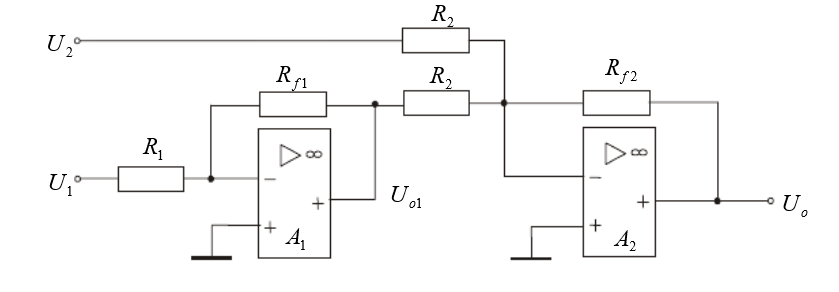

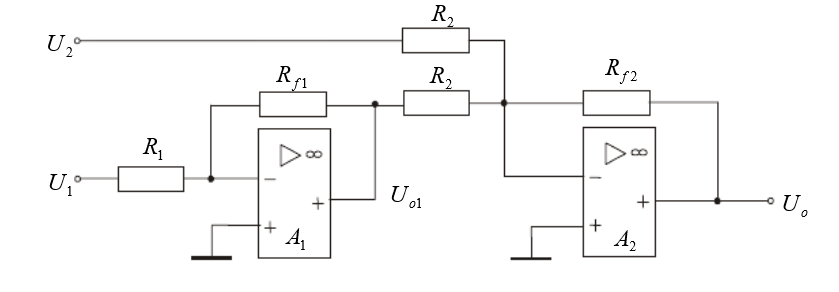

如圖2所示,第一級為反相比例放大電路

圖2

若 ,則

,則 ;第二級為反相加法電路,則可導出

;第二級為反相加法電路,則可導出

若 ,則

,則

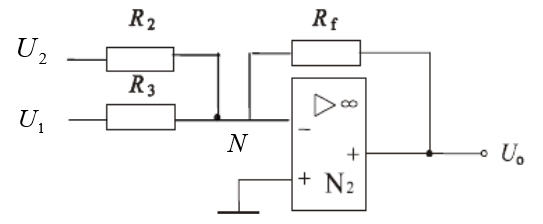

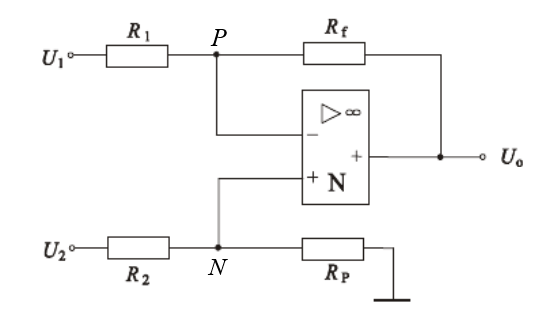

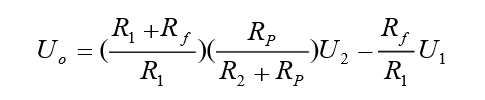

利用差分式電路以實現減法電路

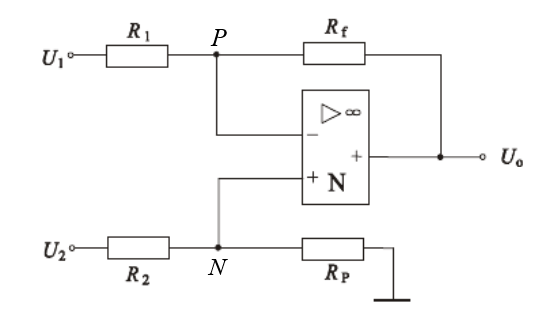

圖3所示是用來實現兩個電壓相減的電路

圖3

從電路結構上來看,它是反相輸入和同相輸入相結合的放大電路。在理想運放情況下,電路看成虛短現象,節點方程:

其中 ,則

,則

在上式中,如果滿足 ,輸出電壓可簡化為:

,輸出電壓可簡化為:

此差分式減法電路由於製作簡單,故成為實驗首選,廣泛應運於各種信號的減法運算。

減法器的設計

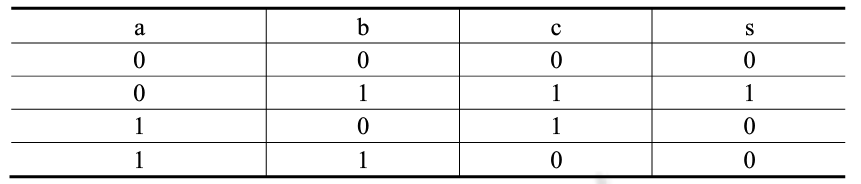

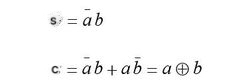

半減器

我們根據半減器的功能列出真值表:

由真值表可得到c和s邏輯的表達式:

全減器

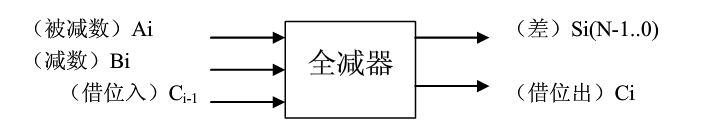

全減器考慮低位向本位的借位。一位全減器有三個輸入、兩個輸出,如下圖。圖中的“借位入”即低位向本位的借位,也就是低位的“借位出”。

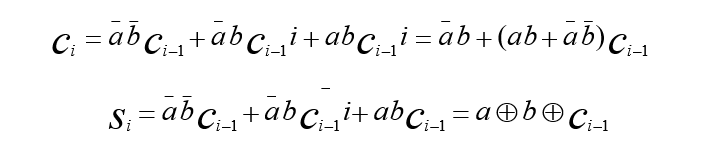

下表為一位全減器真值表,由此表可寫出一位全減器關於Ci與Si的邏輯表達式:

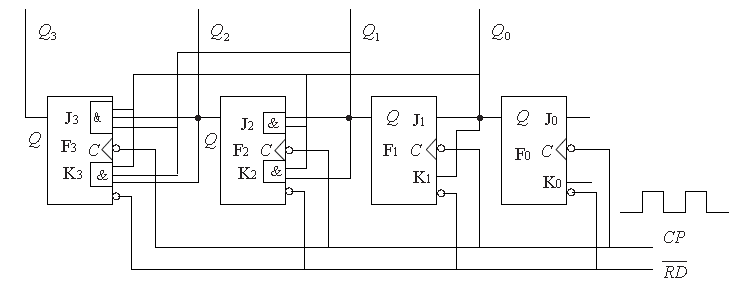

四位二進制減法器的設計與實現

目前,隨著社會的進步與信息技術的高速發展,高集成化已逐步滲入到各個領域。高效率、高品質的生活狀態也是我們的追求。電路設計也追求高集成化,高效率化。傳統的費時又費力的電路設計當被捨棄。下面使用EWB 和74LS48等完成了四位二進制的設計,實現了節省時間、節約成本並且節約勞力的目標。

總體方案設計

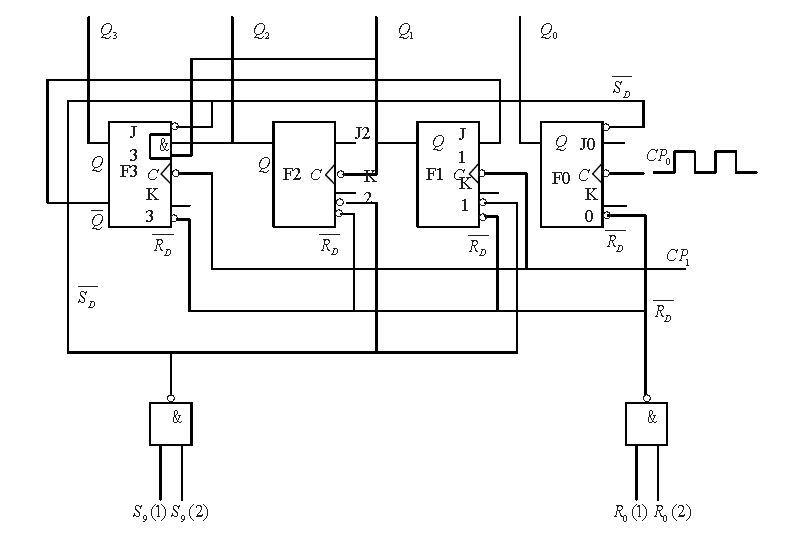

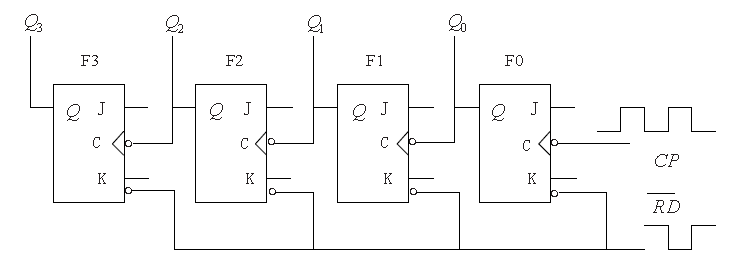

本設計使用EWB進行仿真,使用74LS48、七段解碼器、LED、開關、異或門、或門、非門、與非門等。電路按功能分為三個部分:

(1)減數部分:減數變成補碼(原碼取反加1);

(2)被減數部分:被減數與減數的補碼相加;

(3)差部分:被減數減減數的結果顯示。

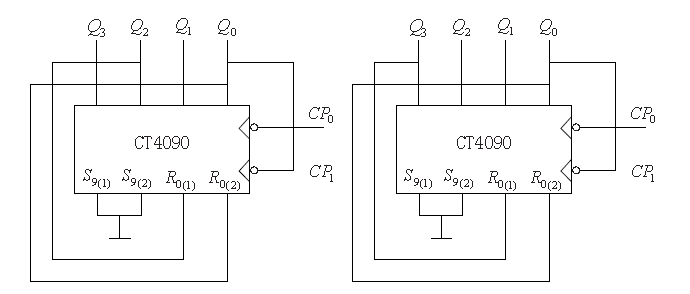

四位二進制減法器的總體仿真圖如圖所示:

被減數模組的設計

本模組由開關、74LS48、VCC(+12 V)、GND、七段解碼器構成,用開關控制輸入信號( 被減數),5、6、7、8 從高位到低位,用74LS48和七段解碼器構成顯示電路。四位二進制減法器的被減數模組的仿真圖如圖所示:

減數模組的設計

本模組由開關、74LS48、VCC(+12 V)、GND、七段解碼器、異或門、或門、非門、與非門構成。用開關控制輸入信號(減數),1、2、3、4 從高位到低位,將輸入信號的原碼變成補碼供計算使用,用74LS48 和七段解碼器構成顯示電路。四位二進制減法器的減數模組的仿真圖如圖所示:

差模組的設計

本模組由VCC(+12 V)、GND、七段解碼器、74LS48、LED 構成。從右到左依次是從高位到低位,並用74LS48和七段解碼器構成顯示電路。四位二進制減法器的差模組的仿真圖如圖所示: