串列二進制加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。

基本介紹

- 中文名:串列二進制加法器

- 外文名:serial binary adder

- 學科:計算機科學與技術

- 類別:加法器

- 方式:串列進位

- 優點:電路簡單

基本概念,串列二進制加法器設計,1位串列加法器,2位串列加法器,串列進位加法器和超前進位加法器,

基本概念

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。PU、MCU及DSP等電子器件中的加法運算是最基礎、最常見的運算方法,常見加法器是位並行的,在一個時鐘周期內完成加法運算。由於傳統加法器位數有限,所以傳統計算機能運算的數值範圍是有限的,能精確到的浮點數位數是有限的。如果將傳統加法器設計為位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果由並行輸入/輸出改為隨時鐘串列輸入/輸出,比如由低到高串列輸入0101和1001到位串列加法器,輸出結果就是1110由低位到高位輸出的數字波形,則其運算結果就可以存入FIFO或RAM 中,這樣不僅能夠提高加法器處理數值的上限,而且也能減少硬體資源的套用。

串列二進制加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。位並行加法器速度高,但是占用資源多。在許多實際套用中並不需要這樣高的速度,而是希望減少硬體資源占用率,這時就可以使用串列二進制加法器。

串列二進制加法器設計

1位串列加法器

二進制數的加法過程是從最低位開始的,低位決定進位數:1和1相加就進1,其他進位0。下一位運算元與上一位進位決定本位相加結果:進位和運算元中1的個數不大於1則進位為0,否則進位為1。

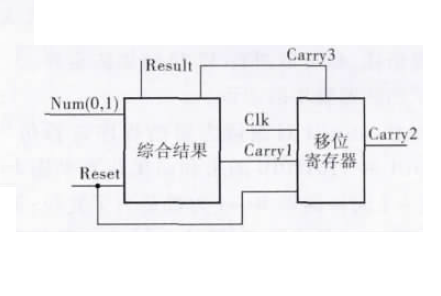

圖1

位串列加法器採用輸入時鐘Clk來控制加法器的操作,其邏輯如圖1所示,輸入信號Num(0,1)代表兩個加法運算元Num(0) 和Num(1);Reset是復位端,低電平時復位;Clk 是同步時鐘;Carry1、Carry2和Carry3是Num(0) 和Num(1)對應位相加的進位結果。要完成整個加法操作,主要是進位和本位運算元相加,而進位結果是由低位決定的。所以本位運算結果輸出後,必須保留進位到下兩位運算元到來,這樣運算元才能實現和上一位進位結果一起運算。由於最低位沒有進位,它的處理方式稍有特殊:在上電復位後Carry3為0,所以可以用該時刻的0作為最開始兩位運算元的進位,具體操作步驟如下:

a.Num(0) 和Num(1) 的求和結果與進位結果,通過組合邏輯電路分別輸出到Result 端和Carry1。

b.Clk上升沿到來後Carry1才賦值給Carry2,Carry2 移位至Carry3;Clk下降沿到來時,重複上次移位操作,此時Carry3就是第一位運算元的進位。

c.運算元第二位輸入與Carry3求和,回到步驟a。依此循環,直到結果輸出完畢。

2位串列加法器

在數字串列加法器中,字長為W的運算元被分為P個位寬為N(N能被W整除,P=W/N)的數字,然後從低位開始相加,在P個時鐘內完成加法操作。P個時鐘周期稱為一個採樣周期(Sample Period)。

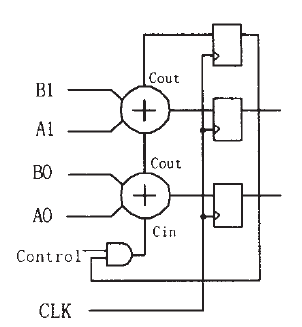

2位串列加法器,即N=2的串列加法器結構如圖所示:

如果輸入運算元的字長為8,那么串列加法器可以在4個時鐘周期內完成加法運算。這個加法器只用了兩個全加器的資源,比一般的8bit行波進位加法器小。

數字串列加法器的控制也比較簡單,輸入移位暫存器完成並行-串列轉換功能。通過移位操作不斷為加法器提供位寬為N的運算元;control信號指示了新採樣周期的開始,此時carry清零;輸出移位暫存器完成串列-並行轉換,輸出計算結果。

對於特定的輸入字長,通過選擇不同的N,可以實現速度、面積不同的數字串列加法器。這樣,設計者可以根據實際情況加以選擇,提高了設計的靈活性。

串列進位加法器和超前進位加法器

實現多為二進制數相加的電路,稱為加法器。根據進位方式不同,有串列進位加法器和超前進位加法器之分。

(1)串列加法進位從最低位進到最高位,即整個進位是分若干步驟進行的。優點是電路結構簡單,缺點是運算速度慢。

(2)超前進位的所有位數進位是同時完成的,一個CP脈衝就能完成整個進位過程。優點是運算速度快,缺點是電路複雜。