8位加法器就是實現兩個 8位二進制相加,其結果的範圍應該在00000000到111111110之間,八位二進制數換算成三位十進制數最大為255,也就是說要輸入兩個000到255之間的數。

基本介紹

- 中文名:八位加法器

- 外文名:eight bit adder

- 學科:計算機科學與技術

- 類別:加法器

- 基本釋義:兩個 8位二進制相加

- 十進制:0到255之間的數

法器概念,設計思路,方案一,方案二,方案三,實現,系統框圖,原理,加法器介紹,

法器概念

加法器是實現兩個二進制數相加運算的基本單元電路。8位加法器就是實現兩個 8位二進制相加,其結果的範圍應該在00000000到111111110之間,八位二進制數換算成三位十進制數最大為255,也就是說要輸入兩個000到255之間的數。

設計思路

8位二進制加法器,它的功能主要是實現兩個8位二進制數的相加,其結果的範圍應該在00000000到111111110之間,八位二進制數換算成三位十進制數最大為255,也就是說要輸入兩個000到255之間的數。要實現它們的相加,下面有三種方案。

方案一

當輸入兩個三位十進制數時,由於在數字電路中運算所用到的是二進制數,因此我們必須首先將十進制數轉換為二進制數,於是一個問題出現了,那就是,我們如何實現十進制數到二進制數的轉換,通過查閱相關資料,我們發現二-十進制編碼器(也叫8421BCD碼編碼器,在實際中通常指74LS147)可以實現從十進制數到二進制數的轉換,於是我們通過二-十進制編碼器來實現上述的轉換。由於二-十進制編碼器可以實現一位十進制數到四位二進制數的轉換,而題目中的是兩個三位十進制數,因此我們就需要用到6個二-十進制編碼器,分別將三位十進制數的個位、十位、百位轉換為其各自對應的8421BCD碼,於是我們得到了兩個十二位的8421BCD碼。於是如何實現兩個三位十進制數的相加這個問題就變成了如何實現兩個十二位的8421BCD碼相加這個新問題。那么,如何實現呢?我們想到了加法器,常用的加法器74LS283能夠實現四位二進制數的相加,於是我們就要將74LS283進行串聯,實現十二位數的相加,但加法器74LS283的進位是逢16進1,而這兩個十二位的8421BCD碼相加時的進位是逢10進1,那么就要對加法器74LS283的二進制和數進行修正,即加上一個6(0110),讓其產生一個進位。於是把大於9的項畫在卡諾圖裡,另外考慮到若相加產生進位,則同樣出現大於9的情況。綜合考慮,得到修正和數的條件,用與非門和與門來實現,得到了一個新的加法器,它可以實現逢10進1這個條件。將這兩個十二位的8421BCD碼分別接到三個新的加法器的輸入端,得到一個新的十二位的8421BCD碼。由於結果要得到一個三位十進制數,因此再將這個十二位的8421BCD碼通過三個7447七段顯示解碼器轉換為一個三位十進制數,通過數碼管將它顯示出來,即為所求的結果。

方案二

當輸入的不是三位十進制數而是八位二進制數時,我們如何實現它們的相加呢?我們知道,超前進位並行加法器74LS283可以實現四位二進制數的相加,於是,我們需要兩個74LS283進行串聯,這樣我們就得到一個新的九位二進制數,其範圍在000到510之間。那么我們如何實現從九位二進制數到三位十進制數的轉換呢?我們就想到了數碼轉換器,通過74185晶片來實現字碼的轉換。這樣,就得到了一個新的十二位8421BCD碼,再通過7447七段數碼顯示解碼器來實現8421BCD碼到三位十進制數的轉換,最後通過數碼管顯示出來,得到的就是所要求的的八位二進制數的和。

方案三

通過上述兩種思路,我們會要進一步想到,能不能同時實現八位二進制數和三位十進制數的相加呢?那么我們可以對上述的思路加以擴展,假設輸入的是三位十進制數,我們可以設法將其轉換為BCD碼,再通過加法器輸出。這樣,我們既可以輸入三位十進制數,也可以輸入八位二進制數。那么三位十進制數如何轉換為八位二進制數呢?我們想到了二-十進制編碼器,一個二-十進制編碼器可以實現一位十進制數到四位二進制數的轉換,那么我們就可以將一個二-十進制編碼器和一些與非門組成一個新的二-十進制編碼器來實現這個三位十進制數的十位到8421BCD碼的轉換;同理,三位十進制數的百位也可以這樣轉換。於是三位十進制數就轉換到了八位二進制數,接著,我們就可以用第二種思路來實現八位二進制數的相加。

實現

通過以上三種思路,經過分析驗證,在實踐論證中我們發現,由於第一種思路所用的元件少,且個位、十位、百位各自對稱,因此在連線上方便可行,不易出錯。同時由於原理清晰,一旦出現錯誤,我們可以儘快發現問題並加以改正。在論證第二種思路時,我們發現,在使用解碼器時,由於使用的是4線-16線解碼器74LS154,因此它有16個出線端。而我們要實現九位二進制數到十二位BCD碼的轉換,就要有512個出線端,也就是512除以16,即32個解碼器。由於所用到的解碼器數量冗長,在連線上容易出錯。因此並不採納。同理,第三種思路也是如此。

系統框圖

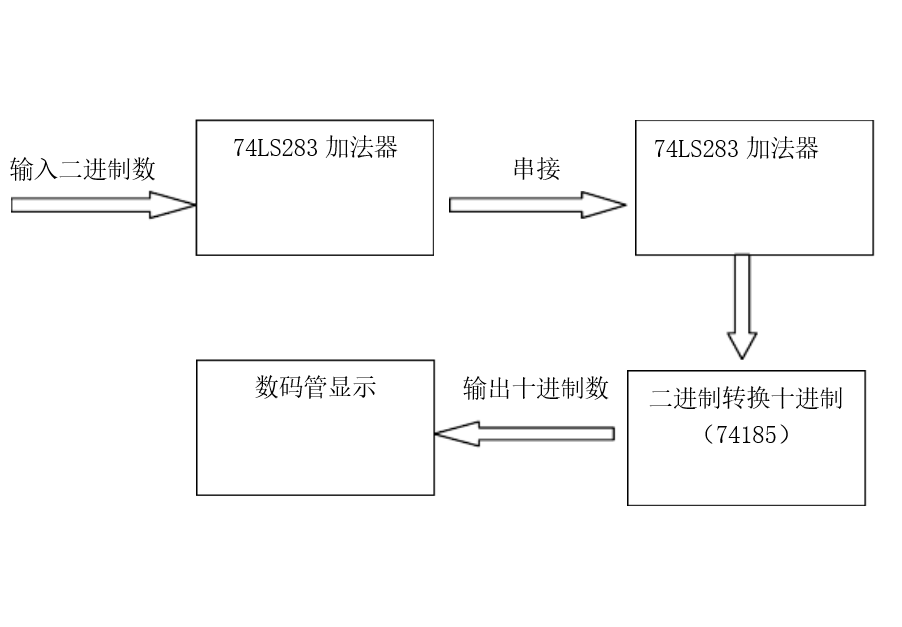

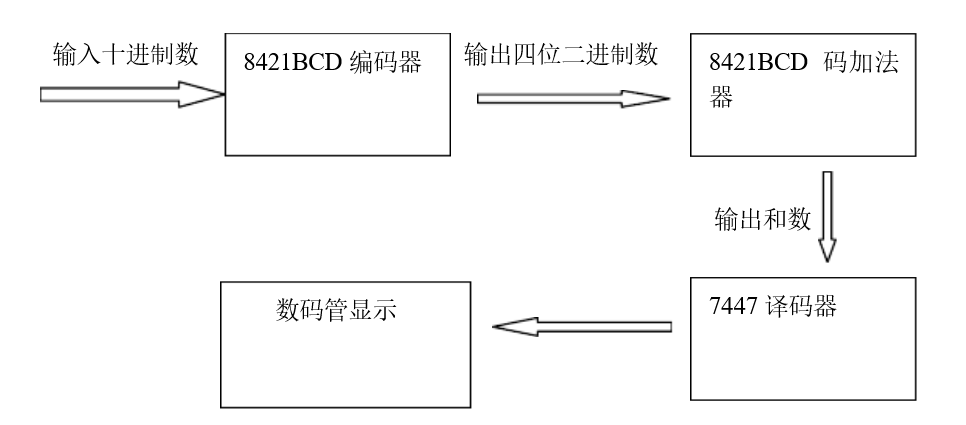

當輸入為十進制數時:

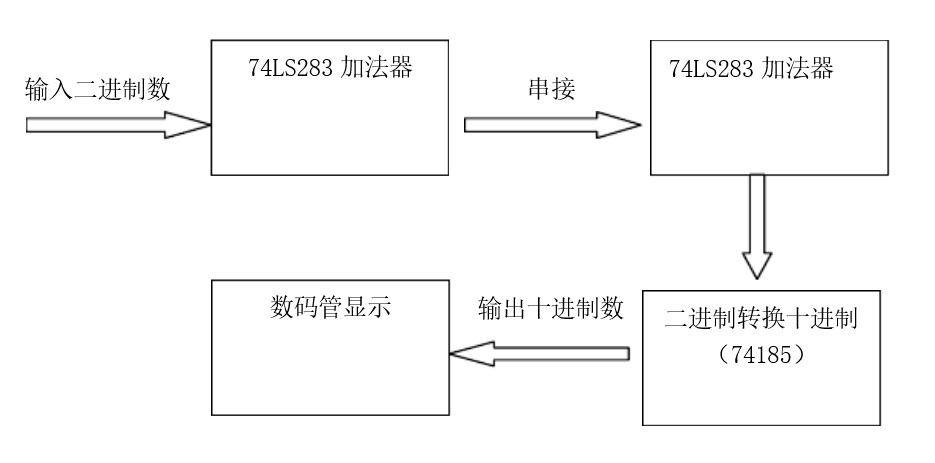

當輸入為二進制數時:

原理

當輸入十進制數的時候,8421BCD碼編碼器先開始工作,編碼器先將十進制數轉換成四位二進制數,輸出的四位二進制數直接到達8421BCD碼加法器的輸入端,我們可以使用71LS185加法器構成的一位8421BCD碼的加法器,8421BCD碼是用4位二進制數表示1位十進制數,4位二進制數內部為二進制,8421BCD碼之間是十進制,即逢十進一。而四位二進制加法器是按四位二進制數進行運算,即逢十六進一。二者進位關係不同。當四位二進制數加法器74LS283完成這個加法運算時,要用兩片74LS283。第一片完成加法運算,第二片完成修正運算。8421BCD碼加法器工作時,8421BCD碼的加法運算為十進制運算,而當和數大於9時,8421BCD碼就產生進位,而此時十六進制則不一定產生進位,因此需要對二進制和數進行修正,即加上6(0110),讓其產生一個進位。當和數小於等於9時,則不需要修正或者說加上0。因此我們可以通過三個8421BCD碼加法器的相連組成一個三位串列進位並行加法器,這樣通過低位向高位產生進位進行十進制的加法運算,最後通過連線數碼管顯示所得的結果。當輸入二進制數的時候,兩個串接的74LS283四位加法器進行加法運算,產生的八位二進制數通過集成晶片轉換成三位十進制數,最後通過數碼管顯示。

加法器介紹

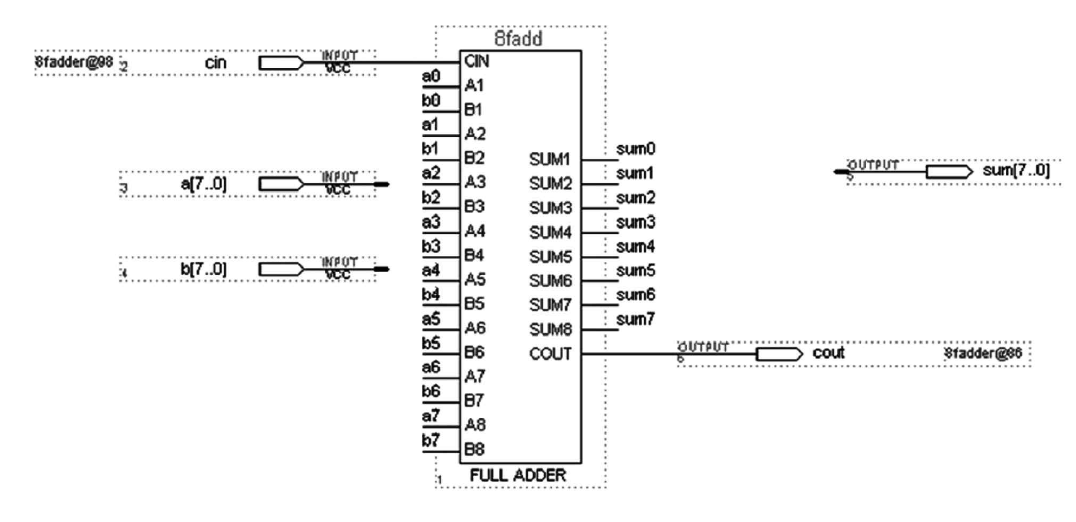

原理圖輸入方式

原理圖輸入,這是一種最直接的設計輸入方式,它使用軟體系統提供的器件庫及各種符號和連線畫出設計電路的原理圖,形成圖形輸入檔案。這種方式大多用在設計者對系統及各部分電路很熟悉或系統對設計特性要求較高的場合。優點是容易實現仿真,便於信號的觀察和電路的調整。

由於MAX+PLUSII軟體的宏函式館種有8位加法器的元件,這樣我們只要調用出這個8fadd元件,再加上輸入、輸出即可。整體設計如圖:

文本輸入法

文本輸入是指採用硬體描述語言進行電路設計的方式。硬體描述語言有普通硬體描述語言和行為描述語言,它們用文本方式描述設計和輸入。行為描述語言是目前常用的高層硬體描述語言,有VHDL和Verilog HDL等,這裡用VHDL,它具有很強的邏輯描述和仿真功能,可實現與工藝無關的編程與設計,輸入效率高,在不同的設計輸入庫之間轉換也非常方便。運用VHDL等硬體描述語言進行設計已是當前的趨勢。8位加法器用文本輸入法輸入也非常簡單方便。下面是8位加法器的VHDL源程式:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.A L L ;

ENTITY adder8 IS

PORT(CIN:IN INTEGER RANGE 0 TO 1;

A:IN INTEGER RANGE 0 TO 255;

B:IN INTEGER RANGE 0 TO 255;

SUM:OUT INTEGER RANGE 0 TO 255;

COUT:OUT INTEGER RANGE 0 TO1);

END adder8;

ARCHITECTURE a OF adder8 IS

SIGNAL SINT:INTEGER RANGE 0 TO 511;

BEGIN

SINT <= A + B + CIN ;

SUM <= SINT WHEN SINT <= 255

ELSE

SINT-256;

COUT <= 0 WHEN SINT <= 255

ELSE 1 ;

END a ;