可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。

基本介紹

- 中文名:可程式邏輯器件

- 外文名:programmable logic device

- 簡稱: PLD

- 作用:通用積體電路

- 分類:固定邏輯器件和可程式邏輯器件

概念

發展歷史

分類

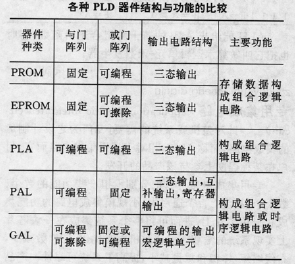

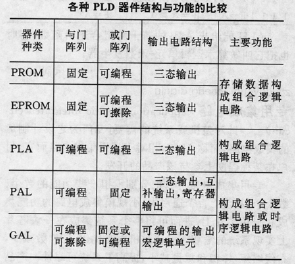

對比

PLD(可程式邏輯器件)一般指本詞條

可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。

PLD中文名是保蘭德,是義大利一家精品皮具製造商的品牌。同時在計算機中PLD是可程式邏輯器件,是作為一種通用積體電路生產的,他的邏輯功能按照用戶對器件編程來決定。...

PLD系列混凝土配料機是採用裝載機或皮帶輸送機上料的沙石配料裝置,能配三種以上的物料,與各類型的攪拌機和其他計量裝置配套使用,能組合成全自動和半自動的攪拌站,...

PLD空薄膜材料製備系統是具有薄膜質量高,膜層和基底互擴散小等特點,用於製備金屬膜及半導體薄膜等的系統。...

《PLD 與數字系統設計》是2005年西安電子科技大學出版社出版的圖書,作者是李輝。...... 《PLD 與數字系統設計》是2005年西安電子科技大學出版社出版的圖書,作者是李...

《PLD系統設計入門與實踐》是2016年7月國防工業出版社出版的圖書,作者是王建農、王鯤鵬、王偉。...

PLD晶片解密,又叫PLD單片機解密,PLD單片機破解,PLD晶片破解。單片機攻擊者藉助專用設備或者自製設備,利用單片機晶片設計上的漏洞或軟體缺陷,通過多種技術手段,就可以從...

(PLD劉波設計顧問(香港)有限公司創始人)編輯 鎖定 本詞條缺少名片圖,補充相關內容使詞條更完整,還能快速升級,趕緊來編輯吧!劉波設計顧問有限公司設計總監,建設部...

《PLD器件與EDA技術》是2000年北京廣播學院出版社出版的圖書,作者是李冬梅。本書可作為電子類、通信類、計算機類本科生的教學用書,也可供相關專業的師生和從事數字...

PLD800型混凝土配料機是一種與攪拌機配套使用的前台自動配料設備。它可根據用戶設計的混凝土配比自動完成砂、石、水泥等3-6種物料的配料程式。 ...

《PLD與CPLD數字電路設計》是2001年中國水利水電出版社出版的圖書,作者是許瑞麟。...... 《PLD與CPLD數字電路設計》是2001年中國水利水電出版社出版的圖書,作者是許...

1. 派力迪特種光催化氧化裝置(簡稱:PLD-光量子) .山東派力迪環保工程有限公司.2011-09-09[引用日期2012-10-29] 圖集 派力迪特種光催化氧化裝置(簡稱:PLD-光量...

《PLD在電子電路設計中的套用》是2007年清華大學出版社出版的圖書,作者是江國強。...... 《PLD在電子電路設計中的套用》是2007年清華大學出版社出版的圖書,作者是...

《數字系統設計與PLD套用》是2005年1月電子工業出版社出版的圖書,作者是臧春華。...... 《數字系統設計與PLD套用》是2005年1月電子工業出版社出版的圖書,作者是臧春...

CPLD(Complex Programmable Logic Device)是Complex PLD的簡稱,一種較PLD為複雜的邏輯元件。CPLD是一種用戶根據各自需要而自行構造邏輯功能的數字積體電路。其基本設計...

《PLD 與數字系統設計》是2005年西安電子科技大學出版社出版的圖書,作者是李輝。...... 《PLD 與數字系統設計》是2005年西安電子科技大學出版社出版的圖書,作者是李...

PLD與SOPC系統設計技術是由國防工業出版社出版的書籍,作者是何賡 ,在2006-01-01出版。...

可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,...

公司名稱: 保蘭德 外文名稱: POWERLAND(PLD) 總部地點: 德國 發起時間: 1970年 經營範圍: 高端皮具精品 創始人: 郭順元 ...

脈衝雷射沉積(Pulsed Laser Deposition,PLD),也被稱為脈衝雷射燒蝕(pulsed laser ablation,PLA),是一種利用雷射對物體進行轟擊,然後將轟擊出來的物質沉澱在不同的...

PLD誕生及簡單PLD發展階段二十世紀七十年代,熔絲編程的PROM(ProgrammableReadOnlyMemory)和PLA(ProgrammableLogicArray)的出現,標誌著PLD的誕生。可程式邏輯器件最早是...

139 0x8B PLD Partial Line Forward(部分行前移) 140 0x8C PLU Partial Line Backward(部分行後移) 141 0x8D RI Reverse Line Feed(逆向饋行) 142 0x8E...

PLD-R系列 站駕式 PLD 10R/15R/20R/30R適用場合:適合平整地面上的中短距離的托盤水平搬運, 結構小巧緊湊,特別適於在類似貨車內部這樣的狹小空間內作業。產品特點...