可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。

基本介紹

- 中文名:可程式邏輯器件

- 外文名:programmable logic device

- 簡稱: PLD

- 作用:通用積體電路

- 分類:固定邏輯器件和可程式邏輯器件

概念

發展歷史

分類

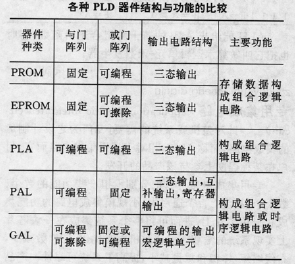

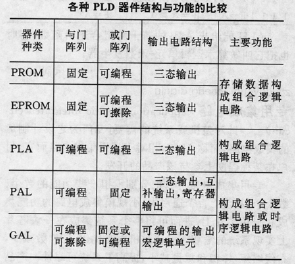

對比

可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。

可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,...

CPLD採用CMOS EPROM、EEPROM、快閃記憶體和SRAM等編程技術,從而構成了高密度、高速度和低功耗的可程式邏輯器件。...

《可程式邏輯器件原理套用》是2004年西安電子科技大學出版社出版的圖書,作者是朱明程。本書主要介紹可程式邏輯器的原理以及相關套用。...

大規模可程式邏輯器件(Programmable Logic Devices),是EDA得以實現的硬體基礎,通過編程,可靈活方便地構建和修改數字電子系統。可程式邏輯器件是積體電路技術發展的產物...

《可程式邏輯器件基礎》是2012年出版的圖書,作者是董海青。...... 《21世紀高職高專電子信息類實用規劃教材:可程式邏輯器件基礎》主要包括器件、工具、語言、單元電...

《可程式邏輯器件設計》是1997年3月出版的圖書,作者是黃均鼐。...... 《可程式邏輯器件設計》是1997年3月出版的圖書,作者是黃均鼐。書名 可程式邏輯器件設計 作...

《可程式邏輯器件設計及套用》在介紹Altera公司PLD器件的基礎上,介紹了開發PLD的完整注程;介紹了用於邏輯電路設計的硬體描述Verilog HDL語言;介紹了Altera公司的開發...

《可程式邏輯器件設計新思路》是發表在2003年第1期《微電子技術》上的一篇學術論文,作者是:劉達、龔建榮。...

可程式邏輯器件(programmaile lofic device)簡稱PLD,是可以根據需要由用戶自己編程來設定邏輯功能的大規模積體電路。自201世紀70年代間世以來,發展迅速,套用日益廣泛...

《可程式邏輯器件與EDA技術》是2014年清華大學出版社出版的圖書,作者是方易圓。本書可作為高等學校電子信息工程、通信工程、廣電通信與網路工程、雷達、計算機套用、...

《可程式邏輯器件設計項目教程》是機械工業出版社出版的書籍,作者是高銳。本書從實際套用角度出發,在企業工程實例和典型電子產品中精選出6個具有代表性的教學項。...

《可程式邏輯器件及EDA技術》是2008年東北大學出版社出版的圖書,作者是李景華。...... 《可程式邏輯器件及EDA技術》是2008年東北大學出版社出版的圖書,作者是李景華...

《可程式邏輯器件原理開發與套用》是2001年西安電子科技大學出版社出版的圖書,作者是趙曙光 / 郭萬有 / 楊頌華...

《可程式邏輯器件原理開發與套用第二版》是西安電子科技大學出版社2006年01月出版的圖書,作者是趙曙光。...

邏輯器件可分為兩大類 – 固定邏輯器件和可程式邏輯器件。正如其命名一樣,固定邏輯器件中的電路是永久性的,它們完成一種或一組功能 —— 一旦製造完成,就無法...

《可程式邏輯器件與VHDL設計》是電子工業出版社於2017年出版的圖書,作者是靳鴻。...... 《可程式邏輯器件與VHDL設計》是電子工業出版社於2017年出版的圖書,作者是...

《可程式邏輯器件套用實踐》是2008年7月份出版的圖書,作者是楊春玲。...... 《可程式邏輯器件套用實踐》是2008年7月份出版的圖書,作者是楊春玲。作者 楊春玲 等 I...

PAL(Programmable Array Logic)可程式陣列邏輯,是70年代末由MMI公司率先推出的一種低密度,一次性可程式邏輯器件,第一個具有典型實際意義的可程式邏輯器件(PLD-...

《Xilinx可程式邏輯器件設計與開發》是2011 年5月人民郵電出版社出版的圖書,作者是王春平、張曉華、趙翔。...

《ALTERA可程式邏輯器件及其套用》是1995年清華大學出版社出版的圖書,作者是劉寶琴、張芳蘭、田立生。...

《可程式邏輯器件與VHDL語言》是2005年科學出版社出版的圖書,作者是程雲長。...... 《套用型本科人才培養創新教材出版工程·電子信息類教材系列:可程式邏輯器件與VHDL...

《可程式邏輯器件及VHDL設計技術》是張昌凡著、華南理工出版社於2001年出版發行。...... 《可程式邏輯器件及VHDL設計技術》共有11章,其中包括:“可程式邏輯器件基礎...

《可程式邏輯器件開發軟體Quartus2》是2006年國防工業出版社出版的圖書。本書圍繞著PLD的設計這個主題,系統介紹了相關的基礎知識和工具軟體,給出了設計實例。...

全書共分11章,內容包括:可程式邏輯器件設計指南、可程式邏輯器件設計方法、VHDL高級設計技術、IP核設計技術、基於HDL的設計輸入、基於原理圖的設計輸入、設計綜合和...

《Xilinx可程式邏輯器件設計與開發(基礎篇)》是2011年人民郵電出版社出版的圖書,作者是王春平、張曉華、趙翔。...

可多次編程,可程式邏輯器件中的一類,另一類為OTP(One Time Programming,一次性可程式)...

《可程式邏輯器件與數字系統設計》是2003年機械工業出版社出版的圖書,作者是趙立民。...