非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非阻塞賦值允許其他的Verilog語句同時進行操作。

基本介紹

- 中文名:非阻塞賦值

- 外文名:nonblocking assignment

- 特點:允許其他的Verilog語句同時操作

- 操作費用:小於等於號(即<=)

- 使用場景:描述時序邏輯的always塊

- 套用學科:機械工程、儀器科學、計算機科學

非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非阻塞賦值允許其他的Verilog語句同時進行操作。

非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非...

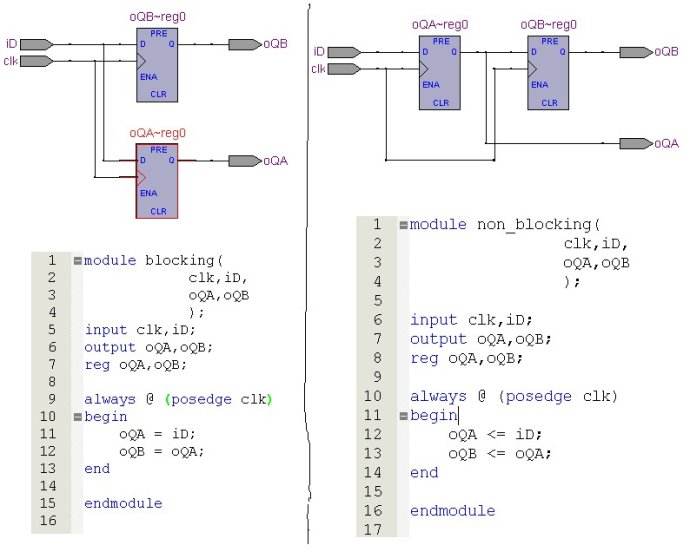

在Verilog HDL的概念中阻塞賦值操作符用等號(即=)表示。在賦值時先計算等號右手部分的值,這時賦值語句不允許任何別的Verilog語句的干擾,直到現行的賦值完成時刻,才...

時序邏輯器件的賦值語句採用非阻塞賦值“<=”,如上的Q〈= D; [1] 語法上,沒有關鍵字“assign”; 左側被賦值的數據類型必須是暫存器類型的變數(reg); 過...

對數據流的建模方式主要有連續賦值語句、阻塞賦值語句、非阻塞賦值語句等。 [1] 連續賦值實例 編輯 wire [3:0] Z, Preset, Clear; //線網說明...

在Verilog中,有兩種賦值運算,一種叫做阻塞賦值(blocking assignment),其運算符為=;另一種叫做非阻塞賦值(non-blocking assignment),其運算符為<=。在順序代碼塊中...

大多數Verilog事件是由動態事件佇列調度的,這些事件包括阻塞賦值、連續賦值、$dis—play命令、實例和原語的輸入變化以及它們的輸出更新、非阻塞賦值語句RHS的計算等。...

14.12 常見的對於非阻塞賦值的誤解小結思考題第15章 較複雜時序邏輯電路設計實踐概述小結思考題第16章 複雜時序邏輯電路設計實踐概述...

4.3.1阻塞賦值、非阻塞賦值和連續賦值674.3.2暫存器電路建模684.3.3組合邏輯建模704.3.4雙向連線埠與三態信號建模724.3.5mux建模734.3.6存儲器建模74...

10.6.1 進程的設計10.6.2 阻塞賦值與非阻塞賦值10.6.3 套用要點10.7 片記憶體儲器的使用10.7.1 片記憶體儲器10.7.2 設計舉例10.8 如何消除毛刺...

5.12.3阻塞和非阻塞賦值2885.12.4組合電路的非阻塞賦值2935.12.5具有清零功能的觸發器2935.13用Verilog代碼實現暫存器和計數器2955.13.1具有使能輸入的觸發器和...

另外,作為一種與普通計算機程式語言不同的硬體描述語言,它還具有一些獨特的語言要素,例如向量形式的線網和暫存器、過程中的非阻塞賦值等。總的來說,具備C語言的...

1.4.7存儲器1.4.8阻塞賦值和非阻塞賦值1.5層次化和參數化設計1.5.1層次化設計1.5.2參數化設計1.5.3generate結構第2章16位微程式控制計算機的設計...

4.3常用RTL級建模4.3.1非阻塞賦值、阻塞賦值、連續賦值4.3.2暫存器電路建模4.3.3組合邏輯建模4.3.4雙向連線埠與三態信號建模4.3.5mux建模4.3.6存儲器建模...

10.5 阻塞賦值與非阻塞賦值28810.6 FPGA設計中毛刺的消除292習題10294第11章 Verilog仿真與驗證29511.1 系統任務與系統函式29511.2 用戶自定義元件29911.2.1 ...

3.4.2 常用的過程語句用法3.4.2 過程中的阻塞賦值與非阻塞賦值3.4.3 基於過程塊的組合邏輯建模標準任務10 基於三態門的雙向連線埠設計3.5 三態門的原理及其套用...

6.3 賦值語句 1486.3.1 持續賦值與過程賦值 1486.3.2 阻塞賦值與非阻塞賦值 1496.4 條件語句 1516.4.1 if-else語句 1516.4.2 case語句 152...

二、“<=”非阻塞賦值174三、舉例說明174四、阻塞和非阻塞的使用要點179第五節模組層次化設計180一、結構層次化設計180二、模組劃分的技巧180...

第十四章 深入理解阻塞和非阻塞賦值 第十五章 較複雜時序邏輯電路設計實踐 第十六章 復時序邏輯電路設計實踐 第十七章 簡化的RISC CPU設計 第十八章 虛擬器...

9.4.4阻塞和非阻塞賦值9.4.5可綜合代碼設計對時鐘和復位的要求9.5小結第10章綜合以及布局布線最佳化10.1綜合級速度與面積最佳化設定10.2使用設計助手和最佳化顧問...

1.4.7存儲器1.4.8阻塞賦值和非阻塞賦值1.5層次化和參數化設計1.5.1層次化設計1.5.2參數化設計1.5.3generate結構第2章16位微程式控制計算機的設計...

4.2.3阻塞賦值與非阻塞賦值4.3VerilogHDL有限狀態機設計4.3.1Moore型狀態機和Mealy型狀態機的設計4.3.2VerilogHDL有限狀態機的不同設計方法...

4.1.5觸發器設計中的非阻塞賦值語句1094.1.6實驗內容1114.2暫存器實驗1114.2.1暫存器1124.2.2移位暫存器1134.2.3實驗內容1134.3計數器實驗115...

3 4 2 過程中的阻塞賦值與非阻塞賦值3 4 3 基於過程塊的組合邏輯建模標準任務10 基於三態門的雙向連線埠設計3 5 三態門的原理及其套用...

3.5.1 阻塞賦值與非阻塞賦值3.5.2 可綜合狀態機的寫法3.5.3 任務和函式3.6 Verilog HDL建模與調試技巧3.6.1 雙向連線埠3.6.2 輸入值不確定的組合邏輯電路...

10.4 過程 28610.5 阻塞賦值與非阻塞賦值 288習題10 292實驗與設計 29210-1 小數分頻 29210-2 如何在FPGA設計中消除毛刺 29410-3 消抖動電路 297 [1] ...

6.3 賦值語句 1636.3.1 持續賦值與過程賦值 1636.3.2 阻塞賦值與非阻塞賦值 1656.4 條件語句 1666.4.1 if-else語句 1666.4.2 case語句 168...

2.5.3 循環語句2.5.4 阻塞賦值和非阻塞賦值2.6 task和function說明語句2.6.1 任務(task)2.6.2 函式(function)2.6.3 任務和函式的異同2.7 編譯預處理...

8.7 推薦實驗 1938.7.1 使用阻塞賦值語句和非阻 [1] 塞賦值語句的移位暫存器 1938.7.2 BCD計數器的另一種編碼風格1948.7.3 FIFO快取器的另一種編碼...