通用陣列邏輯,英語縮寫GAL(genericarray logic)。在可程式陣列邏輯的基礎上強化修改而成的一種可程式邏輯器件。編程非常方便,且具有電可擦除功能,能多次編程、多次擦除。採用了輸出邏輯宏單元的設計,使得電路的邏輯設計更加靈活。

基本介紹

- 中文名:通用陣列邏輯

- 外文名:generic array logic

- 縮寫:GAL

- 發展:PAL

定義

優點

PAL和GAL基本結構比較

PAL和GAL基本結構比較

通用陣列邏輯,英語縮寫GAL(genericarray logic)。在可程式陣列邏輯的基礎上強化修改而成的一種可程式邏輯器件。編程非常方便,且具有電可擦除功能,能多次編程、多次擦除。採用了輸出邏輯宏單元的設計,使得電路的邏輯設計更加靈活。

PAL和GAL基本結構比較

PAL和GAL基本結構比較通用陣列邏輯,英語縮寫GAL(genericarray logic)。在可程式陣列邏輯的基礎上強化修改而成的一種可程式邏輯器件。編程非常方便,且具有電可擦除功能,能多次編程、多次...

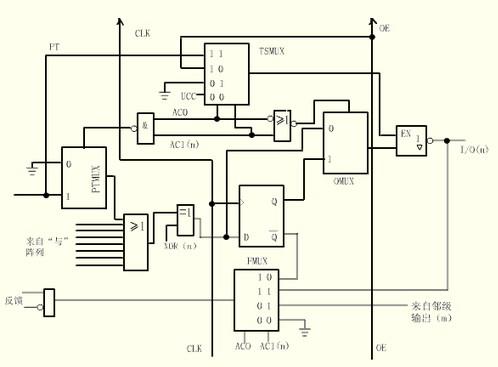

GAL是Lattice在PAL的基礎上設計出來的器件,即通用陣列邏輯器件。GAL首次在PLD上採用了EEPROM工藝,使得其具有電可擦除重複編程的特點,徹底解決了熔絲型可程式器件的...

《數字電路邏輯設計(第2版)》是2011年清華大學出版社出版的圖書,作者是朱正偉。...7.2.2可程式邏輯陣列PLA1967.2.3可程式陣列邏輯PAL1977.2.4通用陣列邏輯...

4.2.3 可程式陣列邏輯PAL. (218)4.2.4 通用陣列邏輯GAL. (221)4.3 高密度可程式邏輯器件... (228)4.3.1 複雜的可程式邏輯器件(CPLD) (229)...

6.10 通用陣列邏輯6.11 高密度可程式邏輯器件第七章 數字系統設計7.1 概述7.2 數字系統的描述7.3 基本數字系統設計7.4 簡易計算機設計...

6.3可程式邏輯器件6.3.1PLD概述6.3.2可程式唯讀存儲器6.3.3可程式邏輯陣列6.3.4可程式陣列邏輯6.3.5通用陣列邏輯6.4小結6.5習題與思考題...

6.3.5通用陣列邏輯GAL6.4小結6.5習題與思考題第7章高密度可程式器件7.1在系統可程式技術7.2ISP器件的結構與原理7.3在系統編程原理...

1.3 可程式陣列邏輯PAL1.3.1 PAL器件的基本結構1.3.2 PAL器件的輸出及反饋結構1.3.3 PAL器件實例介紹1.4 可程式通用陣列邏輯GAL...

7.2.1 可程式邏輯陣列7.2.2 可程式陣列邏輯與通用陣列邏輯7.3 PLD設計方法及步驟7.3.1 PLD器件的設計步驟7.3.2 可程式器件設計軟體簡介...

2.3 陣列邏輯電路212.3.1 唯讀存儲器(ROM)222.3.2 可程式序邏輯陣列(PLA)232.3.3 可程式序陣列邏輯(PAL)252.3.4 通用陣列邏輯(GAL)27...

2.3.3可程式序陣列邏輯(PAL)502.3.4通用陣列邏輯(GAL)512.3.5門陣列(GA)、宏單元陣列(MCA)、標準單元陣列(SCA)522.3.6可程式序門陣列(PGA)61...

第3章 通用陣列邏輯GAL實驗實驗八 門電路設計與實現實驗九 組合邏輯電路的設計與實現(一)實驗十 組合邏輯電路的設計與實現(二)實驗十一 可控計數器的設計與實現第...

PALASM是一種早期的硬體描述語言,主要是用來開發、撰寫能燒錄(program)至可程式陣列邏輯(PAL)[1]的可程式邏輯器件(PLD)內,PAL最早是由Monolithic記憶體公司(Monolithic...

3.1.2 可程式邏輯器件的分類3.1.3 可程式元件3.2 簡單的可程式邏輯器件3.2.2 可程式陣列邏輯器件3.2.3 可程式通用陣列邏輯器件...

7.3.4通用陣列邏輯GAL 7.4ispLSI系列CPLD 7.4.1概述 7.4.2ispLSI1000系列CPLD的結構特點 7.4.3ispLSICPLD的測試和編程特性 7.4.4ispLSI2000系列CPLD的結構...

PLD中文名是保蘭德,是義大利一家精品皮具製造商的品牌。同時在計算機中PLD是可程式邏輯器件,是作為一種通用積體電路生產的,他的邏輯功能按照用戶對器件編程來決定。...

12.3.3 集成RAM12.4 可程式邏輯器件概述12.4.1 PLD的發展12.4.2 PLD的分類和特點12.4.3 實現可程式的基本方法12.5 通用陣列邏輯GAL12.5.1 概述...

6.2 簡單的可程式邏輯器件(SPLD)6.2.1 PROM的PLD表示法6.2.2 可程式陣列邏輯器件(PAL)6.2.3 可程式通用陣列邏輯器件(GAL)6.3 複雜的可程式邏輯器件(CPLD...