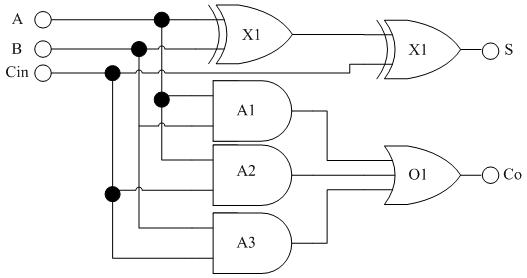

全加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯後做成多位全加器.

相關詞條

- 一位全加器

全加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯後做成...

- 全加器

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加並求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,並輸出本位加法進位。多個一位...

- 四位全加器

能實現四位二進制數全加的數字電路模組,稱之為四位全加器。...... 四位全加器半加器 能對兩個1位二進制數進行相加求和及進位的邏輯電路稱為半加器。或:只...

- 多位加法器

多位加法器是兩個多位數相加時每一位都是帶進位相加的,因而必須使用。...... 兩個多位數相加時每一位都是帶進位相加的,因而必須使用全加器。只要依次將低位的...

- 半加器

半加器電路是指對兩個輸入數據位相加,輸出一個結果位和進位,沒有進位輸入的加法器電路。 是實現兩個一位二進制數的加法運算電路。...

- 超前進位加法器

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法...

- 八位加法器

LS283的進位是逢16進1,而這兩個十二位的8421BCD碼相加時的進位是逢10進1,那么就要對加法器74LS283的二進制和數進行修正,即加上一個6(0110),讓其產生一個...

- 加法器

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用...

- 結構化建模

該實例用結構化建模方式進行一個兩位的全加器的設計,頂層模組Four_bit_FA調用了兩個一位的全加器FA_struct。在這裡,以前的設計模組FA_struct對頂層而言是一個現...

- 半加減電路

半加減電路,兩個二進制數(不考慮低一位的進位信號)相加,叫做半加;能夠實現半加操作的電路。...

- Xilinx FPGA數字電路設計

5.8 二位全加器的設計5.9 BCD七段顯示器解碼器的設計5.9.1 七段顯示器的基本架構5.9.2 七段顯示器解碼器的真值表5.9.3 布爾代數式...

- 串列二進制加法器

若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。PU、MCU及DSP等電子器件中的加法運算是最基礎、最常見的運算方法,常見加法器是位並行的,...

- 地址加法器

[1] 地址加法器加法器電路設計 該加法器設計採用全靜態CMOS電路,它具有很多優點...的加法器,結合加法器結構和XOR電路,再加之胞和位判斷電路,可以得到所需加法器...

- 組合邏輯電路

實現這一功能的邏輯電路叫全加器 [1] 。2.加法器實現多位二進制數相加的電路稱為加法器。根據進位方式不同,有串列進位加法器和超前進位加法器兩種 [1] 。...

- 半減法器

有了全加器之後,一個長度為四位元的加法就可以用四個全加器加以完成如圖6.1-3所示,若加法中的位元增多時,僅需要將全加器並接至最高位元即可[1] 。...

- 機器運算

1.全加器基本的加法單元稱為全加器,它要求三個輸入量:運算元Ai和Bi、低位傳來的進位Ci-1,並產生兩個輸出量:本位和Si、向高位的進位Ci。全加器的邏輯表達式...

一位全加器

一位全加器