Verilog HDL建模概述

在數字電路設計中,數字電路可簡單歸納為兩種要素:線和

器件。線是器件管腳之間的物理連線;器件也可簡單歸納為組合邏輯器件(如與或非門等)和時序邏輯器件(如暫存器、鎖存器、RAM等)。一個數字系統(硬體)就是多個器件通過一定的連線關係組合在一塊的。因此,Verilog HDL的建模實際上就是如何使用HDL語言對數字電路的兩種基本要素的特性及相互之間的關係進行描述的過程。

簡介

Verilog模型可以是實際電路不同級別的抽象,因此有多種不同的建模方法。其中最常用的建模方法有以下三種:

1)門級結構建模

2)行為描述建模

3)數據流建模

結構化的建模方式就是通過對電路結構的描述來建模,即通過對器件的調用(HDL概念稱為例化),並使用線網來連線各器件的描述方式。這裡的器件包括Verilog HDL的內置門如與門and,異或門xor等,也可以是用戶的一個設計。結構化的描述方式反映了一個設計的層次結構。

在實際套用中,實例化語句主用指後者,對內置門建議不採納,而用數據流或行為級方式對基本門電路的描述。連線埠佇列port_list列出了該模組通過哪些連線埠與外部模組通信。

建模示例

對一個數字系統的設計,我們採用的是

自頂向下的設計方式。可把系統劃分成幾個

功能模組,每個功能模組再劃分成下一層的子模組。每個模組的設計對應一個module,一個module設計成一個verilog HDL程式檔案。因此,對一個系統的頂層模組,可採用結構化的設計,即頂層模組分別調用了各個功能模組。

一位全加器

代碼:

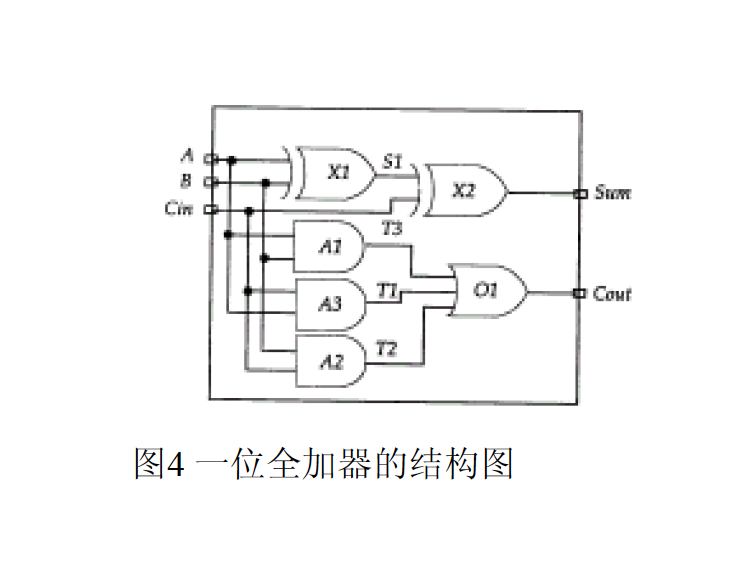

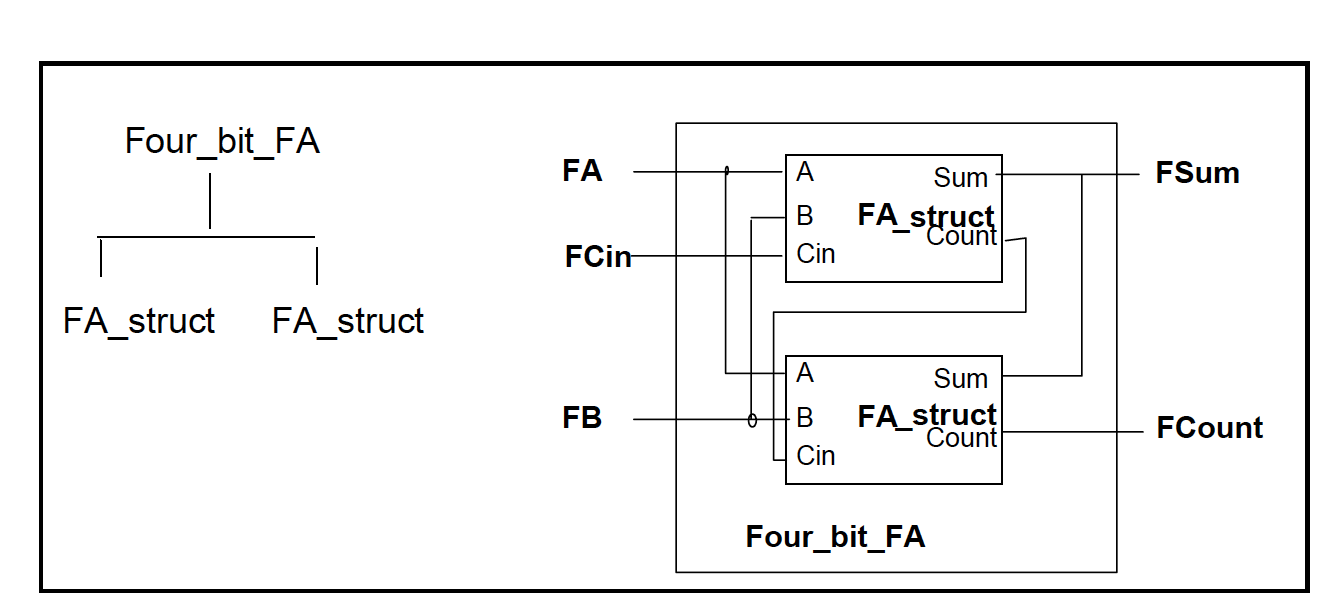

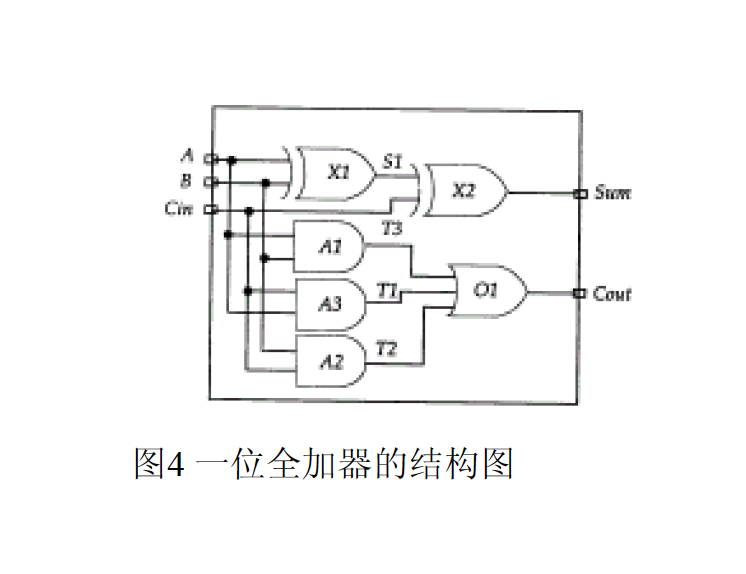

一位全加器的結構圖

一位全加器的結構圖module FA_struct (A, B, Cin, Sum, Count);input A;input B;input Cin;output Sum;output Count;wire S1, T1, T2, T3;// -- statements -- //xor x1 (S1, A, B);xor x2 (Sum, S1, Cin);and A1 (T3, A, B );and A2 (T2, B, Cin);and A3 (T1, A, Cin);or O1 (Cout, T1, T2, T3 );endmodule

該實例顯示了一個全加器由兩個異或門、三個與門、一個或門構成。S1、T1、T2、T3則是

門與門之間的連線。代碼顯示了用純結構的建模方式,其中xor、and、or是Verilog HDL內置的門器件。以xor x1 (S1, A, B)該例化語句為例:

xor表明調用一個內置的異或門,器件名稱xor,代碼實例化名x1(類似原理圖輸入方式)。括弧內的S1,A,B表明該器件管腳的實際連線線(信號)的名稱,其中A、B是輸入,S1是輸出。其他同。

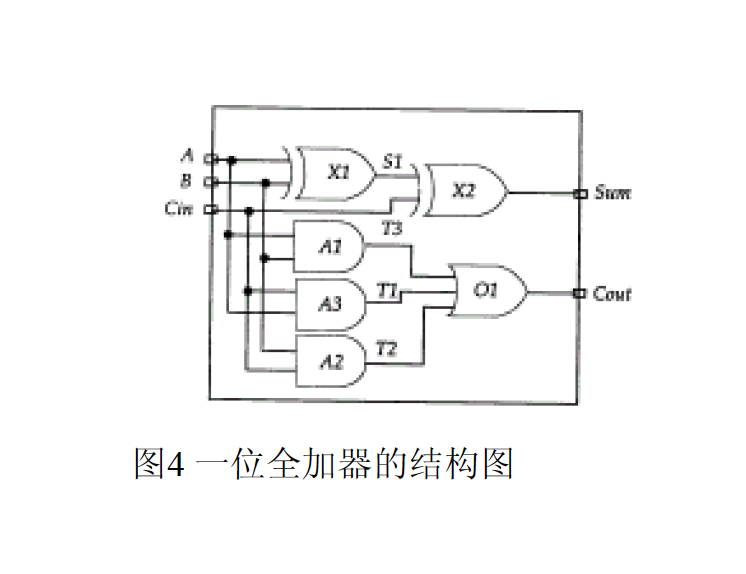

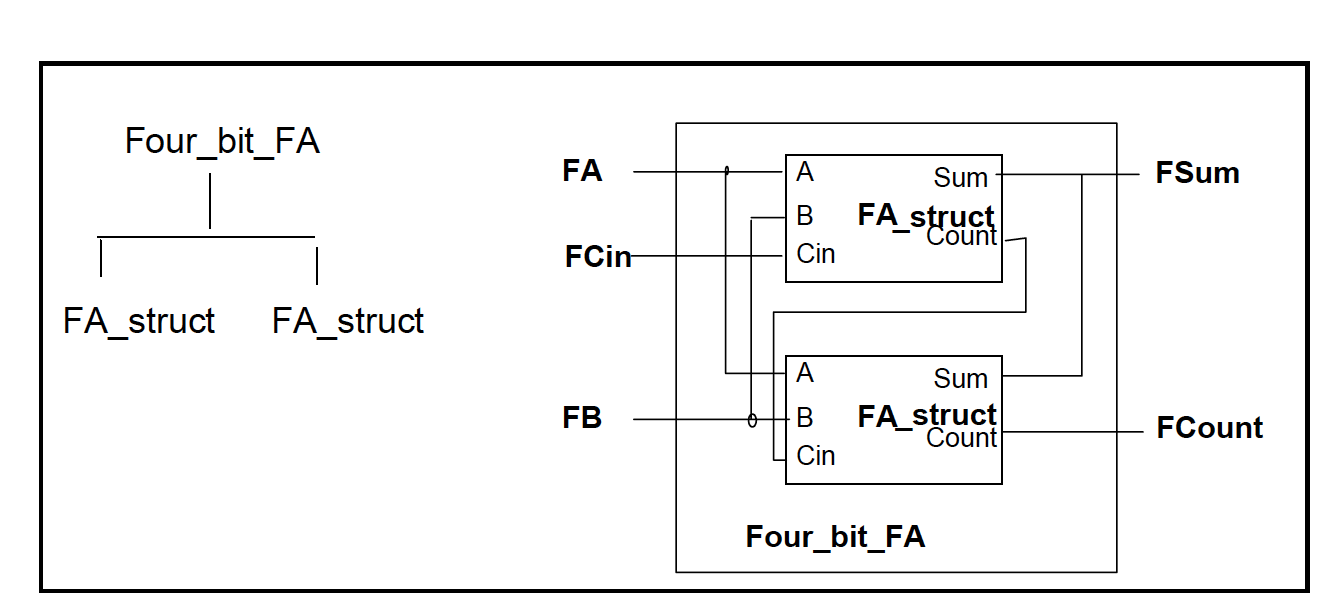

兩位的全加器

兩位的全加器可通過調用兩個一位的

全加器來實現。該設計的設計層次示意圖和結構圖如下:

兩位全加器的結構示意圖

兩位全加器的結構示意圖代碼:

module Four_bit_FA (FA, FB, FCin, FSum, FCout ) ;parameter SIZE = 2;input [SIZE:1] FA;input [SIZE:1] FB;input FCin;output [SIZE:1] FSum;output FCout;wire FTemp;FA_struct FA1(.A (FA[1]),.B (FB[1]),.Cin (FCin) ,.Sum (FSum[1]),.Cout (Ftemp));FA_struct FA2(.A (FA[2]),.B (FB[2]),.Cin (FTemp) ,.Sum (FSum[2]),.Cout (FCount ));endmodule

該實例用結構化建模方式進行一個兩位的全加器的設計,頂層模組Four_bit_FA調用了兩個一位的全加器FA_struct。在這裡,以前的設計模組FA_struct對頂層而言是一個現成的器件,頂層模組只要進行例化就可以了。

注意這裡的例化中,

連線埠映射(管腳的連線)採用名字關聯,如.A(FA[2]),其中.A表示調用器件的管腳A,括弧中的信號表示接到該管腳A的電路中的具體信號。wire保留字表明信號Ftemp是屬線網類型)。

另外,在設計中,儘量考慮

參數化的問題。器件的連線埠映射必須採用名字關聯。

一位全加器的結構圖

一位全加器的結構圖 兩位全加器的結構示意圖

兩位全加器的結構示意圖