基本介紹

- 中文名:arm cortex a5

- 外文名:arm cortex a5

- 內容:Cortex-A系列處理器

- 優點:高性能低成本並且支持雙核技術

簡介

性能規格參數

| ARM Cortex-A5 性能、功耗和面積 | ||

|---|---|---|

工藝類型/額定電壓 | 低泄漏,1.1V | 性能,1.0V |

性能或頻率最佳化 | 頻率 | 頻率 |

頻率 | 530~600 MHz | >1GHz |

面積,不包括 RAM/高速快取 | 0.27mm2 | 0.27mm2 |

面積(帶 16K/16K 高速快取) | 0.53mm2 | 0.53mm2 |

面積(帶 16K/16K 高速快取 + NEON) | 0.68mm2 | 0.68mm2 |

動態功耗 | 0.12 mW/MHz | <0.08mW/MHz |

能效 | 13 DMIPS/mW | >20 DMIPS/mW |

| Cortex-A5 | |

|---|---|

Dhrystone 性能 | 每個核心 1.57 DMIPS/MHz |

多核 | 1-4 個核心 還提供單核版本 |

ISA 支持 | |

ARMv7 記憶體管理單元 | |

調試和跟蹤 | CoreSight™ DK-A5 |

| Cortex-A5 主要功能 | |

|---|---|

Thumb-2 技術 | 可為傳統 ARM 代碼提供最高性能,對於存儲指令占用的記憶體,最多可節省 30% 的空間。 |

TrustZone® 技術 | 確保全全套用的可靠實現,適合從數字著作權管理到電子支付等套用。獲得技術和行業合作夥伴的廣泛支持。 |

NEON 媒體處理引擎 (MPE) | 可選 Cortex-A5 NEON 可提供 Cortex-A5 浮點單元的性能和功能以及 ARM NEON 高級 SIMD 指令集實現,以便進一步提高媒體和信號處理功能的速度。 MPE 擴展 Cortex-A5 浮點單元 (FPU),提供一個附加暫存器集,在 8 位、16 位和 32 位整型以及 32 位浮點數據類型的基礎上支持一組豐富的 SIMD 操作。 |

浮點單元 (FPU) | |

Jazelle RCT 和 DBX 技術 | |

可配置 L1 高速快取 | 可在 4-64K 範圍內單獨配置功率最佳化的 L1 指令和數據高速快取。 提供了ARM SRAM 的最佳化實例。 |

高性能AXI匯流排 | |

先進的多核技術 | |

偵測控制單元 (SCU) | |

加速器一致性連線埠 (ACP) | SCU 上的此 AMBA® 3 AXI™ 兼容的輔助接口為各種系統主機提供了一個互連點,出於總體系統性能、功耗或軟體簡化的原因,這些接口更易於直接連線 Cortex-A5 MPCore 處理器。 該接口可用作標準的 AMBA 3 AXI 輔助接口,它支持所有標準讀寫事務,而對連線的組件沒有任何其他一致性要求。不過,針對一致的記憶體區域的任何讀事務都會與 SCU 互動,以測試所需信息是否已存儲在處理器的 L1 高速快取內。如果存儲在其中,則會將其直接返回到請求組件。如果未存儲在 L1 高速快取中,則在最後轉發到主記憶體之前還有機會存儲在 L2 高速快取中。 對於針對任何一致的記憶體區域的寫事務,在將寫入數據轉發到記憶體系統之前,SCU 會強制其保持一致性。此外,此事務還可分配到 L2 高速快取,從而消除直接寫入對晶片外記憶體產生的功率和性能影響 |

通用中斷控制器 (GIC) | 實現最近標準化的、基於架構的 ARM 中斷控制器後,GIC 提供了一種強大且靈活的方式,用來進行處理器間通信以及路由系統中斷和確定其優先次序。在軟體控制下,最多支持 224 次獨立中斷,每次中斷均可在 CPU 之間分布,經過硬體確定優先權,然後在作業系統和 TrustZone 軟體管理層之間路由。藉助半虛擬化管理器,此路由靈活性以及支持虛擬化作業系統中斷這一特性賦予了增強解決方案功能所需的其中一個主要功能。 |

主要特點

概述

套用

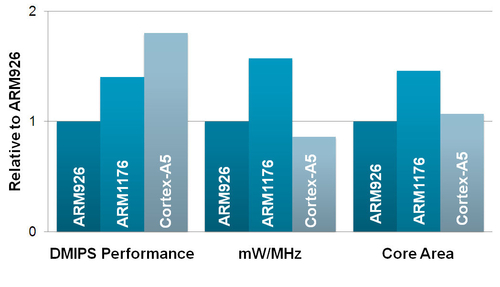

面積和能效

功耗對比圖

功耗對比圖