定義 ARM的Jazelle技術使Java加速得到比基於軟體的Java

虛擬機 (JVM)高得多的性能,和同等的非Java加速核相比功耗降低80%。CPU功能上增加DSP

指令集 提供增強的16位和32位算術運算能力,提高了性能和靈活性。ARM還提供兩個前沿特性來輔助帶深嵌入處理器的高集成SoC器件的調試,它們是嵌入式ICE-RT邏輯和嵌入式跟蹤宏核(ETMS)系列。

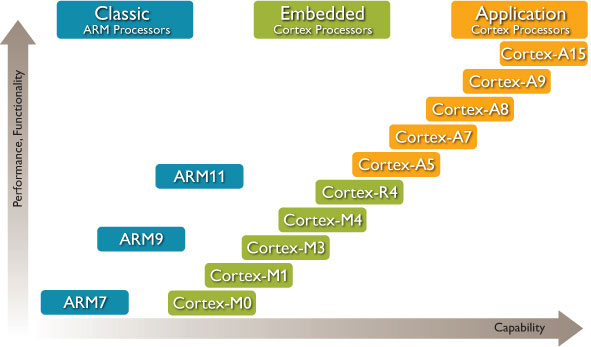

arm處理器階梯圖 (概述圖片來源:)

特點 ARM處理器的三大特點是:耗電少功能強、16位/32位雙

指令集 和合作夥伴眾多。

1、體積小、低功耗、低成本、高性能;

2、支持Thumb(16位)/ARM(32位)雙指令集,能很好的兼容8位/16位器件;

4、大多數數據操作都在暫存器中完成;

5、定址方式靈活簡單,執行效率高;

體系結構 1 CISC(Complex Instruction Set Computer,複雜

指令集計算機 )

在CISC

指令集 的各種指令中,大約有20%的指令會被反覆使用,占整個程式代碼的80%。而餘下的指令卻不經常使用,在程式設計中只占20%。

2 RISC(Reduced Instruction Set Computer,

精簡指令集計算機 )

RISC結構優先選取使用頻最高的簡單指令,避免複雜指令;將

指令長度 固定,

指令格式 和定址方式種類減少;以控制邏輯為主,不用或少用微碼控制等

RISC體系結構應具有如下特點:

1 採用固定長度的指令格式,指令歸整、簡單、基本定址方式有2~3種。

2 使用單周期指令,便於流水線操作執行。

3 大量使用

暫存器 ,數據處理指令只對暫存器進行操作,只有載入/存儲指令可以訪問

存儲器 ,以提高指令的執行效率。

除此以外,ARM

體系結構 還採用了一些特別的技術,在保證高性能的前提下儘量縮小晶片的面積,並降低功耗:

4 所有的指令都可根據前面的執行結果決定是否被執行,從而提高指令的執行效率。

5 可用載入/存儲指令批量傳輸數據,以提高數據的

傳輸效率 。

6 可在一條數據處理指令中同時完成邏輯處理和移位處理。

7 在循環處理中使用地址的自動增減來提高運行效率。

暫存器結構

ARM處理器共有37個暫存器,被分為若干個組(BANK),這些暫存器包括:

2 6個

狀態暫存器 ,用以標識CPU的工作狀態及程式的運行狀態,均為32位,只使用了其中的一部分。

指令結構

ARM微處理器的在較新的

體系結構 中支持兩種

指令集 :ARM指令集和Thumb指令集。其中,ARM指令為32位的長度,Thumb指令為16位長度。Thumb指令集為ARM指令集的功能子集,但與等價的ARM代碼相比較,可節省30%~40%以上的存儲空間,同時具備32位代碼的所有優點。

體系結構擴充

當前ARM體系結構的擴充包括:

·DSP DSP套用的算術運算指令集;

·Jazeller 允許直接執行Java

位元組碼 。

ARM處理器系列提供的解決方案有:

主要模式 處理器工作模式 說明

用戶模式(usr) ARM處理器正常的程式

執行狀態 系統模式(sys) 運行具有特權的作業系統任務

快中斷模式(fiq) 支持高速數據傳輸或通道處理

管理模式(svc) 作業系統保護模式

數據訪問終止模式(abt) 用於

虛擬存儲器 及存儲器保護

未定義指令終止模式(und) 支持硬體

協處理器 的軟體仿真

除用戶模式外,其餘6種模式稱為非用戶模式或特權模式;用戶模式和系統模式之外的5種模式稱為異常模式。ARM處理器的運行模式可以通過軟體改變,也可以通過

外部中斷 或

異常處理 改變。

歷史發展 1978年12月5日,物理學家赫爾曼·豪澤(Hermann Hauser)和工程師Chris Curry,在英國劍橋創辦了CPU公司(Cambridge Processing Unit),主要業務是為當地市場供應電子設備。1979年,CPU公司改名為Acorn公司。

起初,Acorn公司打算使用

摩托羅拉 公司的16位晶片,但是發現這種晶片太慢也太貴。"一台售價500英鎊的機器,不可能使用價格100英鎊的CPU!"他們轉而向Intel公司索要80286晶片的設計資料,但是遭到拒絕,於是被迫自行研發。

1985年,Roger Wilson和Steve Furber設計了他們自己的第一代32位、6M Hz的處理器,用它做出了一台RISC

指令集 的計算機,簡稱ARM(Acorn RISC Machine)。這就是ARM這個名字的由來。

Roger Wilson和Steve Furber RISC 的全稱是"

精簡指令集計算機 "(reduced instruction set computer),它支持的指令比較簡單,所以功耗小、價格便宜,特別適合移動設備。早期使用ARM晶片的典型設備,就是蘋果公司的牛頓PDA。

20世紀80年代後期,ARM很快開發成Acorn的台式機產品,形成英國的計算機教育基礎。

1990年11月27日,Acorn公司正式改組為ARM計算機公司。蘋果公司出資150萬英鎊,晶片廠商VLSI出資25萬英鎊,Acorn本身則以150萬英鎊的智慧財產權和12名工程師入股。公司的辦公地點非常簡陋,就是一個穀倉。20世紀90年代,ARM 32位嵌入式RISC(Reduced lnstruction Set Computer)處理器擴展到世界範圍,占據了低功耗、低成本和高性能的

嵌入式系統 套用領域的領先地位。ARM公司既不生產晶片也不銷售晶片,它只出售晶片技術授權。

在中國 ARM公司中國總部設立在上海,執行中國地區所有的產品業務和售後支持。其中在深圳設有辦事處,專門處理ARM相關技術問題。

ARM在中國主要從事ARM IP核心方面的工作,對於 ARM軟體工具,包括DS-5,RVDS,MDK-ARM等則不直接進行銷售,由其中國區代理商米爾科技作為渠道分銷商,負責銷售開發工具和客戶服務。

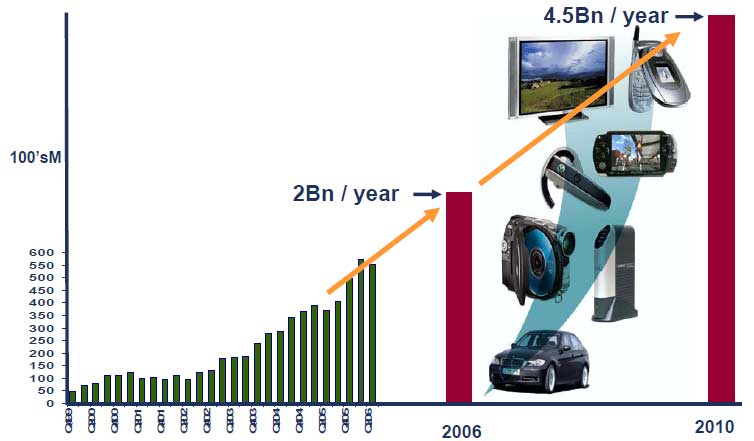

市場前景 微軟公司(2011年)宣布,下一版Windows將正式支持ARM處理器。這是計算機工業發展歷史上的一件大事,標識著x86處理器的主導地位發生動搖。在移動設備市場,ARM處理器的市場份額超過90%;在

伺服器 市場,2011年就會有2.5GHz的伺服器上市;在桌面電腦市場,又有了微軟的支持。ARM成為主流,恐怕指日可待。難怪有人驚呼,Intel公司將被擊敗!ARM微處理器核技術廣泛套用於攜帶型通信產品、手持運算、多媒體和嵌入式解決方案等領域,已成為RISC的標準。

arm處理器 與這場轟轟烈烈的變革相比,它的主角ARM公司卻沒有受到太多的關注,顯得不太起眼。這家遠離矽谷、位於劍橋大學的英國公司,到底是怎么走到打開市場的,居然能將晶片巨人Intel拉下馬?

展望未來,即使Intel成功地實施了Atom戰略,將x86晶片的功耗和價格大大降低,它與ARM競爭也將非常吃力。因為ARM的商業模式是開放的,任何廠商都可以購買授權,所以未來並不是Intel vs. ARM,而是Intel vs. 世界上所有其他半導體公司。那樣的話,Intel的勝算能有多少呢?

2012年10月29日AMD做出了一個震驚業界的宣布:AMD將會設計基於64-bit ARM架構的處理器,首先從雲和數據中心伺服器領域開始。AMD、ARM在伺服器領域的合作已經得到了戴爾、惠普兩大伺服器廠商,以及伺服器系統廠商RedHat的鼎力支持,新的生態系統已具雛形,AMD能否藉此東山再起?

AMD的首批ARM處理器於2014年問世,仍將披掛Opteron皓龍品牌。這種64位的多核心SoC會針對數據中心中份額最大的密集型高能效伺服器進行最佳化,提供現代計算體驗,並整合收購而來的SeaMicro Freedom超級計算光纖互聯技術。

系列產品 ARM7系列 ARM9系列 ARM9E系列 ARM10E系列

SecurCore系列 Intel的StrongARM ARM11系列 Intel的Xscale

其中,ARM7、ARM9、ARM9E和ARM10為4個通用處理器系列,每一個系列提供一套相對獨特的性能來滿足不同套用領域的需求。SecurCore系列專門為安全要求較高的套用而設計。

Axxia 4500通信處理器基於採用28納米工藝的ARM 4核Cortex-A15處理器,並搭載ARM全新CoreLink CCN-504高速快取一致性互連技術,實現安全低功耗和最佳性能。

ARM公司在經典處理器ARM11以後的產品改用

Cortex 命名,並分成A、R和M三類,旨在為各種不同的市場提供服務。

ARM核心

家族

架構

核心

特色

套用

ARM1

ARMv1

ARM1

無

ARM2

ARMv2

ARM2

Architecture 2 加入了MUL(乘法)指令

無

4 MIPS @ 8MHz

Acorn Archimedes,Chessmachine

ARMv2a

ARM250

Integrated (完整的)MEMC (MMU),圖像與IO處理器。Architecture 2a 加入了SWP和SWPB(置換)指令。

無,MEMC1a

7 MIPS@ 12MHz

Acorn Archimedes

ARM3

ARMv2a

ARM2a

首次在ARM架構上使用處理器高速快取

均為4K

12 MIPS @ 25MHz

Acorn Archimedes

ARM6

ARMv3

ARM610

v3 架構首創支援定址32位的記憶體(針對26位)

均為4K

28 MIPS @ 33MHz

ARM7TDMI

ARMv4T

ARM7TDMI(-S)

三級流水線

無

15 MIPS @ 16.8 MHz

ARM710T

均為8KB, MMU

36 MIPS @ 40 MHz

Acorn Risc PC 700,Psion 5 series,Apple eMate 300

ARM720T

均為8KB, MMU

60 MIPS @ 59.8 MHz

Zipit

ARM740T

MPU

ARMv5TEJ

ARM7EJ-S

Jazelle DBX

無

ARM9TDMI

ARMv4T

ARM9TDMI

五級流水線

無

ARM920T

16KB/16KB, MMU

200 MIPS @ 180 MHz

ARM922T

8KB/8KB, MMU

ARM940T

4KB/4KB, MPU

ARM9E

ARMv5TE

ARM946E-S

可變動,tightly coupled memories, MPU

ARM966E-S

無高速快取,TCMs

ST Micro STR91xF,包含Ethernet [2]

ARM968E-S

無高速快取,TCMs

ARMv5TEJ

ARM926EJ-S

Jazelle DBX

可變動,TCMs, MMU

220 MIPS @ 200 MHz

ARMv5TE

ARM996HS

無振盪器處理器

無高速快取,TCMs, MPU

ARM10E

ARMv5TE

ARM1020E

(VFP),六級流水線

32KB/32KB, MMU

ARM1022E

(VFP)

16KB/16KB, MMU

ARMv5TE

ARM1026EJ-S

Jazelle DBX

可變動,MMU or MPU

ARMv5TE

80200/IOP310/IOP315

I/O處理器

80219

400/600MHz

ThecusN2100

IOP321

Iyonix

IOP33x

IOP34x

1-2核,RAID加速器

32K/32K L1, 512K L2, MMU

PXA210/PXA250

套用處理器,七級流水線

ZaurusSL-5600

PXA255

32KB/32KB, MMU

PXA26x

可達 400 MHz

PXA27x

800 MIPS 624 MHz

HTC Universal, ZaurusSL-C1000,3000,3100,3200, Dell Aximx30, x50,和 x51 系列

PXA800(E)F

Monahans

1000 MIPS 1.25 GHz

PXA900

Blackberry 8700, Blackberry Pearl (8100)

IXC1100

Control Plane Processor

IXP2400/IXP2800

IXP2850

IXP2325/IXP2350

IXP42x

NSLU2

IXP460/IXP465

ARM11

ARMv6

ARM1136J(F)-S

SIMD, Jazelle DBX, (VFP),八級流水線

可變動,MMU

從 350 MHz 到1 GHz

ARMv6T2

ARM1156T2(F)-S

SIMD, Thumb-2, (VFP),九級流水線

可變動,MPU

ARMv6KZ

ARM1176JZ(F)-S

SIMD, Jazelle DBX, (VFP)

可變動,MMU+TrustZone

ARMv6K

ARM11 MPCore

1-4核對稱多處理器,SIMD, Jazelle DBX, (VFP)

可變動,MMU

Cortex

ARMv7-A

Cortex-A8

Application profile, VFP, NEON, Jazelle RCT, Thumb-2, 13-stage pipeline

可變動 (L1+L2), MMU+TrustZone

up to 2000(2.0 DMIPS/MHz 從600 MHz到超過1 GHz的速度)

Texas Instruments OMAP3

ARMv7-R

Cortex-R4(F)

Embedded profile, (FPU)

可變動高速快取,MMU可選配

600 DMIPS

ARMv7-M

Cortex-M3

Microcontroller profile

無高速快取,(MPU)

120 DMIPS @ 100MHz

Luminary Micro[3]微控制器家族

新款ARMv8架構ARMCortex-A50處理器系列產品,進一步擴大ARM在高性能與低功耗領域的領先地位。該系列率先推出的是Cortex-A53與Cortex-A57處理器以及最新節能64位處理技術與現有32位處理技術的擴展升級。該處理器系列的可擴展性使ARM的合作夥伴能夠針對智慧型手機、高性能伺服器等各類不同市場需求開發系統級晶片(SoC)。

ARMCortex-A50處理器系列:

提供Cortex-A57與Cortex-A53兩款處理器,可選配密碼編譯加速器,為驗證軟體提高10倍的運行速度與ARMMali圖形處理器系列互用,適用於圖形處理器計算套用具有AMBA系統一致性,與CCI-400、CCN-504等ARMCoreLink快取一致性結構組件達成多核心快取一致性。

ARMCortex-A57處理器:

最先進、單執行緒性能最高的ARM套用處理器能提升,以滿足供智慧型手機從內容消費設備轉型為內容生產設備的需求,並在相同功耗下實現最高可達現有超級手機三倍的性能計算能力可相當於傳統PC,但僅需移動設備的功耗成本即可運行,無論企業用戶或普通消費者均可享受低成本與低耗能針對高性能企業套用提高了產品可靠度與可擴展性。

ARMCortex-A53處理器:

史上效率最高的ARM套用處理器,使用體驗相當於當前的超級手機,但功耗僅需其四分之一結合可靠性特點,可擴展數據平面(dataplane)套用可將每毫瓦及每平方毫米性能發揮到極致針對個別執行緒計算應用程式進行了傳輸處理最佳化Cortex-A53處理器結合Cortex-A57及ARM的big.LITTLE處理技術,能使平台擁有最大的性能範圍,同時大幅減少功耗。

設計檔案 設計檔案講求精簡又快速的設計方式,整體電路化卻又不採用

微碼 ,就像早期使用在

Acorn 微電腦的8位6502處理器。

讀取/儲存 架構不支援地址不對齊記憶體存取(ARMv6核心現已支援)正交

指令集 (任意存取指令可以任意的

定址方式 存取數據Orthogonal instruction set)大量的16 × 32-bit 暫存器陣列(register file)固定的32 bits

操作碼 (opcode)長度,降低編碼數量所產生的耗費,減輕解碼和流水線化的負擔。大多均為一個CPU周期執行。為了補強這種簡單的設計方式,相較於同時期的處理器如

Intel 80286 和Motorola 68020,還多加了一些特殊設計:

大部分指令可以條件式地執行,降低在分支時產生的負重,彌補

分支預測 器(branch predictor)的不足。算數指令只會在要求時更改條件編碼(condition code)32-bit筒型位移器(barrel shifter)可用來執行大部分的算數指令和定址計算而不會損失效能強大的索引

定址模式 (addressing mode)精簡但快速的雙優先權中斷子系統,具有可切換的

暫存器 組有個附加在ARM設計中好玩的東西,就是使用一個4-bit

條件編碼 在每個指令前頭,表示每支指令的執行是否為有條件式的

這大大的減低了在記憶體存取指令時用到的編碼位,換句話說,它避免在對小型敘述如if做分支指令。有個標準的範例引用

歐幾里德 的

最大公因子 算法:

在C程式語言中,循環為:

int gcd (int i, int j)

{

while (i != j) if (i > j) i -= j; else j -= i; return i;

}

loop CMP Ri, Rj ;

設定條件為 "NE"(不等於) if (i != j) ; "GT"(大於) if (i > j), ; or "LT"(小於) if (i < j) SUBGT Ri, Ri, Rj ; 若 "GT"(大於), i = i-j; SUBLT Rj, Rj, Ri ; 若 "LT"(小於), j = j-i; BNE loop ; 若 "NE"(不等於),則繼續迴圈這避開了then和else子句之間的分支。

另一項

指令集 的特色是,能將位移(shift)和迴轉(rotate)等功能並成"資料處理"型的指令(算數、邏輯、和

暫存器 之間的搬移),因此舉例來說,一個C語言的敘述

a += (j << 2);在ARM之下,可簡化成只需一個word和一個cycle即可完成的指令

ADD Ra, Ra, Rj, LSL #2這結果可讓一般的ARM程式變得更加緊密,而不需經常使用記憶體存取,流水線也可以更有效地使用。即使在ARM以一般認定為慢速的速度下執行,與更複雜的CPU設計相比它仍能執行得不錯。

ARM處理器還有一些在其他RISC的架構所不常見到的特色,例如PC-相對定址(的確在ARM上PC為16個

暫存器 的其中一個)以及 前遞加或後遞加的定址模式。

另外一些注意事項是 ARM 處理器會隨著時間,不斷地增加它的

指令集 。某些早期的 ARM 處理器(比ARM7TDMI更早),譬如可能並未具備指令可以讀取兩 Bytes 的數量,因此,嚴格來講,對這些處理器產生程式碼時,就不可能處理如 C 語言物件中使用 "volatile short" 的資料型態。

ARM7 和大多數較早的設計具備三階段的流水線化(Pipeline):提取指令、解碼,並執行。較高效能的設計,如 ARM9,則有五階段的流水線化。提高效能的額外方式,包含一顆較快的

加法器 ,和更廣的分支預測邏輯線路。

這個架構使用“

協處理器 ”提供一種非侵入式的方法來延伸指令集,可透過軟體下 MCR、MRC、MRRC和MCRR 等指令來對協處理器定址。協處理器空間邏輯上通常分成16個協處理器,編號分別從 0 至 15 ,而第15號協處理器(CP15)是保留用作某些常用的控制功能,像是使用高速快取和記憶管理單元運算(若包含於處理器時)。

在 ARM 架構的機器中,周邊裝置連線處理器的方式,通常透過將裝置的實體

暫存器 對應到 ARM 的記憶體空間、協處理器空間,或是連線到另外依序接上處理器的裝置(如匯流排)。協處理器的存取延遲較低,所以有些周邊裝置(例如

XScale 中斷控制器)會設計成可透過不同方式存取(透過記憶體和協處理器)。

Thumb

較新的ARM處理器有一種16-bit指令模式,叫做Thumb,也許跟每個條件式執行指令均耗用4位的情形有關。在Thumb模式下,較小的opcode有更少的功能性。例如,只有分支可以是條件式的,且許多opcode無法存取所有CPU的暫存器。然而,較短的opcode提供整體更佳的編碼密度(註:意指程式碼在記憶體中占的空間),即使有些運算需要更多的指令。特別在記憶體埠或匯流排寬度限制在32 以下的情形時,更短的Thumb opcode能更有效地使用有限的

記憶體頻寬 ,因而提供比32位程式碼更佳的效能。典型的嵌入式硬體僅具有較小的32-bit datapath定址範圍以及其他更窄的16 bits定址(例如

Game Boy Advance )。在這種情形下,通常可行的方案是編譯成 Thumb 程式碼,並自行最佳化一些使用(非Thumb)32位

指令集 的CPU相關程式區,因而能將它們置入受限的32-bit匯流排寬度的記憶體中。

首顆具備 Thumb 技術的處理器是 ARM7TDMI。所有 ARM9 和後來的家族,包括

XScale 都納入了 Thumb 技術。

Jazelle

ARM 還開發出一項技術,Jazelle DBX (Direct Bytecode eXecution),允許它們在某些架構的硬體上加速執行Java bytecode,就如其他執行模式般,當呼叫一些無法支援bytecodes的特殊軟體時,能提供某些bytecodes的加速執行。它能在現存的ARM與Thumb模式之間互相執行。

首顆具備Jazelle技術的處理器是

ARM926EJ-S :Jazelle以一個英文字母'J'標示於CPU名稱中。它用來讓手機製造商能夠加速執行

Java ME 的遊戲和套用程式,也因此促使了這項技術不斷地開發。

Thumb-2

Thumb-2 技術首見於

ARM1156 核心 ,並於2003年發表。Thumb-2 擴充了受限的 16-bit Thumb

指令集 ,以額外的 32-bit 指令讓指令集的使用更廣泛。因此 Thumb-2 的預期目標是要達到近乎 Thumb 的編碼密度,但能表現出近乎 ARM 指令集在 32-bit 記憶體下的效能。

Thumb-2也從 ARM 和 Thumb 指令集中派生出多種指令,包含位欄(bit-field)操作、分支建表(table branches),和條件執行等功能。

Thumb Execution Environment (ThumbEE)

ThumbEE ,也就是所謂的

Thumb-2EE ,,業界稱為Jazelle RCT技術,於2005年發表,首見於

Cortex-A8 處理器。ThumbEE 提供從 Thumb-2 而來的一些擴充性,在所處的

執行環境 (Execution Environment)下,使得

指令集 能特別適用於執行階段(Runtime)的編碼產生(例如即時編譯)。Thumb-2EE 是專為一些語言如

Limbo 、Java、

C# 、

Perl 和

Python ,並能讓

即時編譯器 能夠輸出更小的編解碼卻不會影響到效能。

ThumbEE 所提供的新功能,包括在每次存取指令時自動檢查是否有無效指標,以及一種可以執行陣列範圍檢查的指令,並能夠分支到分類器(handlers),其包含一小部份經常呼叫的編碼,通常用於高階語言功能的實作,例如對一個新物件做記憶體配置。

進階 SIMD (NEON)

進階 SIMD 延伸集,業界稱為

NEON 技術,它是一個結合 64 和 128 bit 的

SIMD (Single Instruction Multiple Data 單指令多重數據)

指令集 ,其針對多媒體和訊號處理程式具備標準化加速的能力。NEON 可以在 10 MHz 的 CPU 上執行 MP3 音效解碼,且可以執行 13 MHz 頻率以下的

GSM AMR (Adaptive Multi-Rate) 語音編碼。NEON具有一組廣泛的指令集、各自的

暫存器 陣列,以及獨立執行的硬體。NEON 支援 8-, 16-, 32- 和 64-bit 的整數及單精度浮點數據,並以

SIMD 的方式運算,執行圖形和遊戲處理中關於語音/視訊的部分。SIMD 在 向量超級處理機 中是個決定性的要素,它具備同時多項處理功能。在 NEON 技術中,SIMD 最高可支援到同時 16 個運算。

VFP

VFP 是在協同處理器針對ARM架構的衍生技術。它提供低成本的單精度和倍精度

浮點運算 能力,並完全相容於ANSI/IEEE Std 754-1985 二進制浮點算數標準。VFP 提供大多數適用於浮點運算的套用,例如PDA、智慧手機、語音壓縮與解壓、3D圖像以及數位音效、印表機、機上盒,和汽車套用等。VFP 架構也支援

SIMD (單指令多重數據)平行化的短向量指令執行。這在圖像和訊號處理等套用上,非常有助於降低編碼大小並增加輸出效率。

在ARM-based處理器中,其他可見的浮點、或 SIMD 的協同處理器還包括了 FPA, FPE, iwMMXt。他們提供類似 VFP 的功能但在

opcode 層面上來說並不具有相容性。

安全性擴充 (TrustZone)

TrustZone (TM) 技術出現在 ARMv6KZ 以及較晚期的套用核心架構中。它提供了一種低成本的方案,針對

系統單晶片 (

SoC )內加入專屬的安全核心,由硬體建構的存取控制方式支援兩顆虛擬的處理器。這個方式可使得套用程式核心能夠在兩個狀態之間切換(通常改稱為領域(worlds)以避免和其他功能領域的名稱混淆),在此架構下可以避免資訊從較可信的核心領域泄漏至較不安全的領域。這種

核心 領域之間的切換通常是與處理器其他功能完全無關聯性(orthogonal),因此各個領域可以各自獨立運作但卻仍能使用同一顆核心。記憶體和周邊裝置也可因此得知核心運作的領域為何,並能針對這個方式來提供對裝置的機密和編碼進行存取控制。典型的 TrustZone 技術套用是要能在一個缺乏安全性的環境下完整地執行作業系統,並在可信的環境下能有更少的安全性的編碼。

套用選型 1、ARM微處理器核心的選擇從前面所介紹的內容可知,ARM微處理器包含一系列的核心結構,以適應不同的套用領域,用戶如果希望使用WinCE或標準Linux等作業系統以減少軟體開發時間,就需要選擇ARM720T以上帶有MMU(Memory Management Unit)功能的ARM晶片,ARM720T、ARM920T、ARM922T、ARM946T、Strong-ARM都帶有MMU功能。而 ARM7TDMI則沒有MMU,不支持Windows CE和標準Linux,但目前有uCLinux等不需要MMU支持的作業系統可運行於ARM7TDMI硬體平台之上。事實上,uCLinux已經成功移植到多種不帶MMU的微處理器平台上,並在穩定性和其他方面都有上佳表現。

2、系統的

工作頻率 在很大程度上決定了ARM微處理器的處理能力。ARM7系列

微處理器 的典型處理速度為0.9MIPS/MHz,常見的ARM7晶片系統主時鐘為20MHz-133MHz,ARM9系列微處理器的典型處理速度為1.1MIPS/MHz,常見的ARM9的系統主

時鐘頻率 為100MHz- 233MHz,ARM10最高可以達到700MHz.不同晶片對時鐘的處理不同,有的晶片只需要一個主時鐘頻率,有的晶片內部時鐘控制器可以分別為ARM 核和USB、UART、DSP、音頻等功能部件提供不同頻率的時鐘。

3、大多數的ARM微處理器片記憶體儲器的容量都不太大,需要用戶在設計系統時外擴存儲器,但也有部分晶片具有相對較大的片記憶體儲空間,如ATMEL的AT91F40162就具有高達2MB的片內程式存儲空間,用戶在設計時可考慮選用這種類型,以簡化系統的設計。

4、片內外圍電路的選擇除ARM微處理器核以外,幾乎所有的ARM晶片均根據各自不同的套用領域,擴展了相關功能模組,並集成在晶片之中,我們稱之為片內外圍電路,如USB接口、IIS接口、LCD控制器、鍵盤接口、RTC、ADC和DAC、DSP協處理器等,設計者應分析系統的需求,儘可能採用片內外圍電路完成所需的功能,這樣既可簡化系統的設計,同時提高系統的可靠性

相關新聞 搭載ARM晶片架構的設備數量是英特爾的25倍。全世界99%的智慧型手機和平板電腦都採用ARM架構。約有43億人每天都會觸摸一台搭載ARM晶片的設備,占全球總人口的60%。

所有的iPhone和iPad都使用ARM的晶片,多數Kindle電子閱讀器和Android設備也都採用這一架構。與這種廣泛觸角極不相稱的是,ARM的營收可以用少得可憐來形容。雖然全世界幾乎所有的智慧型手機幾乎都採用了該公司的晶片設計,但平均每賣出一款這樣的手機,該公司只能得到1美分,而英特爾的晶片單位收益卻高達數十至數百美元不等。

發展前景 ARM網路陣營成員主要包括博通、Cavium和Freescale。其他合作包括與AMD一道為虛擬化軟體打造ENEA的合作、以及與AppliedMicro在虛擬機頂盒(vSTB)概念驗證方面的合作。

大部分領先的網路/電信製造商正積極地將其下一代平台遷移到ARM平台上來,有理由相信在今後的幾年中,ARM在行業中將扮演一個極為重要的角色。

arm處理器階梯圖

arm處理器階梯圖 Roger Wilson和Steve Furber

Roger Wilson和Steve Furber

arm處理器

arm處理器