基本概述

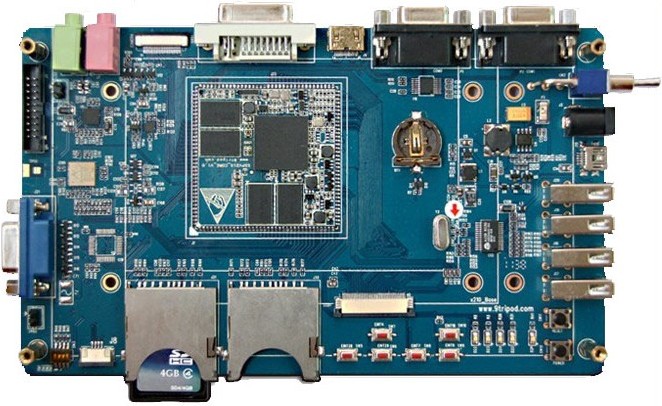

ARM開發板在CPU的基礎上增加外設後如圖中所示,具備許多功能接口,如擴展了TFT-LCD、LVDS接口、觸控螢幕、VGA、矩陣鍵盤、外部匯流排接口、CAN、SPI、PWM、高速USB HOST\Device、SD卡、RS232\RS485串口,音頻、MIC等常用接口,國內領先的嵌入式方案廠商往往有多個核心平台的ARM開發板使各科技類企業的研發工程師可以方便的測試ARM開發板和研發公司的產品,通過開發板內的資料文檔可快速開發公司產品,縮短研發周期。

醫學套用

基於ARM核的ADμC7024在醫療電子中的套用

隨著信息技術的迅猛發展和人民生活水平的提高,極大地推動了醫療電子設備的發展,當今醫療電子設備的發展趨勢是高精度、實時性、低功耗和小尺寸,作為醫療電子設備中核心地位的MCU(

微處理器)也隨著這一發展趨勢向前不斷衍變著。由早期的8位MCU發展到目前的32位RISC(

精簡指令集計算機)MCU。美國ADI公司根據市場的需要最新推出了一款基於ARM(高級精簡指令集計算機)核的微處理器ADμC7024便是目前32位RISC MCU的傑出代表。ADμC7024卓越的處理能力、集成眾多片上外圍器件和晶片低功耗的特點,完全勝任目前醫療電子設備的需求及未來的發展目標。

本文以ADμC7024在醫療電子中監護產品脈搏血氧計的套用為例,重點介紹其在醫療電子行業中的實際用途。

ARM核心特點

英國ARM公司是嵌入式RISC處理器的IP(智慧財產權)供應商,它為ARM架構處理器提供ARM處理器核心(如ARM7TDMI、ARM9TDMI及ARM10TDMI等)。由各半導體公司在上述處理器核心基礎上進行再設計,嵌入各種外圍和處理部件,形成各種MCU。目前基於ARM核心的晶片在

嵌入式處理器市場上占據75%的份額。

ARM作為

嵌入式系統的處理器,具有低電壓,低功耗和高集成度等特點,並具有開放性和可擴充性。事實上,ARM核心已成為嵌入式系統首選的處理器核心。而對於醫療電子設備而言,並不需要

圖像處理等方面更高的要求,因此,ARM7TDMI核心以0.9MIPS(百萬條指令每秒)/MHz的高效處理能力足以滿足套用需要。

ARM7TDMI核心是ARM核系列中32位通用核心中的一個產品,它採用三級流水線結構,指令的執行分成取指、譯值和執行3個階段。

運算器能夠實現32位整數運算。核心不但能夠執行32位高效ARM指令,同時還支持簡潔的16位Thumb指令集以提高代碼密度。

ARM7TDMI名稱的含義為:

b)T:內含16位壓縮指令集Thumb,由於32位RISC型處理器的指令代碼利用率較低,ARM為了彌補不足,在新型ARM架構(V4T版以上,成熟架構由V3版發展到V6版)定義了16位的Thumb指令集,Thumb指令集比通常的8位和16位CISC/RISC處理器具有更好的代碼密度,而晶片面積只增加6%,可使

程式存儲器更小。

c)D:支持片內調試,該核心包含用於調試的硬體結構,可使CPU進入調試模組,可以方便地進行

斷點觀察點設定、

單步調試和多步調試

d)M:採用增強型乘法器。AARM7TDMI指令集包含2個32位×32位的乘法指令和2個乘法累加MAC指令,該結構使得指令的執行比其他類型的ARM7核心減小了許多

機器周期。

e)I:內含嵌入式ICE

宏單元,ARM架構的處理器晶片都嵌入了Embedded ICE-RT邏輯塊,便於通過

JTAG接口來仿真調試RAM架構晶片。

晶片內部結構及特點

美國ADI公司利用其在模擬電路領域的優勢,綜合基於8052-8位ADμC8xx的技術積累,將ARM7TDMI核心和ADC(

A/D轉換器),DAC(

D/A轉換器)等外圍設備集成在一塊晶片上,就是最近推向市場的拳頭產品ADμC702x系列。其中ADμC7020、ADμC7021、ADμC7022、ADμC7026等晶片除了在片上Flash和SRAM容量大小、ADC和DAC通道數量、PWM(脈寬調製)相位數量有差別外,其他完全一致;而ADμC7026,ADμC7027具有外部

擴展記憶體接口。

本文主要介紹其中具有代表性的一款--ADμC7024,工業級的ADμC7024工作於2.7V-3.6V電源電壓,64

引腳CSP封裝的晶片面積僅為9mm×9mm,在1MHz

時鐘頻率下晶片最高功耗為5mA,在最大時鐘頻率45MHz下晶片最高功耗為60mA。其原理框圖如圖1所示。

2.1 片上集成高性能的ADC和DAC

ADμC7024片上集成了10通道12位逐次逼近型ADC,能夠在電源電壓為2.7V-3.6V的範圍正常工作,在

系統時鐘頻率為45MHz下的最高採樣率高達1MSPS(百萬次採樣每秒)。該ADC模組提供一個高精度、低漂移的片上2.5V基準電壓VREF,該電壓通過片上REFCON

暫存器的軟體配置也能作為輸出,向外提供基準參考源。ADC能夠工作於單端轉換模式或者差分轉換模式,在單端轉換模式下的

輸入電壓範圍是0至VREF,在差分轉換模式下輸入電壓範圍是0至AVDD(AVDD通常情況下為3.3V)ADC單個或連續的轉換能夠被外部

引腳CONVstar、片上PLA、

定時器1或定時器2所觸發。

通過ADC

控制暫存器ADCCON,通道選擇暫存器

ADCCP和ADCCN

軟體配置好ADC後,轉換結果將存儲在暫存器ADCDAT位27至位16中,通過ADC

狀態暫存器ADCSTA的位0可以查看ADC轉換是否完成,當ADC轉換結束時,位0被置位;當讀取ADC-DAT時,該位自動被清空。當ADC正在執行轉換操作時,片上引腳ADCBusy保持高電平,一旦轉換結束,該引腳馬上變為低電平。

還可以通過ADCRST

暫存器將ADC模組中所有暫存器恢復至默認值;通過調整ADCOF和ADCGN暫存器的值可以調整ADC轉換精度,不過,該暫存器出廠時已經過校準。

由於該ADC的是逐次逼近型結構,因此比較適合低功耗的產品套用。

ADμC7024片上還集成有2通道12位DAC。每個DAC都具有

軌至軌的輸出電壓範圍,驅動能力可達100pF或者5kΩ,每個DAC也能通過

軟體配置來選擇輸出範圍0至VREF(內部基準電壓)、0至DACref(外部基準電壓)和0至AVDD,而DACref的取值範圍是0V至AVDD。

DAC的使用十分簡單,通過DAC

控制暫存器DAC0CON或者DAC1CON來選擇通道和配置DAC通道特性,然後通過向DAC0CON或DAC1CON的位27至位16寫入數值,就可以在DAC引腳上得到所需要的模擬電壓結果。

2.2 片上集成Flash暫存器和SRAM

ADμC7024片上集成了64KB的

Flash存儲器,其中低62KB的Flash存儲器是用戶可以編程的,剩下的高2kB區域是用戶不可接觸的

固件程式,裡面包含了線上串列下載程式及出廠配置默認方案。ADμC7024片上Flash存儲器能夠通過串列編程模式,JTAG編程模式或

並行編程模式在系統中編程。

1)串列編程模式

當片上BM引腳晶片被拉低時,ADμC7024重啟動將進入串列下載模式,通過標準的UART連線埠或IIC連線埠線上下載程式。

2)並行編程模式

並行編程協定使得片上Flash存儲器能夠通過工業級第三方

編程器進行編程。

3)JTAG編程模式

ADμC7024片上Flash存儲器完全遵守IEEE 1149.1規範,因而可以通過標準的JTAG接口來下載程式和進行調試代碼,使得系統的開發十分簡單易行。

而ADμC7024片上Flash存儲器通過FEEPRO、FEEHIDE

暫存器的軟體設定可以防止程式通過JTAG接口或

並行編程模式被讀出,有效地保障了開發人員的勞動成果。

2.3 晶振和PLL

ADμC7024片上集成了一個32.768KHz晶振、一個時鐘分頻器和一個PLL(鎖相環)。內部的PLL能夠將晶振頻率放大1376倍,即為系統提供一個穩定的45MHz。

為了降低系統功耗,可以通過軟體設定時鐘分頻器的

控制暫存器PLLCON和POWCON將經過PLL後輸出的45MHz降頻,最大可降低至352KHz,由於內部晶振有±3%的誤差,因此,用戶可以選擇外接一個32.768kHz的晶振,通過軟體設定PLLCON值使用外部晶振,使系統的性能穩定可靠。

2.4 復用I/O及標準的UART、SPI、IIC

ADμC7024提供30個通用型雙向I/O

引腳。所有的I/O引腳具有5V電壓耐壓能力,一些I/O引腳中與其他外圍設備引腳復用。在默認情況下,所有的GPIO都是I/O模式,如果在實際中需要將I/O口復用成其他情況的,只需要按照I/O控制配置

暫存器GPxCON的手冊配置方案軟體編程即可(這裡x表示連線埠0,連線埠1,…,連線埠4,如1連線埠5引腳則是P1.5)。在配置成I/O情況下,可以通過置位

數據暫存器GPxDAT中某些位的值使引腳輸出"1";同時可以清除數據暫存器GPxDAT中的某些位的值使引腳輸出"0";還可以讀數據暫存器GPxDAT中某些位的值得到輸入引腳的值(x同前面介紹,具體設定請參考ADμC7024手冊)。

ADμC7024片上集成了2個標準的、全雙工模式的異步串口UART(

通用異步收發器),它們與16450串口標準所兼容。片上UART的

波特率產生器中包含一個小數分頻器,使得UART波特率的產生更加精確。同時,其中一個UART還支持網路

定址模式下的串口傳送接收模式。UART的使用首先通過I/O的配置成UART連線埠

引腳。然後通過

軟體配置UART配置

暫存器及波特率設定暫存器就可以通過COMTX暫存器、COMRX暫存器分別傳送和接收數據。

ADμC7024片上也集成了標準工業級同步串口SPI(串列外圍接口),SPI接口可以同步接收和傳送8位數據,最高速率可達5.6Mbit/s。該SPI能夠被配置成主(Master)或者從(Slave)兩種工作模式,關於SPI使能、選擇工作模式、串列時鐘相位及極性、先傳送低有效位還是高有效位等多項設定,均是通過SPICON編程而得到,而主模式傳送的串列

時鐘頻率由SPIDIV來設定,從模式則不用設定串列時鐘頻率,因為串列時鐘是由主模式的SPI來決定的,通過讀取SPISTA中某些

數據位的值,可以知道SPI是否傳送結束或者接收結束。

ADμC7024還具有兩個經Philips公司授權的IIC接口,IIC是Philips公司20世紀80年代開發的一個簡單的兩線匯流排,包括一條數據線和一條時鐘線,速率有100kHz和400kHz兩種方式,目前IIC已經成為重要的全球業界標準,被所有主要的積體電路廠商所認同和使用。它採用主-從通信方式,採用匯流排仲裁特性,使得在某一時刻只有兩個器件進行通信,具體數據指標參考ADμC7024數據手冊。

中斷系統是一個MCU在套用中的靈魂所在。ADμC7024片上中斷控制器控制著24個

中斷源。這些中斷源包括片上ADC中斷、UART中斷、2個外部

中斷請求XIRQ0和XIRQ1等,而ARM7TDMI核心僅僅將這些中斷源分成兩大類來識別,一類是IRQ,另一類是FIQ。所有中斷源能夠單獨地被禁止。中斷系統的控制和配置管理由9個關於中斷方面的

暫存器所控制,4個涉及到IRQ的暫存器、4個涉及到FIQ的暫存器,1個用來選擇已編程的中斷源暫存器SWICFG。雖然作為一個已編程的

中斷源是不能夠被禁止掉的,但是它們可以被SWICFG來控制。

ADμC7024有4個通用定時器:定時器0、定時器1、定時器2和定時器3。這4個定時器在一般的操作模式下均能按照默認值計數或者按照預設值暫存器TxLD(x表示0,1,2,和3中的某一個暫存器)中值來計算。在任意時刻可以通過讀取TxVAL暫存器中的值了解定時器中的當前計數值。通過配置TxCON的值可以設定相應的定時器按照一定的方式開始計數。

定時器0是一個通用型16位倒計數定時器,該定時器的刻度尺頻率來源是

系統時鐘,計數默認值可以是系統

時鐘頻率、系統時鐘頻率的16分頻和256分頻。

定時器1是一個32位通用型累加定時器或者倒計時定時器。該定時器的刻度尺頻率來源可以是32kHz晶振、系統時鐘和外部GPIO三者之一。計數默認值可以是刻度尺頻率、刻度尺頻率的16分頻、256分頻和32768分頻。定時器1可以被設定為標準的32位時間值,如Hours:Minutes:Seconds:Hundreths這樣的格式。定時器1通過預設回響IRQ事件,可以比通常情況下定時器0回響IRQ

中斷請求要準確得多。它還可以用來觸發ADC轉換過程。

定時器2的系統刻度尺頻率來源是內部集成的32.768kHz晶振,當

系統時鐘停止工作時,該定時器還可以繼續運行,這一特性可以用來將處於

休眠狀態的系統核心恢復至正常工作狀態。

定時器3由兩種工作模式,一種通常模式與前面3個定時器一樣,還有一種是

看門狗模式。一旦程式跑飛時,可以利用該定時器看門狗模式來重啟動處理器,令其恢復正常工作。

2.7 其他外圍設備及特性

片上還集成有獨立的

比較器、電源監控模組、三相PWM(在ADμC7020、ADμC7021、ADμC7022是單相PWM)以及PLA(可程式邏輯陣列)。其中PLA的輸入輸出

引腳與GPIO復用。

引腳定義

ADμC7024引腳定義見表1。 詳細請點擊引用連結。

4 套用實例

該晶片卓越的數據處理能力、片上集成的高精度ADC及DAC等豐富的片上外圍設備以及時鐘頻率可調節的特點,使得在要求低功耗、高精度、實時性等嵌入式微

信號處理系統中的套用如魚得水。現以脈搏血氧計為例,介紹其中一個廣泛的套用領域。其系統框圖如圖2所示。 詳細請點擊引用連結。

ADμC7024作為系統的核心MCU,負責控制和協調其他電路模組的正常工作,它將採集到的血氧信號經過數據處理後,通過SPI匯流排傳送給LCD顯示屏得以顯示。

根據實際臨床結果顯示,ADμC7024已完全勝任設計血氧模組的任務,處理能力、採樣率、採樣精度、功耗、實時性要求等指標完全達到系統的要求,

ARM體系架構使得醫療電子的穩定性得到極大保障。最後,採用第三方Keil公司μVision開發工具,用C語言作為開發語言,利用GNU的ARM-ELF-GCC等工具作為

編譯器及

連結器,易學易用,它的調試仿真工具也是Keil公司開發的Ulink

仿真器,調試簡單,縮短上市時間,便於移植。

可以預料,在不久的將來,ADμC7024以其獨樹一幟的性能必將在醫療電子行業中發揮越來越大的作用。