簡介,工作原理,P0 口,P1 口,P2 口,P3 口,RST,ALE/PROG,PSEN,EA/VPP,XTAL1,XTAL2,特殊功能,數據存儲,片上資源,定時器2,UART串口,時鐘振盪器,中斷,低功耗,節電模式,掉電模式,編程加密,Flash,編程方法,程式加密,數據查詢,

簡介

3、32個雙向I/O口;

5、3個16位可程式定時/計數器中斷;

6、時鐘頻率0-24MHz;

8、2個外部中斷源,共6箇中斷源;

9、2個讀寫中斷口線,3級加密位;

10、低功耗空閒和掉電模式,軟體設定睡眠和喚醒功能;

工作原理

AT89C52為8 位

通用微處理器,採用工業標準的C51核心,在內部功能及管腳排布上與通用的8xc52 相同,其主要用於會聚調整時的功能控制。功能包括對會聚主IC 內部

暫存器、數據RAM及外部接口等功能部件的初始化,會聚調整控制,會聚測試圖控制,紅外遙控信號IR的接收解碼及與主機板

CPU通信等。主要管腳有:XTAL1(19 腳)和XTAL2(18 腳)為振盪器輸入輸出連線埠,外接12MHz 晶振。RST/Vpd(9 腳)為復位輸入連線埠,外接電阻電容組成的復位電路。

VCC(40 腳)和

VSS(20 腳)為供電連線埠,分別接+5V電源的正負端。P0~P3 為可程式通用I/O 腳,其功能用途由軟體定義,在本設計中,P0 連線埠(32~39 腳)被定義為N1 功能

控制連線埠,分別與N1的相應功能管腳相連線,13 腳定義為IR輸入端,10 腳和11腳定義為I2C匯流排控制連線埠,分別連線N1的SDAS(18腳)和SCLS(19腳)連線埠,12 腳、27 腳及28 腳定義為握手信號功能連線埠,連線主機板

CPU 的相應功能端,用於當前制式的檢測及會聚調整狀態進入的控制功能。

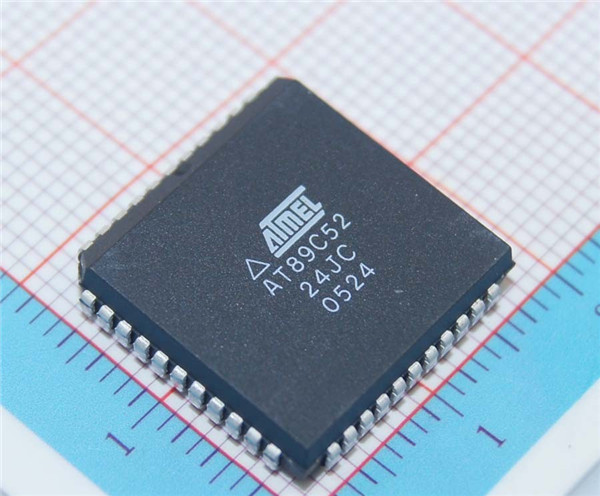

PDIP封裝的AT89C52引腳圖

PDIP封裝的AT89C52引腳圖P0 口

P0 口是一組8 位漏極開路型雙向I/O 口, 也即地址/

數據匯流排復用口。作為輸出口用時,每位能吸收電流的

方式驅動8 個TTL邏輯門電路,對連線埠P0 寫“1”時,可作為高阻抗輸入端用。

在Flash編程時,P0 口接收指令位元組,而在程式校驗時,輸出指令位元組,校驗時,要求外接上拉電阻。

P1 口

P1 是一個帶內部上拉電阻的8 位雙向I/O 口, P1 的輸出緩衝級可驅動(吸收或輸出電流)4 個TTL 邏輯

門電路。對連線埠寫“1”,通過內部的上拉電阻把連線埠拉到高電平,此時可作輸入口。作輸入口使用時,因為內部存在上拉

電阻,某個

引腳被外部信號拉低時會輸出一個電流(IIL)。

與AT89C51 不同之處是,P1.0 和P1.1 還可分別作為定時/計數器2 的外部計數輸入(P1.0/T2)和輸入(P1.1/T2EX),

參見表1。

Flash 編程和程式校驗期間,P1 接收低8 位地址。

表.P1.0和P1.1的第二功能

引腳號 | 功能特性 |

P1.0 | T2,時鐘輸出 |

P1.1 | T2EX(定時/計數器2) |

P2 口

P2 是一個帶有內部上拉電阻的8 位雙向I/O 口,P2 的

輸出緩衝級可驅動(吸收或輸出電流)4 個TTL 邏輯

門電路。對連線埠P2 寫“1”,通過內部的上拉電阻把連線埠拉到高電平,此時可作輸入口,作輸入口使用時,因為內部存在上拉電阻,某個引腳被外部信號拉低時會輸出一個電流(IIL)。

在訪問外部

程式存儲器或16 位地數據存儲器(例如執行MOVX @DPTR 指令)時,P2 口送出高8 位地址數據。在訪問8 位地址的外部數據

存儲器(如執行MOVX@RI 指令)時,P2 口輸出P2

鎖存器的內容。

Flash編程或校驗時,P2亦接收高位地址和一些

控制信號。

P3 口

P3 口是一組帶有內部上拉電阻的8 位雙向I/O 口。P3 口輸出緩衝級可驅動(吸收或輸出電流)4 個TTL 邏

輯門電路。對P3 口寫入“1”時,它們被內部上拉電阻拉高並可作為輸入連線埠。此時,被外部拉低的P3 口將用上拉電阻輸出電流(IIL)。

P3 口除了作為一般的I/O 口線外,更重要的用途是它的第二功能

RST

ALE/PROG

當訪問外部

程式存儲器或數據存儲器時,ALE(

地址鎖存允許)輸出脈衝用於鎖存地址的低8 位字

節。一般情況下,ALE 仍以時鐘振盪頻率的1/6 輸出固定的脈衝信號,因此它可對外輸出時鐘或用於定時目的。要注意的是:每當訪問

外部數據存儲器時將跳過一個ALE 脈衝。

對Flash存儲器編程期間,該

引腳還用於輸入編程脈衝(PROG)。

如有必要,可通過對

特殊功能暫存器(SFR)區中的8EH 單元的D0 位置位,可禁止ALE 操作。該位置位後,只有一條

MOVX 和MOVC指令才能將ALE 激活。此外,該引腳會被微弱拉高,

單片機執行外部程式時,應設定ALE 禁止位無效。

PSEN

程式儲存允許(PSEN)輸出是外部程式

存儲器的讀選通信號,當AT89C52 由外部

程式存儲器取指令(或數

據)時,每個

機器周期兩次PSEN 有效,即輸出兩個脈衝。在此期間,當訪問

外部數據存儲器,將跳過兩次PSEN信號。

EA/VPP

外部訪問允許。欲使CPU 僅訪問外部

程式存儲器(地址為0000H—FFFFH),EA 端必須保持低電平(接

地)。需注意的是:如果加密位LB1 被編程,復位時內部會鎖存EA端狀態。

如EA端為高電平(接Vcc端),CPU 則執行內部程式存儲器中的指令。

Flash

存儲器編程時,該

引腳加上+12V 的編程允許電源Vpp,當然這必須是該器件是使用12V編程電壓Vpp。

XTAL1

振盪器反相放大器及內部時鐘發生器的輸入端。

XTAL2

振盪器反相放大器的輸出端。

特殊功能

在AT89C52 片

記憶體儲器中,80H-FFH 共128 個單元為特殊功能暫存器(SFR),SFR 的

地址空間映象如表2 所示。

並非所有的地址都被定義,從80H—FFH 共128 個

位元組只有一部分被定義,還有相當一部分沒有定義。對沒有定義的單元讀寫將是無效的,讀出的數值將不確定,而寫入的數據也將丟失。

不應將數據寫入未定義的單元,由於這些單元在將來的產品中可能賦予新的功能,在這種情況下,復位後這些單元數值總是“0”。

AT89C52除了有AT89C51所有的定時/計數器0 和定時/計數器1 外,還增加了一個定時/計數器2。定時/計數器2 的控制和狀態位位於T2CON(參見表3)T2MOD(參見表4),

暫存器對(RCAP2H、RCAP2L)是

定時器2 在16 位捕獲方式或16 位自動重裝載方式下的捕獲/自動重裝載暫存器。

數據存儲

AT89C52 有256 個位元組的內部RAM,80H-FFH 高128 個位元組與

特殊功能暫存器(SFR)地址是重疊的,也就是高128位元組的RAM 和特殊功能暫存器的地址是相同的,但物理上它們是分開的。

當一條指令訪問7FH 以上的內部地址單元時,指令中使用的

定址方式是不同的,也即定址方式決定是訪問高128 位元組RAM 還是訪問特殊功能暫存器。如果指令是

直接定址方式則為訪問特殊功能暫存器。

例如,下面的

直接定址指令訪問特殊功能暫存器0A0H(即P2 口)地址單元。

MOV 0A0H,#data

間接定址指令訪問高128 位元組RAM,例如,下面的間接定址指令中,R0 的內容為0A0H,則訪問數據位元組地址為0A0H,而不是P2 口(0A0H)。

MOV @R0,#data

堆疊操作也是間接定址方式,所以,高128 位數據RAM 亦可作為堆疊區使用。

AT89C52的定時器0和定時器1 的工作方式與AT89C51 相同。

片上資源

定時器2

基本特性:

定時器2 是一個16 位定時/計數器。它既可當定時器使用,也可作為外部事件計數器使用,其工作方式由特殊功能寄

存器T2CON(如表3)的C/T2 位選擇。定時器2 有三種工作方式:捕獲方式,自動重裝載(向上或向下計數)方式和波

特率發生器方式,工作方式由T2CON 的控制位來選擇。

定時器2 由兩個8 位暫存器TH2 和TL2 組成,在定時器工作方式中,每個

機器周期TL2 暫存器的值加1,由於一個機

器周期由12 個振盪時鐘構成,因此,計數速率為振盪頻率的1/12。

在計數工作方式時,當T2 引腳上外部輸入信號產生由1 至0 的下降沿時,暫存器的值加1,在這種工作方式下,每個

機器周期的5SP2 期間,對外部輸入進行採樣。若在第一個機器周期中採到的值為1,而在下一個機器周期中採到的值為0,

則在緊跟著的下一個周期的S3P1 期間暫存器加1。由於識別1 至0 的跳變需要2 個

機器周期(24 個振盪周期),因此,最

高計數速率為振盪頻率的1/24。為確保採樣的正確性,要求輸入的電平在變化前至少保持一個完整周期的時間,以保證輸

入信號至少被採樣一次。

捕獲方式:

在捕獲方式下,通過T2CON 控制位EXEN2 來選擇兩種方式。如果EXEN2=0,

定時器2 是一個16 位定時器或計數器,

計數溢出時,對T2CON 的溢出標誌TF2 置位,同時激活中斷。如果EXEN2=1,定時器2 完成相同的操作,而當T2EX 引

腳外部輸入信號發生1 至0 負跳變時,也出現TH2 和TL2 中的值分別被捕獲到RCAP2H 和RCAP2L 中。另外,T2EX 引

腳信號的跳變使得T2CON 中的EXF2 置位,與TF2 相仿,EXF2 也會激活中斷。捕獲方式如圖4 所示。

自動重裝方式:

當

定時器2工作於16位自動重裝載方式時,能對其編程為向上或向下計數方式,這個功能可通過

特殊功能暫存器T2CON

(見表5)的DCEN 位(允許向下計數)來選擇的。復位時,DCEN 位置“0”,定時器2 默認設定為向上計數。當DCEN

置位時,定時器2 既可向上計數也可向下計數,這取決於T2EX 引腳的值,參見圖5,當DCEN=0 時,定時器2 自動設定

為向上計數,在這種方式下,T2CON 中的EXEN2 控制位有兩種選擇,若EXEN2=0,定時器2 為向上計數至0FFFFH 溢

出,置位TF2 激活中斷,同時把16 位計數暫存器RCAP2H 和RCAP2L重裝載,RCAP2H 和RCAP2L 的值可由軟體預置。

若EXEN2=1,

定時器2 的16 位重裝載由溢出或外部輸入端T2EX 從1 至0 的下降沿觸發。這個脈衝使EXF2 置位,如果

中斷允許,同樣產生中斷。

定時器2 的中斷入口地址是:002BH ——0032H 。

當DCEN=1 時,允許定時器2 向上或向下計數,如圖6 所示。這種方式下,T2EX

引腳控制計數器方向。T2EX引腳為邏

輯“1”時,定時器向上計數,當計數0FFFFH 向上溢出時,置位TF2,同時把16 位計數暫存器RCAP2H 和RCAP2L 重裝

載到TH2 和TL2 中。 T2EX 引腳為邏輯“0”時,

定時器2 向下計數,當TH2 和TL2 中的數值等於RCAP2H 和RCAP2L

中的值時,計數溢出,置位TF2,同時將0FFFFH 數值重新裝入定時暫存器中。

當定時/計數器2 向上溢出或向下溢出時,置位EXF2 位。

當T2CON(表3)中的TCLK 和RCLK 置位時,定時/計數器2 作為

波特率發生器使用。如果定時/計數器2 作為傳送器或

表3

表3接收器,其傳送和接收的

波特率可以是不同的,

定時器1 用於其它功能,如圖7 所示。若RCLK 和TCLK 置位,則定時器2

波特率發生器的方式與自動重裝載方式相仿,在此方式下,TH2 翻轉使定時器2 的暫存器用RCAP2H 和RCAP2L 中的16

位數值重新裝載,該數值由軟體設定。

在方式1 和方式3 中,波特率由定時器2 的溢出速率根據下式確定:

方式1和3的波特率=定時器的溢出率/16

定時器既能工作於定時方式也能工作於計數方式,在大多數的套用中,是工作在定時方式(C/T2=0)。定時器2 作為波

特率發生器時,與作為

定時器的操作是不同的,通常作為定時器時,在每個

機器周期(1/12 振盪頻率)

暫存器的值加1,

而作為

波特率發生器使用時,在每個狀態時間(1/2 振盪頻率)暫存器的值加1。

波特率的計算公式如下:

方式1和3的波特率=振盪頻率/{32*[65536-(RCP2H,RCP2L)]}

式中(RCAP2H,RCAP2L)是RCAP2H 和RCAP2L中的16 位無符號數。

定時器2 作為波特率發生器使用的電路如圖7 所示。T2CON 中的RCLK 或TCLK=1 時,波特率工作方式才有效。在

波特率發生器工作方式中,TH2 翻轉不能使TF2 置位,故而不產生中斷。但若EXEN2 置位,且T2EX 端產生由1 至0 的

負跳變,則會使EXF2 置位,此時並不能將(RCAP2H,RCAP2L)的內容重新裝入TH2 和TL2 中。所以,當

定時器2 作

為波特率發生器使用時,T2EX 可作為附加的

外部中斷源來使用。需要注意的是,當定時器2 工作於

波特率器時,作為定

時器運行(TR2=1)時,並不能訪問TH2 和TL2。因為此時每個狀態

時間定時器都會加1,對其讀寫將得到一個不確定的

數值。

然而,對RCAP2 則可讀而不可寫,因為寫入操作將是重新裝載,寫入操作可能令寫和/或重裝載出錯。在訪問

定時器2

或RCAP2

暫存器之前,應將定時器關閉(清除TR2)。

可程式時鐘輸出:

定時器2 可通過編程從P1.0 輸出一個占空比為50%的

時鐘信號,如圖8 所示。P1.0 引腳除了是一個標準的I/O 口外,

還可以通過編程使其作為定時/計數器2 的外部時鐘輸入和輸出占空比50%的

時鐘脈衝。當時鐘振盪頻率為16MHz 時,輸

當設定定時/計數器2 為時鐘發生器時,C/T2(T2CON .1)=0,T2OE (T2MOD.1) =1,必須由TR2(T2CON.2)啟

動或停止

定時器。時鐘輸出頻率取決於振盪頻率和定時器2 捕獲

暫存器(RCAP2H,RCAP2L)的重新裝載值,公式如下:

輸出時鐘頻率=振盪器頻率/{4*[65536-(RCP2H,RCP2L)]}

在時鐘輸出方式下,定時器2 的翻轉不會產生中斷,這個特性與作為

波特率發生器使用時相仿。定時器2 作為波特率

發生器使用時,還可作為時鐘發生器使用,但需要注意的是

波特率和時鐘輸出頻率不能分開確定,這是因為它們同使用

RCAP2L和RCAP2L。

UART串口

AT89C52的UART 工作方式與AT89C51 工作方式相同。

時鐘振盪器

AT89C52 中有一個用於構成內部振盪器的高增益反相放大器,引腳XTAL1 和XTAL2 分別是該放大器的輸入端和輸出端。

這個放大器與作為反饋元件的片外石英晶體或陶瓷諧振器一起構成自激振盪器,振盪電路參見圖10。

外接石英晶體(或陶瓷諧振器)及電容C1、C2 接在放大器的反饋迴路中構成並聯振盪電路。對外接電容C1、C2 雖

然沒有十分嚴格的要求,但電容容量的大小會輕微影響振盪頻率的高低、振盪器工作的穩定性、起振的難易程式及溫度穩

定性,如果使用石英晶體,我們推薦電容使用30pF±10pF,而如使用陶瓷諧振器建議選擇40pF±10pF。

用戶也可以採用外部時鐘。採用外部時鐘的電路如圖10 右圖所示。這種情況下,外部

時鐘脈衝接到XTAL1 端,即內部

時鐘發生器的輸入端,XTAL2 則懸空。

由於外部

時鐘信號是通過一個2 分頻觸發器後作為內部時鐘信號的,所以對外部時鐘信號的占空比沒有特殊要求,但

最小高電平持續時間和最大的低電平持續時間應符合產品技術條件的要求。

中斷

AT89C52 共有6 個

中斷向量:兩個外中斷(INT0 和INT1),3 個

定時器中斷(定時器0、1、2)和

串列口中斷。所有

這些中斷源可通過分別設定專用暫存器IE 的置位或清0 來控制每一個中斷的允許或禁止。IE 也有一個總禁止位EA,

它能控制所有中斷的允許或禁止。

注意表5 中的IE.6 為保留位,在AT89C51 中IE.5 也是保留位。程式設計師不應將“1”寫入這些位,它們是將來AT89 系

列產品作為擴展用的。

定時器2 的中斷是由T2CON 中的TF2 和EXF2

邏輯或產生的,當轉向

中斷服務程式時,這些標誌位不能被硬體清除,

事實上,服務程式需確定是TF2 或EXF2 產生中斷,而由軟體清除中斷標誌位。

定時器0 和定時器1 的標誌位TF0 和TF1 在定時器溢出那個

機器周期的S5P2 狀態置位,而會在下一個機器周期才查

詢到該中斷標誌。然而,定時器2 的標誌位TF2 在定時器溢出的那個機器周期的S2P2 狀態置位,並在同一個機器周期內

查詢到該標誌。

低功耗

節電模式

在空閒工作模式狀態, CPU 自身處於睡眠狀態而所有片內的外設仍保持激活狀態,這種方式由軟體產生。此時,同

由硬體復位終止空閒狀態只需兩個

機器周期有效

復位信號,在此狀態下,片內硬體禁止訪問內部RAM,但可以訪問端

口引腳,當用復位終止空閒方式時,為避免可能對連線埠產生意外寫入,激活空閒模式的那條指令後一條指令不應是一條對

掉電模式

在掉電模式下,振盪器停止工作,進入掉電模式的指令是最後一條被執行的指令,片內RAM 和特殊功能暫存器的內

容在終止掉電模式前被凍結。退出掉電模式的唯一方法是硬體復位,復位後將重新定義全部

特殊功能暫存器,但不改變RAM

中的內容,在Vcc恢復到正常工作電平前,復位應無效,且必須保持一定時間以使振盪器重啟動並穩定工作。

編程加密

Flash

均為FFH),用戶隨時可對其進行編程。

編程接口可接收高電壓(+12V)或低電壓(Vcc)的允許編程信號。低電壓編程模

式適合於用戶線上編程系統,而高電壓編程模式可與通用EPROM

編程器兼容。

AT89C52單片機中,有些屬於低電壓編程方式,而有些則是高電壓編程方式,用戶可從晶片上的型號和讀取晶片內的

簽名位元組獲得該信息。

AT89C52 的

程式存儲器陣列是採用位元組

寫入方式編程的,每次寫入一個位元組,要對整個晶片內的PEROM 程式存儲器

寫入一個非空位元組,必須使用片擦除的方式將整個

存儲器的內容清除。

編程方法

編程前,須按表9 和圖11 所示設定好地址、數據及

控制信號, AT89C52 編程方法如下:

1. 在地址線上加上要編程單元的地址信號。

2. 在數據線上加上要寫入的數據位元組。

3. 激活相應的控制信號。

4. 在高電壓編程方式時,將EA/Vpp 端加上+12V 編程電壓。

5. 每對Flash 存儲陣列寫入一個位元組或每寫入一個

程式加密位,加上一個ALE/PROG編程脈衝。每個位元組寫入周期

是自身定時的,通常約為1.5ms。重複1—5 步驟,改變編程單元的地址和寫入的數據,直到全部檔案編程結束。

程式加密

AT89C52 有3 個

程式加密位,可對晶片上的3 個加密位LB1、LB2、LB3 進行編程(P)或不編程(U)來得到。

當加密位LB1 被編程時,在復位期間,EA 端的邏輯電平被採樣並鎖存,如果

單片機上電後一直沒有復位,則鎖存起的

初始值是一個隨機數,且這個隨機數會一直保存到真正復位為止。為使單片機能正常工作,被鎖存的EA 電平值必須與該引

腳當前的邏輯電平一致。此外,加密位只能通過整片擦除的方法清除。

數據查詢

AT89C52

單片機用Data Palling 表示一個寫周期結束為特徵,在一個寫周期中,如需讀取最後寫入的一個位元組,則讀出的數據的最高位(P0.7)是原來寫入位元組最高位的反碼。寫周期完成後,所輸出的數據是有效的數據,即可進入下一個位元組的寫周期,寫周期開始後,Data Palling 可能隨時有效。

Ready/Busy:位元組編程的進度可通過“RDY/BSY 輸出信號監測,編程期間,ALE 變為高電平“H”後,P3.4(RDY/BSY)端電平被拉低,表示正在編程狀態(忙狀態)。編程完成後,P3.4 變為高電平表示準備就緒狀態。

程式校驗:如果加密位LB1、LB2 沒有進行編程,則代碼數據可通過地址和數據線讀回原編寫的數據,採用如圖12的電路。加密位不可直接校驗,加密位的校驗可通過對

存儲器的

校驗和寫入狀態來驗證。

晶片擦除:利用

控制信號的正確組合(表6)並保持ALE/PROG

引腳10mS 的低電平脈衝寬度即可將PEROM 陣列(4k位元組)和三個加密位整片擦除,代碼陣列在片擦除操作中將任何非空單元寫入“1”,這步驟需再編程之前進行。

讀片內簽名位元組:AT89C52

單片機內有3 個簽名位元組,地址為030H、031H 和032H。用於聲明該器件的廠商、型號和編程電壓。讀AT89C52 簽名位元組需將P3.6 和P3.7 置邏輯低電平,讀簽名位元組的過程和單元030H、031H 及032H 的正常校驗相仿,只返回值意義如下:

(030H)=1EH 聲明產品由ATMEL公司製造。

(031H)=52H 聲明為AT89C52 單片機。

(032H)=FFH 聲明為12V 編程電壓。

(032H)=05H 聲明為5V 編程電壓。

PDIP封裝的AT89C52引腳圖

PDIP封裝的AT89C52引腳圖 表3

表3