基本介紹

- 中文名:復位信號

- 外文名:reset signal

分類

同步復位信號

優點

缺點

異步復位信號

優點

缺點

復位信號重要性

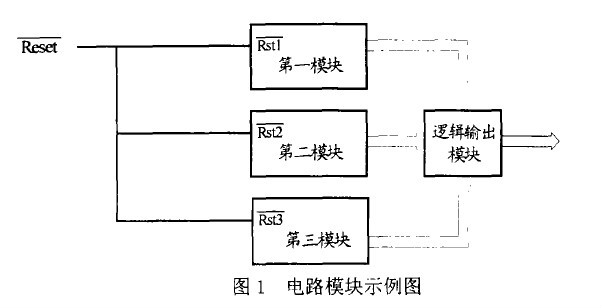

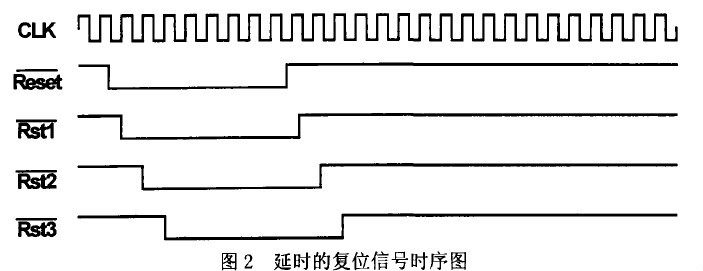

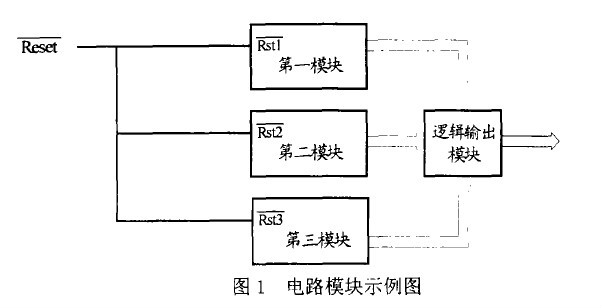

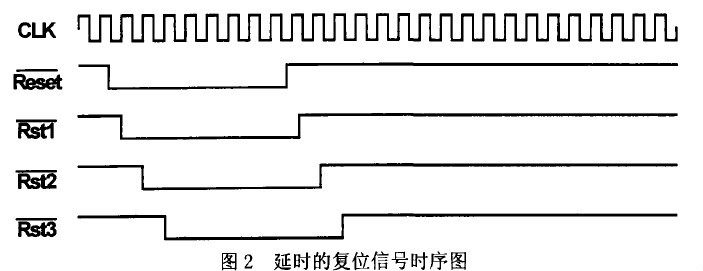

復位信號主要分為兩大類同步復位信號與異步復位信號。同步復位信號是指時鐘有效沿到來時對觸發器進行復位所產生的信號;異步復位信號不依賴於時鐘信號,只在系統復位...

復位電路是一種用來使電路恢復到起始狀態的電路設備,它的操作原理與計算器有著異曲同工之妙,只是啟動原理和手段有所不同。復位電路,就是利用它把電路恢復到起始...

復位是任何一個微處理器所必須有的操作功能,復位的基本作用是使CPU恢復到一個初始的默認狀態,主要是CPU內部指令指針和狀態暫存器設定為一個默認值,使CPU可以從一個...

復位鍵是存在於電腦主機、筆記本電腦、智慧型手機、智慧型PDA或其它電子產品的鍵位,又叫重啟鍵,即RESET。因其功能原因,位置一般比較隱蔽,不容易碰觸。桌上型電腦的復位鍵在...

《網路復位》是一款程式套用,運行環境支持Android2.1。...... 提高數據的速度和改善信號!網路復位套用更新和部隊行動裝置選擇和挑選最好的細胞塔為你當前的位置。...

復位操作是單片機的初始化操作。其功能主要是將程式計數器(PC)初始化為0000H, 使單片機從0000H 單元開始執行程式,並將特殊功能暫存器賦一些特定值表。復位是上電...

異步復位:它是指無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。 ...... 異步復位:它是指無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。...

電阻給電容充電,電容的電壓緩慢上升直到vcc,沒到VCC時晶片復位腳近似低電平,於是晶片復位,接近VCC時晶片復位腳近高電平,於是晶片停止復位,復位完成。...

同步復位, 同步復位:是復位信號和時鐘同步,當時鐘上升沿檢測到復位信號,執行復位操作。 晶片同步復位 具有同步復位功能的晶片一般具有內部時鐘或外部時鐘。而沒有時鐘...

上電復位是指上電壓從無到有在RESET處會先處於高電平一段時間,然後由於該點通過電阻接地,則RESET該點的電平會逐漸的改變為低電平,從而使得單片機復位口電平從1...

控制匯流排主要用來傳送控制信號和時序信號。控制信號中,有的是微處理器送往存儲器和輸入輸出設備接口電路的,比如:讀/寫信號、片選信號、中斷回響信號等;也有是其它...

復位/置位觸發器又被稱為RS觸發器,是由兩個與非門交叉耦合構成的具有復位和置位功能的觸發器。RS觸發器是構成其它各種功能觸發器的基本組成部分,故又稱為基本RS...

簡單來講就是:復位就是清0,置位就是置1。...... 簡單來講就是:復位就是清0,置位就是置1。...(在滿足輸入信號符合高低電平的要求下,不管S腳什麼狀態...

復位IC晶片BL8509是一系列高精度電壓超低消耗電流探測器(500nA典型值在VDD = 3.0V)和一個內置延遲電路。...

AVR復位是一種程式檔案。...... 復位向量處的 指令必須是絕對跳轉JMP 指令,以使程式跳轉到復位處理例程。 AVR的復位信號源有五個: 上電復位。電源電壓低於上電復...

頸椎旋轉復位法是治療寰樞椎半脫位、頸椎後關節錯縫、壓縮等的復位手法。...... 多數是復位信號。立即以同樣手法向左側(對側)旋轉一次。囑患者再搖晃頭頸。如運轉...

復位門限,可監視電源,一旦監視電壓低於工廠設定的復位門限,手動復位被觸發或者看門狗定時器逾時,該器件就會發出復位信號。復位門限最低值1.1V。 ...

信號隔離器是一種信號隔離裝置,將輸入單路或雙路電流或電壓信號,變送輸出隔離的單路或雙路線性的電流或電壓信號,並提高輸入、輸出、電源之間的電氣隔離性能。...

神經信號是一種電信號,其傳導速度極快,信號在神經上傳遞時表現為電位變化,但在胞體間傳遞時卻有不同的介質。產生不同的介質是因為,電衝動打開了電壓門通道,使得...

信號盤相當於控制發動機的開關,其相位角度的設計及精確控制,對發動機各個氣缸的協調工作起著至關重要的作用,信號盤提供信號給轉速感測器,轉速感測器再把信號傳遞給ECU...

控制匯流排主要用來傳送控制信號和時序信號。計算機控制信號(Computer-controlled signal)是計算機系統實施各類動態操作時生成的信號,多數控制信號由CPU生成,但其他功能部件...