基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。

基本介紹

- 中文名:系統時鐘

- 釋義:基於CMOS工藝的高性能處理器

- 特點:集成PLL可以從內部觸發

- 性能:設計頻率為200MHz

基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。

基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。...

時鐘頻率(又譯:時鐘頻率速度,英語:clock rate),是指同步電路中時鐘的基礎頻率,它以“若干次周期每秒”來度量,量度單位採用SI單位赫茲(Hz)。它是評定CPU性能的...

時鐘控制系統,又稱時間控制系統。是用定時裝置產生控制作用的系統。...... 用定時裝置產生控制作用的系統,又稱時間控制系統。時鐘控制系統的套用範圍很廣,從常見的鬧...

電力時鐘同步系統又稱(變電站時鐘系統)選用兩路外部B碼基準,提供高可靠性、高冗餘度的時間基準信號,並採用先進的時間頻率測控技術馴服晶振,使守時電路輸出的時間同步...

GPS時鐘系統是針對自動化系統中的計算機、控制裝置等進行校時的高科技產品,GPS數字產品它從GPS衛星上獲取標準的時間信號,將這些信息通過各種接口類型來傳輸給自動化...

運行環境支持Android 1.5套用類型生活實用類軟體套用介紹一款模仿HTC?Sense界面的天氣時鐘外掛程式,總的來說界面還是比較漂亮的,功能還是比較強大,能夠提供數字時鐘日曆、...

實時時鐘的縮寫是RTC(Real_Time Clock)。RTC 是積體電路,通常稱為時鐘晶片。實時時鐘晶片是日常生活中套用最為廣泛的消費類電子產品之一。它為人們提供精確的實時...

本地時鐘是位於相關設備附近,並與設備有直接關係的時鐘源。通訊設計中為了獲得準確的頻率和定時信號,無不用到時鐘。這個時鐘通常是石英晶體振盪器所產生的振盪信號,...

時鐘是生活中常用的一種計時器,人們通過它來記錄時間。至今為止,在中國歷史上有留下記載的四代計時器分別為:日晷、沙漏、機械鐘、石英鐘。...

邏輯時鐘,可以是計算機、數字電路、機械結構密碼機、CPU內部操作、音效卡、顯示卡和各種系統等等內部操作的時鐘,她的狀態於時間基準有固定或可改變的規則。...

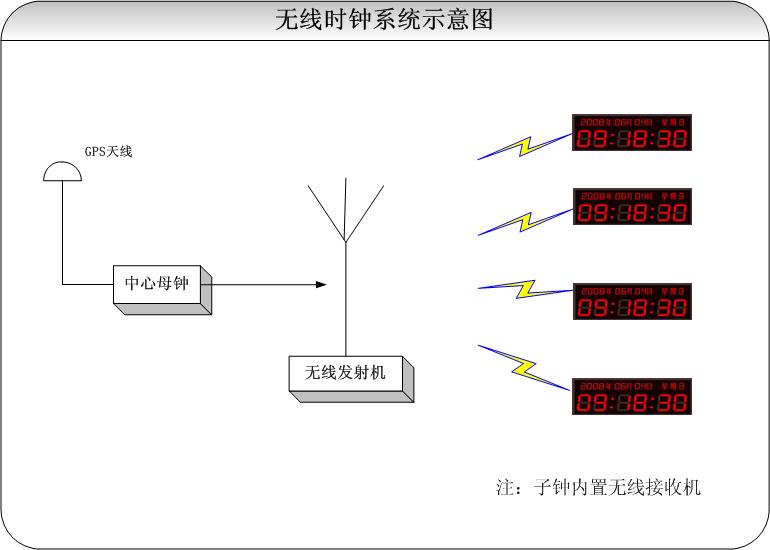

主要套用於要求有統一時間進行生產,調度的單位如:電力,機場、輕軌、捷運、體育場館、酒店、醫院、部隊、油田、水利工程等領域。大區域時鐘系統主要由母鐘和多台子鐘...

時鐘脈衝是指脈衝信號是一個按一定電壓幅度,一定時間間隔連續發出的脈衝信號。...... 電腦中的系統時鐘就是一個典型的頻率相當精確和穩定的脈衝信號發生器。頻率在數...

時間同步系統是一種能接收外部時間基準信號,並按照要求的時間精度向外輸出時間同步信號和時間信息的系統,它能使網路內其它時鐘對準並同步,通俗來說時間同步就是採取...

時間是物質存在和運動的客觀形式,建立時間單位必須以物質的運動為依據。選取的物質運動形式不同,就會有不同的時間系統。早期當人們把地球自轉看作均勻運動時,就以...

BC是網路中間節點時鐘設備,該設備有多個1588連線埠,其中一個連線埠可作為Slave,設備系統時鐘的頻率和時間同步於上一級設備,其他連線埠作為Master,可以實現逐級的時間傳遞。...

時鐘發生器是用來產生時鐘信號的器件。常用於數字產品中,產品中所有的組件將隨著所產生的時鐘信號來同步進行運算動作。數字產品必須有時鐘的控制,才能精確處理數位訊號...

時鐘源用來為環形脈衝發生器提供頻率穩定且電平匹配的方波時鐘脈衝信號。它通常由石英 晶體振盪器和與非門組成的正反饋振盪電路組成,其輸出送至環形脈衝發生器。...

時鐘同步是通過各個能產生時鐘的器件線連線到SCL線上來實現的,上述的各個器件可能都有自己獨立的時鐘,各個時鐘信號的頻率、周期、相位和占空比可能都不相同,由於“...

時鐘信號是計算機科學以及相關領域用語,時鐘信號通常被用於同步電路當中,扮演計時器的角色,保證相關的電子組件得以同步運作。...

桌面時鐘(英文名:Desktop clock),是指集數字時鐘、指針時鐘、桌面月曆、倒計時、日記本和鬧鈴提醒、備忘錄提醒、整點半點報時、網路對時、定時關機、天氣預報、定時...

在計算機中,時鐘速度(clock speed)指的是振盪器設定的處理器節拍,也就是由振盪器產生的每秒脈衝次數。...

提供視覺信息的電子系統。顯示系統按照不同的套用,採用一種或多種、一台或多台顯示設備、提供單人或成組人所需的視覺信息,接收來自不同電子設備或系統的信號,一般...

在數字同步網中,高穩定度的基準時鐘是全網的最高級時鐘源。符合基準時鐘指標的基準時鐘源可以是銫原子鐘組和美國衛星全球定位系統(GPS)。我國目前採用分散式多基準...

東漢公元78年-139年,張衡製造漏水轉渾天儀,用齒輪系統把渾象和計時漏壺聯結起來,...14世紀在歐洲的英、法等國的高大建築物上出現了報時鐘,鐘的動力來源於用繩索...