基本介紹

- 中文名:高阻態

- 外文名:High impedance state

- 定義:數字電路里常見的術語

- 實質:電路分析時高阻態可做開路理解

- 方法:高阻態常用字母 Z 表示

高阻態是一個數字電路里常見的術語,指的是電路的一種輸出狀態,既不是高電平也不是低電平,如果高阻態再輸入下一級電路的話,對下級電路無任何影響,和沒接一樣...

高阻,數字電路里常見的術語,又叫高阻態,指的是電路的一種輸出狀態,既不是高電平也不是低電平。 ...

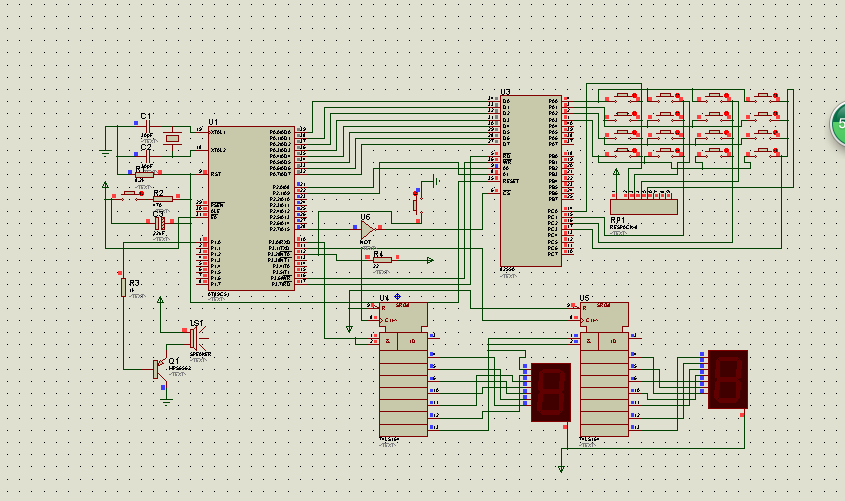

高阻狀態是三態門電路的一種狀態。邏輯門的輸出除有高、低電平兩種狀態外,還有第三種狀態——高阻狀態的門電路。...

阻變式存儲器(RRAM)是以非導性材料的電阻在外加電場作用下,在高阻態和低阻態之間實現可逆轉換為基礎的非易失性存儲器。...

高阻態的意義在於實際電路中不可能斷開電路。三態電路的輸出邏輯狀態的控制,是通過一個輸入引腳實現的。三態門都有一個EN控制使能端,來控制門電路的通斷。 可以...

“高阻態”應理解為“電路”的一種狀態而不是“信號”的一種狀態(數位訊號只有0或1)。 [2] 單穩態電路原理 編輯 單穩態觸發器只有一個穩定狀態,一個暫穩態...

在數字電路中,三態邏輯(英語:Three-state logic)允許輸出端在0和1兩種邏輯電平之外呈現高阻態,等效於將輸出的影響從後級電路中移除。這允許多個電路共同使用同一...

Hi-Z是數字電路常見術語,指的是電路的一種輸出狀態,既不是高電平也不是低電平,如果高阻態再輸入下一級電路的話,對下級電路無任何影響,和沒接一樣,如果用萬...

這樣,這個電路的輸出就有了3個邏輯狀態:邏輯0、邏輯1和高阻態。[2] 當多個三態門的輸出端連在一起形成匯流排時,只要保證任何一個時刻只有一個三態門的輸出控制...

若E=0,緩衝器被阻止,無論輸入什麼值,輸出的總是高阻態,用Z表示。高阻態能使電流降到足夠低,以致於類似緩衝器的輸出沒有與任何東東相連。...

當 OE 為高電平時,Q0~Q7 呈高阻態,既不驅動匯流排,也不為匯流排的負載,但鎖存器內部的邏輯操作不受影響。74LS373引出端 編輯 ...

該三態輸出由輸出使能端1OE和2OE控制。任意nOE上的高電平將使輸出端呈現高阻態。 74HC244與74HC240邏輯功能相似,只不過74HC244帶有正相輸出。...

解釋:在無電涌時呈高阻態,但對電涌回響時,其阻抗突變為低阻值的一種SPD。開關型SPD的常用器件有:火花間隙、氣體放電管等。 ...