工作原理,匯流排特性,匯流排分類,內部匯流排,並發,串列,外部匯流排,並發,串列,計算機匯流排,技術指標,合理搭配,匯流排操作,匯流排標準,優點與缺點,相關信息,匯流排的發展史,ISA匯流排,PCI匯流排,專業術語,

工作原理 如果說主機板(Mother Board)是一座城市,那么匯流排就像是城市裡的公共汽車(bus),能按照固定行車路線,傳輸來回不停運作的

比特 (bit)。這些線路在同一時間內都僅能負責傳輸一個比特。因此,必須同時採用多條線路才能傳送更多數據,而匯流排可同時傳輸的數據數就稱為寬度(width),以比特為單位,匯流排寬度愈大,傳輸性能就愈佳。匯流排的

頻寬 (即單位時間內可以傳輸的總數據數)為:匯流排頻寬 = 頻率 x 寬度(Bytes/sec)。當匯流排空閒(其他器件都以

高阻態 形式連線在匯流排上)且一個器件要與目的器件通信時,發起通信的器件驅動匯流排,發出地址和數據。其他以高阻態形式連線在匯流排上的器件如果收到(或能夠收到)與自己相符的地址信息後,即接收匯流排上的數據。傳送器件完成通信,將匯流排讓出(輸出變為高阻態)。

匯流排特性 由於匯流排是連線各個部件的一組信號線。通過信號線上的信號表示信息,通過約定不同信號的先後次序即可約定操作如何實現。匯流排的特性如下

(1)物理特性:

(2)功能特性:

功能特性是指每一根信號線的功能,如地址匯流排用來表示地址碼。數據匯流排用來表示傳輸的數據,

控制匯流排 表示匯流排上操作的命令、狀態等。

(3)電氣特性:

(4)時間特性:

匯流排分類 匯流排按功能和規範可分為五大類型:

數據匯流排(Data Bus):在CPU與RAM之間來回傳送需要處理或是需要儲存的數據。

地址匯流排(Address Bus):用來指定在RAM(Random Access Memory)之中儲存的數據的地址。

控制匯流排(Control Bus):將微處理器控制單元(Control Unit)的信號,傳送到周邊設備。

擴展匯流排(Expansion Bus):外部設備和計算機主機進行數據通信的匯流排,例如ISA匯流排,PCI匯流排。

局部匯流排(Local Bus):取代更高速數據傳輸的擴展匯流排。

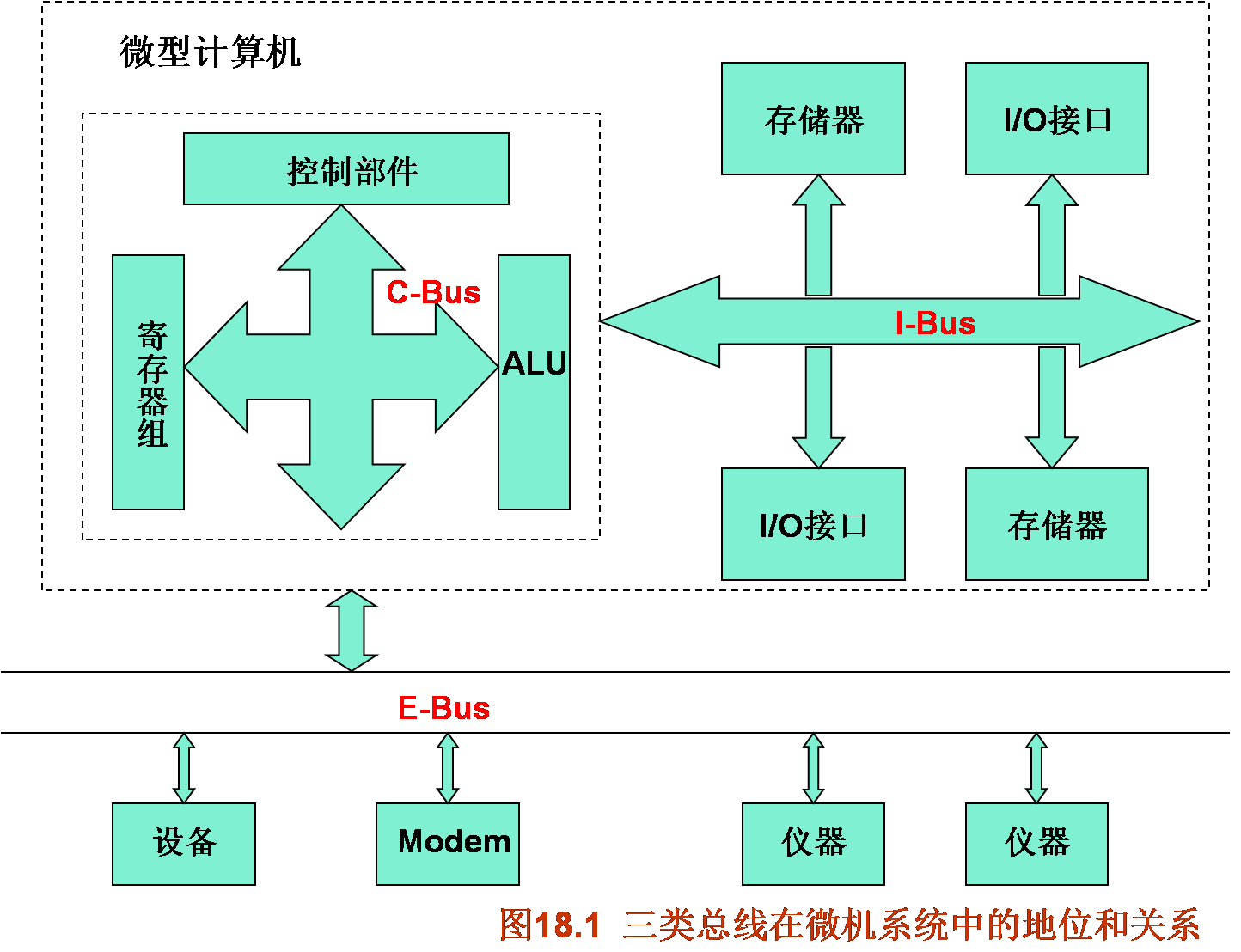

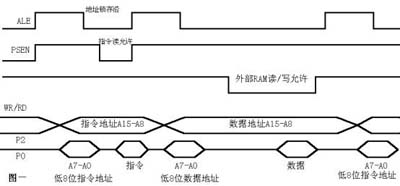

三類匯流排在微機系統中的地位和關係 有的系統中,數據匯流排和地址匯流排是復用的,即匯流排在某些時刻出現的信號表示數據而另一些時刻表示地址;而有的系統是分開的。51系列單片機的地址匯流排和數據匯流排是復用的,而一般PC中的匯流排則是分開的。

“數據匯流排DB”用於傳送數據信息。數據匯流排是雙向三態形式的匯流排,即他既可以把CPU的

數據傳送 到

存儲器 或I/O接口等其它部件,也可以將其它部件的數據傳送到CPU。

數據匯流排 的位數是

微型計算機 的一個重要指標,通常與微處理的字長相一致。例如Intel 8086

微處理器 字長 16位,其

數據匯流排寬度 也是16位。需要指出的是,數據的含義是廣義的,它可以是真正的數據,也可以是指令代碼或狀態信息,有時甚至是一個控制信息,因此,在實際工作中,數據匯流排上傳送的並不一定僅僅是真正意義上的數據。

常見的數據匯流排為ISA、EISA、VESA、PCI等。

“

地址匯流排 AB”是專門用來傳送地址的,由於地址只能從CPU傳向

外部存儲器 或I/O連線埠,所以地址匯流排總是單向三態的,這與數據匯流排不同。地址匯流排的位數決定了CPU可

直接定址 的記憶體空間大小,比如8位微機的地址匯流排為16位,則其最大可

定址空間 為2^16=64KB,16位微型機(x位處理器指一個

時鐘周期 內

微處理器 能處理的位數(1 、0)多少,即

字長 大小)的地址匯流排為20位,其可定址空間為2^20=1MB。一般來說,若地址匯流排為n位,則可定址空間為2^n

位元組 。

“

控制匯流排 CB”用來傳送

控制信號 和

時序信號 。控制信號中,有的是微處理器送往

存儲器 和I/O接口電路的,如讀/寫信號,

片選信號 、

中斷回響 信號等;也有是其它部件反饋給CPU的,比如:中斷申請信號、

復位信號 、匯流排請求信號、設備就緒信號等。因此,控制匯流排的傳送方向由具體控制信號而定,(信息)一般是雙向的,控制匯流排的位數要根據系統的實際控制需要而定。實際上

控制匯流排 的具體情況主要取決於CPU。

按照傳輸數據的方式劃分,可以分為串列匯流排和

並行匯流排 。串列匯流排中,二進制數據逐位通過一根數據線傳送到目的器件;並行匯流排的數據線通常超過2根。常見的串列匯流排有SPI、I2C、USB及RS232等。

按照

時鐘信號 是否獨立,可以分為同步匯流排和異步匯流排。同步匯流排的時鐘信號獨立於數據,而異步匯流排的時鐘信號是從數據中提取出來的。SPI、I2C是同步串列匯流排,RS232採用異步串列匯流排。

內部匯流排 並發 CAMAC,用於儀表檢測系統

MBus

多匯流排(Multibus),用於工業生產系統

NuBus,或稱IEEE 1196

OPTi本地匯流排,用於早期Intel 80486主機板

S-100匯流排(S-100 bus),或稱IEEE 696,用於Altair或類似微處理器

SBus或稱IEEE 1496

VESA本地匯流排(VLB,VL-bus)

VERSAmodule Eurocard bus(VME匯流排)

STD匯流排(STD bus),用於八位或十六位微處理器系統

Unibus

Q-Bus

PC/104 Plus

PC/104 Express

PCI-104

PCIe-104

串列 HyperTransport

串列外圍接口匯流排(SPI匯流排)

火線i.Link(IEEE 1394)

外部匯流排 外部匯流排指纜線和連線器系統,用來傳輸I/O路徑技術指定的數據和控制信號,另外還包括一個匯流排終結電阻或電路,這個終結電阻用來減弱電纜上的信號反射干擾。

並發 串列 計算機匯流排 計算機匯流排是一組能為多個部件分時共享的信息傳送線,用來連線多個部件並為之提供信息交換通路。匯流排不僅是一組信號線,從廣義上講,匯流排是一組傳送線路及相關的匯流排協定。

a. 主機板的匯流排

在計算機科學技術中,人們常常以MHz表示的速度來描述匯流排頻率。計算機匯流排的種類很多,前端匯流排的英文名字是Front Side Bus,通常用FSB表示,是將CPU連線到

北橋晶片 的匯流排。計算機的

前端匯流排頻率 是由CPU和北橋晶片共同決定的。

b.硬碟的匯流排

一般有SCSI、ATA、SATA等幾種。SATA是串列ATA的縮寫,為什麼要使用串列ATA就要從PATA——並行ATA的缺點說起。我們知道ATA或者說普通IDE硬碟的數據線最初就是40根的排線,這40根線裡面有數據線、時鐘線、控制線、地線,其中32根數據線是並行傳輸的(一個

時鐘周期 可以同時傳輸4個位元組的數據),因此對同步性的要求很高。這就是為什麼從PATA-66(就是常說的DMA66)接口開始必須使用80根的硬碟數據線,其實增加的這40根全是禁止用的地線,而且只在主機板一邊接地(千萬不要接反了,反了的話禁止作用大大降低),有了良好的禁止硬碟的傳輸速度才能達到66MB/s、100MB/s和最高的133MB/s。但是在PATA-133之後,並行傳輸速度已經到了極限,而且PATA的三大缺點暴露無遺:信號線長度無法延長、信號同步性難以保持、5V信號線耗電較大。那為什麼SCSI-320接口的數據線能達到320MB/s的高速、而且

線纜 可以很長呢?你有沒有注意到SCSI的高速數據線是“花線”?這可不是為了好看,那“花”的部分實際上就是一組組的差分信號線兩兩扭合而成,這成本可不是普通電腦系統願意承擔的。

匯流排 c.其他的匯流排

計算機中其他的匯流排還有:

通用串列匯流排 USB(Universal Serial Bus)、IEEE1394、PCI等等。

技術指標 匯流排的頻寬指的是單位時間內匯流排上傳送的數據量,即每秒鐘傳送MB的最大穩態數據傳輸率。與匯流排密切相關的兩個因素是匯流排的

位寬 和匯流排的

工作頻率 ,它們之間的關係:

匯流排的頻寬=匯流排的工作頻率*匯流排的位寬/8

或者 匯流排的頻寬=(匯流排的位寬/8 )/

匯流排周期 2、匯流排的 位寬

匯流排的位寬指的是匯流排能同時傳送的二進制數據的位數,或

數據匯流排 的位數,即32位、

64位 等匯流排寬度的概念。匯流排的位寬越寬,每秒鐘數據傳輸率越大,匯流排的頻寬越寬。

3、匯流排的工作頻率

合理搭配 主機板

北橋晶片 負責聯繫記憶體、顯示卡等數據吞吐量最大的部件,並和南橋晶片連線。CPU就是通過前端匯流排(FSB)連線到北橋晶片,進而通過北橋晶片和記憶體、顯示卡交換數據。前端匯流排是CPU和外界交換數據的最主要通道,因此前端匯流排的數據傳輸能力對計算機整體性能作用很大,如果沒足夠快的前端匯流排,再強的CPU也不能明顯提高計算機整體速度。數據傳輸最大頻寬取決於所有同時傳輸的數據的寬度和傳輸頻率,即數據頻寬=(

匯流排頻率 ×數據

位寬 )÷8。目前PC機上所能達到的

前端匯流排頻率 有266MHz、333MHz、400MHz、533MHz、800MHz幾種,前端匯流排頻率越大,代表著CPU與

北橋晶片 之間的數據傳輸能力越大,更能充分發揮出CPU的功能。現在的CPU技術發展很快,

運算速度 提高很快,而足夠大的前端匯流排可以保障有足夠的數據供給給CPU,較低的前端匯流排將無法供給足夠的數據給CPU,這樣就限制了CPU性能得發揮,成為系統瓶頸。

匯流排 匯流排操作 匯流排一個操作過程是完成兩個模組之間傳送信息,啟動操作過程的是主模組,另外一個是從模組。某一時刻匯流排上只能有一個主模組占用匯流排。

匯流排的操作步驟:

主模組申請匯流排控制權,匯流排控制器進行裁決。

匯流排的操作步驟:

主模組得到匯流排控制權後定址從模組,從模組確認後進行數據傳送。

匯流排定時協定:定時協定可保證數據傳輸的雙方操作同步,傳輸正確。定時協定有三種類型:

同步匯流排定時:匯流排上的所有模組共用同一時鐘脈衝進行操作過程的控制。各模組的所有動作的產生均在

時鐘周期 的開始,多數動作在一個時鐘周期中完成。

異步匯流排定時:操作的發生由源或目的模組的特定信號來確定。匯流排上一個事件發生取決前一事件的發生,雙方相互提供聯絡信號。

匯流排定時協定

半同步匯流排定時:匯流排上各操作的時間間隔可以不同,但必須是時鐘周期的整數倍,信號的出現,採樣與結束仍以公共時鐘為基準。ISA匯流排採用此定時方法。

數據傳輸類型:分單周期方式和突發(burst)方式。

突發方式:取得主線控制權後進行多個數據的傳輸。定址時給出目的地首地址,訪問第一個數據,數據2、3到數據n的地址在首地址基礎上按一定規則自動定址(如自動加1)。

匯流排標準 為什麼要制定匯流排標準?

便於機器的擴充和新設備的添加,有了匯流排標準,不同廠商可以按照同樣的標準和規範生產各種不同功能的晶片、模組和整機,用戶可以根據功能需求去選擇不同廠家生產的、基於同種匯流排標準的模組和設備,甚至可以按照標準,自行設計功能特殊的專用模組和設備,以組成自己所需的套用系統。這樣可使晶片級、模組級、設備級等各級別的產品都具有兼容性和互換性,以使整個計算機系統的可維護性和可擴充性得到充分保證。

匯流排標準的技術規範?

機械結構規範:模組尺寸、匯流排插頭、匯流排接外掛程式以及安裝尺寸均有統一規定。

哪種匯流排是標準的?

主機板上的處理器-主存匯流排經常是特定的專用匯流排,而用於連線各種I/O模組的I/O匯流排和底板式匯流排則通常可在不同計算機中互用。實際上,底板式匯流排和I/O匯流排通常是標準匯流排,可被許多由不同公司製造的不同計算機使用。

匯流排標準-ISA

ISA(IndustrialStandardArchitecture)匯流排是IBM公司1984年為推出PC/AT機而建立的系統匯流排標準。所以也叫AT匯流排。

主要特點:

(1)支持64KI/O地址空間、16M主存地址空間的定址,支持15級硬中斷、7級DMA通道。

(2)是一種簡單的多主控匯流排。除了CPU外,DMA控制器、DRAM刷新控制器和帶處理器的智慧型接口控制卡都可成為匯流排主控設備。

(3)支持8種匯流排事務類型:存儲器讀、存儲器寫、I/O讀、I/O寫、中斷回響、DMA回響、存儲器刷新、匯流排仲裁。

它的時鐘頻率為8MHz,共有98根信號線。數據線和地址線分離,數據線寬度為16位,可以進行8位或16位數據的傳送,所以最大數據傳輸率為16MB/s。

匯流排標準-EISA

EISA(ExtendedIndustrialStanderdArchitecture)匯流排 是一種在ISA匯流排基礎上擴充的開放匯流排標準。 支持多匯流排主控和突發傳輸方式。

時鐘頻率為8.33MHz。共有198根信號線,在原ISA匯流排的98根線的基礎上擴充了100根線,與原ISA匯流排完全兼容。具有分立的數據線和地址線。數據線寬度為32位,具有8位、16位、32位數據傳輸能力,所以最大數據傳輸率為33MB/s。地址線的寬度為32位,所以定址能力達232。即:CPU或DMA控制器等這些主控設備能夠對4G範圍的主存地址空間進行訪問。

匯流排標準-PCI

PCI(PeripheralComponentInterconnect)匯流排

是一種高性能的32位局部匯流排。它由Intel公司於1991年底提出,後來又聯合IBM、DEC等100多家PC業界主要廠家,於1992年成立PCI集團,稱為PCISIG,進行統籌和推廣PCI標準的工作。

用於高速外設的I/O接口和主機相連。採用自身33MHz的匯流排頻率,數據線寬度為32位,可擴充到64位,所以數據傳輸率可達132MB/s~264MB/s。

速度快、支持無限突發傳輸方式 、支持並發工作(PCI橋提供數據緩衝,並使匯流排獨立於CPU) ,可在主機板上和其他系統匯流排(如:ISA、EISA或MCA)相連線,系統中的高速設備掛接在PCI匯流排上,而低速設備仍然通過ISA、EISA等這些低速I/O匯流排支持。支持基於微處理器的配置,可用在單處理器系統中,也可用於多處理器系統。

優點與缺點 採用匯流排結構的主要優點

1、面向存儲器的雙匯流排結構信息傳送效率較高,這是它的主要優點。但CPU與I/O接口都要訪問存儲器時,仍會產生衝突。

2、CPU與高速的局部存儲器和局部I/O接口通過高傳輸速率的局部匯流排連線,速度較慢的全局存儲器和全局I/O接口與較慢的全局匯流排連線,從而兼顧了高速設備和慢速設備,使它們之間不互相牽扯。

3、簡化了硬體的設計。便於採用模組化結構設計方法,面向匯流排的微型計算機設計只要按照這些規定製作cpu

外掛程式 、

存儲器 外掛程式以及I/O外掛程式等,將它們連入匯流排就可工作,而不必考慮匯流排的詳細操作。

4、簡化了

系統結構 。整個系統結構清晰。連線少,底板連線可以印製化。

5、系統擴充性好。一是規模擴充,規模擴充僅僅需要多插一些同類型的外掛程式。二是功能擴充,功能擴充僅僅需要按照

匯流排標準 設計新外掛程式,外掛程式插入機器的位置往往沒有嚴格的限制。

6、系統更新性能好。因為cpu、

存儲器 、I/O接口等都是按匯流排規約掛到匯流排上的,因而只要匯流排設計恰當,可以隨時隨著處理器的晶片以及其他有關晶片的進展設計新的

外掛程式 ,新的外掛程式插到底板上對系統進行更新,其他外掛程式和底板連線一般不需要改。

7、便於故障診斷和維修。用主機板測試卡可以很方便找到出現故障的部位,以及匯流排類型。

採用匯流排結構的缺點

由於在CPU與主存儲器之間、CPU與I/O設備之間分別設定了匯流排,從而提高了微機系統信息傳送的速率和效率。但是由於外部設備與主存儲器之間沒有直接的通路,它們之間的信息交換必須通過CPU才能進行中轉,從而降低了CPU的工作效率(或增加了CPU的占用率。一般來說,外設工作時要求CPU干預越少越好。CPU干預越少,這個設備的CPU占用率就越低,說明設備的智慧型化程度越高),這是面向CPU的雙匯流排結構的主要缺點。同時還包括: 1、利用匯流排傳送具有分時性。當有多個主設備同時申請匯流排的使用是必須進行匯流排的仲裁。

2、匯流排的頻寬有限,如果連線到匯流排上的某個硬體設備沒有資源調控機制容易造成信息的延時(這在某些即時性強的地方是致命的)。

3、連到匯流排上的設備必須有信息的篩選機制,要判斷該信息是否是傳給自己的。

相關信息 任何一個微處理器都要與一定數量的部件和外圍設備連線,但如果將各部件和每一種外圍設備都分別用一組線路與

CPU 直接連線,那么連線將會錯綜複雜,甚至難以實現。為了簡化硬體電路設計、簡化系統結構,常用一組線路,配置以適當的接口電路,與各部件和外圍設備連線,這組共用的連線線路被稱為匯流排。

採用匯流排結構便於部件和設備的擴充,尤其制定了統一的匯流排標準則容易使不同設備間實現互連。

微機中匯流排一般有內部匯流排、系統匯流排和外部匯流排。內部匯流排是微機內部各外圍晶片與處理器之間的匯流排,用於晶片一級的互連;而系統匯流排是微機中各外掛程式板與系統板之間的匯流排,用於外掛程式板一級的互連;外部匯流排則是微機和外部設備之間的匯流排,微機作為一種設備,通過該匯流排和其他設備進行信息與數據交換,它用於設備一級的互連。

另外,從廣義上說,計算機通信方式可以分為

並行通信 和

串列通信 ,相應的通信匯流排被稱為並行匯流排和串列匯流排。並行通信速度快、實時性好,但由於占用的口線多,不適於小型化產品;而串列通信速率雖低,但在數據通信吞吐量不是很大的微處理電路中則顯得更加簡易、方便、靈活。串列通信一般可分為異步模式和同步模式。---隨著微電子技術和計算機技術的發展,匯流排技術也在不斷地發展和完善,而使計算機匯流排技術種類繁多,各具特色。

匯流排的發展史 ISA匯流排 (Industry Standard Architecture)

最早的PC匯流排是IBM公司1981年在PC/XT電腦採用的系統匯流排,它基於8bit的8088 處理器,被稱為PC匯流排或者PC/XT匯流排。

1984年,IBM 推出基於16-bit Intel 80286處理器的PC/AT 電腦,系統匯流排也相應地擴展為16bit,並被稱呼為PC/AT 匯流排。而為了開發與IBM PC 兼容的外圍設備,行業內便逐漸確立了以IBM PC 匯流排規範為基礎的ISA(工業標準架構:Industry Standard Architecture )匯流排。

PCI匯流排 (Peripheral Component Interconnect)

由於ISA/EISA匯流排速度緩慢,一度出現CPU 的速度甚至還高過匯流排的速度,造成硬碟、顯示卡還有其它的外圍設備只能通過慢速並且狹窄的瓶頸來傳送和接受數據,使得整機的性能受到嚴重的影響。為了解決這個問題,1992年Intel 在發布486處理器的時候,也同時提出了32-bit 的PCI(周邊組件互連)匯流排。

3、AGP 匯流排

(Accelerated Graphics Port)

PCI 匯流排是獨立於CPU 的系統匯流排,可將顯示卡、音效卡、網卡、硬碟控制器等高速的外圍設備直接掛在CPU 匯流排上,打破了瓶頸,使得CPU 的性能得到充分的發揮。可惜的是,由於PCI 匯流排只有133MB/s 的頻寬,對付音效卡、網卡、視頻卡等絕大多數輸入/輸出設備也許顯得綽綽有餘,但對於胃口越來越大的3D 顯示卡卻力不從心,並成為了制約顯示子系統和整機性能的瓶頸。因此,PCI 匯流排的補充——AGP 匯流排就應運而生了。

4、PCI-Express

在經歷了長達10年的修修補補,PCI 匯流排已經無法滿足電腦性能提升的要求,必須由頻寬更大、適應性更廣、發展潛力更深的新一代匯流排取而代之,這就是PCI-Express 匯流排。

相對於PCI匯流排來講,PCI-Express匯流排能夠提供極高的頻寬,來滿足系統的需求。PCI Express匯流排2.0標準的頻寬如下表所示:

經歷著這么三代半(AGP匯流排只是一種增強型的PCI匯流排)的發展,PC的外部匯流排終於發展到我們現在看到的PCI-E 2.0,提供了比以往匯流排大得多的頻寬。至於今後匯流排發展的方向,相信會隨著人們對頻寬需要的不斷增加,而很快來出現。

專業術語 1.

intermediate distribution bus

2.

VESA local bus (VL-bus) VESA

3.

analysis, bus bounce

4.

analog summing bus

5.

architecture, micro-channel bus (MCA)

6.

arbitration bus

7.

arbiter, bus

8.

backplane bus

9.

back-off, bus

10.

base bus

11.

bus-timing emulation

12.

bus-intensive

13.

bus-control unit

14.

bus, utility

15.

bus, summing

16.

bus, realtime system integration (RTSIBus)

17.

bus, peripheral interface

18.

bus, multisystem extension interface (MXIbus)

19.

bus, multidrop parallel

20.

bus, micro-channel

三類匯流排在微機系統中的地位和關係

三類匯流排在微機系統中的地位和關係 匯流排

匯流排 匯流排

匯流排