浮柵量子點的存儲器是依據量子點的庫侖阻塞原理設計和製備的。

基本介紹

- 中文名:浮柵型單電子存儲器

- 外文名:Floatinggate single-electronemory

產品簡介,背景,

產品簡介

浮柵型單電子存儲器

伴隨著整個半導體微電子產業的發展,存儲器也在以驚人的速度發展。以動態存儲器(DRAM)為例,每個功能元件的尺寸不斷減小,價格不斷下降,每個存儲單元工作所需的電子數目也越來越少。DRAM中的電容如果不能提供足夠多的電子給放大器,整個存儲器將被噪聲所淹沒,將不能保證信息存儲的可靠性。當每個存儲單元的電子數目因集成度的提高變得越來越小時,存儲器中的MOS場效應電晶體將逐漸變得不定,而使整個存儲器的可靠性難以得到保證。

單電子存儲器的出現使存儲器繼續維持高速發展成為可能,目前已經實現室溫下的對背景電荷不敏感的單電子存儲器,因此實際套用的前景非常光明。從目前設計製備出來的單電子存儲器來看,它們的工作通常只需控制幾百個、幾十個甚至幾個電子就可以實現數據的存儲,因此它們的功耗非常低。一般根據存儲器件結構的不同,將其分為單量子點單電子存儲器和多量子點單電子存儲器。

單電子電晶體是單電子存儲器的最主要的組成部分,單電子電晶體的特性在一定程度上決定了基於它製備的存儲器的性能,所以它的發展在很大程度上制約單電子存儲器的發展。在單電子存儲器中,使用對電荷超敏感的庫侖計對存儲單元中的電荷進行探測,來確定存儲單元的狀態。這些超敏感的庫侖計是將單電子電晶體和浮柵與被測的對象集成在一起,利用單電子電晶體對柵極電荷的敏感性來實現電荷的探測。而在另一些單電子存儲器中則是利用單電子電晶體中的庫侖阻塞現象,通過控制源、漏和柵極電壓來實現對源(或漏)上電子數目的精確控制,然後利用其他的放大部分(如MOSFET等)來實現數據的存儲。其中的單電子電晶體有些具有單個量子點結構,而有些則具有納米線結構。

浮柵量子點的存儲器是依據量子點的庫侖阻塞原理設計和製備的。依據Fowler—Nordheim隧穿原理,利用柵極來控制電子進出量子點,使量子點在庫侖阻塞區域的邊界達到兩個穩定的電壓值,此時系統的兩個穩定態對應著量子點兩個不同的勢能。通過電容耦合一個單電子電晶體(庫侖計)或者利用MOS場效應管來對量子點的狀態進行探測,便可以確定出系統的狀態。為了實現單電子器件的高密度存儲,就必須精確控制量子點的形狀和位置,因此這些器件的製備通常具有一定的難度,但是利用掃描探針技術可以製備出常溫下就可以正常工作的單電子存儲器;如果使用納米矽顆粒來製備器件,它們也可以在室溫下工作,並且不受背景電荷漲落的影響。

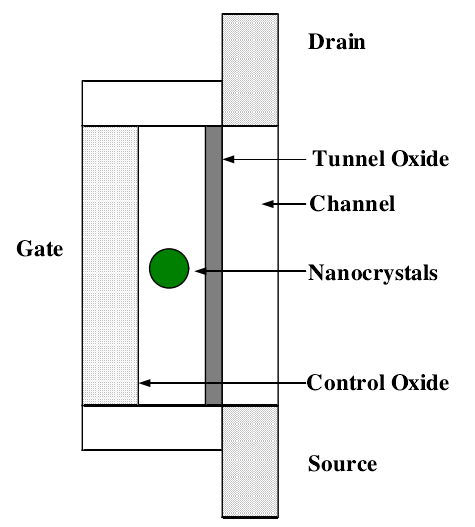

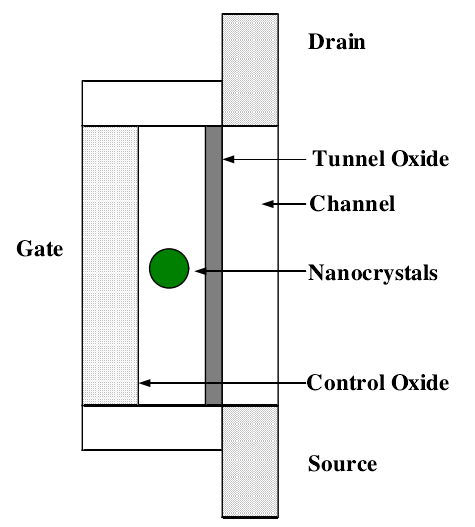

圖表示的是利用量子點和MOS場效應管制備的單電子存儲器的基本結構。納米晶粒(量子點,Dot)放置於MOSFET結構的溝道(Channel)和控制柵極(Control Gate)之間的氧化層中。納米晶粒和溝道被一層薄的氧化物(1 ~ 4.5 nm)隔開,而納米晶粒和控制柵極隔著一層厚的氧化物(5 ~ 10 nm)。

柵極電壓控制量子點的靜電勢能,此時的存儲器存在一個隧穿結,即量子點和溝道之間的絕緣層。通過控制每個電子的Fowler—Nordheim隧穿,使電子一個個的進出量子點,這樣量子點在庫侖阻塞區域的邊界達到兩個穩定的電壓值,它們具有不同的勢能值,代表了存儲器的兩個穩定的存儲狀態。通過電容耦合一個單電子電晶體(庫侖計)或者利用一個MOS場效應管來對量子點的狀態進行探測,便可以確定出系統的狀態。

可以利用多種材料來製備單電子存儲器,不同的材料可以製備出具有不同存儲性能的存儲器。存儲器單元中的柵極和量子點之間有很厚的絕緣層,而量子點和通道之間的絕緣層則很薄,通道中的電子可以隧穿很薄的氧化層進入量子點。柵極用來控制量子點的靜電勢能,當量子點的靜電勢能超出庫侖阻塞區域時,電子會隨著柵壓的變化一個接一個的隧穿氧化層進入量子點。受控電子的運動引起量子點靜電勢能的變化,當系統再次滿足庫侖阻塞條件時,電子的隧穿停止了。此時的量子點靜電勢能將保持恆定,器件處在一個穩定的存儲狀態。由此可見,調節柵極電壓,控制量子點中電子的進出,可以使量子點達到兩個穩定的狀態,並實現存儲器件在這兩個狀態之間的轉化.

由於能級的分立和庫侖阻塞效應的影響,在較低的偏壓下納米晶粒只注入一個電子。這樣就可保證器件在低電壓、低能耗下工作。因為注入過程是直接隧穿過程,而且載流子的熱漲落不會影響到注入過程,所以寫入電流大,寫入時間短。隧穿氧化層厚度是影響寫入過程的重要因素,寫入電流和寫入時間對隧穿氧化層厚度的變化極其敏感。隧穿氧化層厚度每變化 0.15nm,寫入電流和寫入時間就變化一個數量級。

電子注入以後,就被禁錮在矽納米晶粒。存儲狀態時,器件處於靜態零電壓偏置下,矽襯底表面處於耗盡狀態,能級排列不利於隧穿,並且在體矽中,電荷的輸運需要載流子的擴散。所以矽納米晶粒存儲器的存儲時間較長。

在所提出的眾多單電子存儲器模型中,採用納米量子點陣列作為浮置柵極的矽基納米存儲器被認為是將會首先得到套用的納米量子功能器件。在這種結構的存儲器單元中,鑲嵌在二氧化矽層中的矽納米點作為浮置柵極,置於源漏溝道和控制柵極之間,直接隧穿的電荷穿過超薄的隧穿氧化層注入到矽納米點而導致器件閾值電壓的改變,表現出存儲的特點。由於量子限制效應和庫侖阻塞效應,可望實現單電子存儲。文獻首次提出了一種 N 溝道矽基納米存儲器模型,工作電荷為電子;而文獻則首次提出了 P 溝道器件模型,工作電荷為空穴。N 溝道矽基納米存儲器的操作有寫入、保留和擦除三個過程。在寫入過程中,加以適當的正向偏壓,電子從反型層通過直接隧穿到達矽納米點。因為寫入過程是直接隧穿過程,而且載流子的熱漲落不會影響到注入過程,因而寫入電流大,寫入時間短。在電荷保留期間,不加偏壓,電荷被束縛在納米點。有兩種途徑可以造成電荷的泄漏:一是電 荷在矽納米點之間的傳輸,一是電荷遺漏到矽襯底表面,最終回到源極或漏極。由於矽納米點之間的間距大於 5 nm,相互之間的隧穿可以忽略不計。所以納米點所存儲的電子主要是通過後一種途徑逐漸失去的,也是一個直接隧穿的過程,從而導致器件有一個有限的保留時間。若要擦除電子,就要加以適當的負向偏壓,電子由矽納米點處重又回到溝道內。P 溝道矽基納米存儲器的操作過程與 N 溝道器件類似,不同之處在於其操作的電荷是空穴,因而在寫入過程中加負向偏壓,擦除過程中則加正向電壓。

背景

隨著半導體微電子產業的發展, 存儲器的發展速度越來越快。以動態存儲器(DRAM)為例, 其集成度越來越高, 每個功能元件的尺寸不斷減小, 價格不斷下降, 每個存儲單元工作所需的電子數目也越來越少。伴隨存儲單元的電子數目變得越來越小, 存儲器中的MOS場效應電晶體將逐漸變得不穩定, 而使整個存儲器的可靠性難以得到保證。因此,尋求具有更高集成可能的存儲器件成為當今的研究熱點。

1969 年,Lambe和Jaklevic發現了單電子在箱勢阱中的電荷量子化。80年代中期,Averin和Likharev提出了單電子轉移振盪現象和單電子電晶體模型。單電子器件是依據庫侖阻塞原理來控制一個或少數幾個電子的位置或移動,從而實現器件功能的新型器件。早期的工作主要集中在SED的邏輯電路、SET的工作溫度研究和單電子轉移器件。後來Fulton等在進行單電子高阻結轉移試驗時,注意到了I-V特性曲線明顯的時滯特性。同時SET的小尺寸、低功耗、高速度極具誘惑力,於是人們開始了對SEM探索。SED的發展十分迅速。十幾年的時間, 其理論已經有了基本雛形,器件的性能不斷提高,套用範圍不斷拓寬。1995-1998年,各種類型的SET陸續被提出。8TT5 年日本NNT LSI實驗室做成室溫下工作的Si-SET ,1999年日本NEC實驗室做成是利用庫侖阻塞原理.它有幾種結構,都是依據與巨觀結構浮置柵相比,量子點接納一個電子需要大的充電能來設計的。它實際上是原來浮置柵器件的變形。其中量子點代替了原來的浮置柵。由於量子點的大的庫侖充電能,使得在很高的控制柵偏壓下,才能將一個電子隧穿進島。由於隧道勢壘取得合適,在控制柵壓移去後電子並不能隧穿出島,將保持漏源溝道感應導通和截止。只有在高於閾值的寫電壓或擦除電壓下,才能改變島中的電荷態。

單電子學基本概念

有一個小的導體(單電子學中習慣稱之為“島”)為電中性,也就是說在它的晶格內電子數目(m)和質子電荷數目嚴格相等。在這種情況下,島的邊緣以外就不能觀察到電場。這時一個微弱的外力F就可以使島帶有一個附加的電子,在大多數單電子器件中,載流子隧穿通過由薄絕緣介質層形成的勢壘而注入島中。這樣島中的淨電荷Q為-e,帶電的導體將在其周圍產生一個電場。這樣,任何其它電子想向島靠近,都將碰到靜電排斥力。如果這個島的半徑為1nm且放置在真空中,其表面上產生的電場將有14MV/cm大。這個靜電排斥力就是單電子學領域中最基本的庫侖阻塞效應的來源。

單電子存儲器的出現使存儲器繼續維持高速發展成為可能, 目前已經實現室溫下的對背景電荷不敏感的單電子存儲器。從目前設計製備出來的單電子存儲器來看, 它們的工作通常只需控制幾百個、幾十個甚至幾個電子就可以實現數據的存儲, 因此它們的功耗非常低。根據存儲器件結構的不同, 單電子存儲器分為量子點單電子存儲器和納米線單電子存儲器。浮柵量子點的存儲器是依據量子點的庫侖阻塞原理設計和製備的。

柵極電壓控制量子點的靜電勢能, 此時的存儲器存在一個隧穿結, 即量子點和通道之間的絕緣層。通過控制每個電子的Fowler-Nordheim隧穿, 使電子一個個的進出量子點。這樣, 量子點在庫侖阻塞區域的邊界達到兩個穩定的電壓值, 它們具有不同的勢能值, 代表了存儲器的兩個穩定的存儲狀態。通過電容耦合一個單電子電晶體(庫侖計)或者利用一個MOS場效應管來對量子點的狀態進行探測, 便可以確定出系統的狀態。

通過分析建立了相應的集總電容電路模型, 計算了存儲器線上性、飽和、亞閾值情況下的電流。利用單電子器件的“閾值漂移”特性, 可以得到納米存器在不同閾值電壓下的存儲狀態, 即可以準確的“讀取”所存儲的信息。