基本介紹

- 中文名:SV語言

- 外文名:SystemVerilog

- 基礎:Verilog語言

- 性質:將HDL與HVL結合了起來

- 優點:提高了設計建模的能力

- 套用學科:機械工程、儀器科學、計算機科學

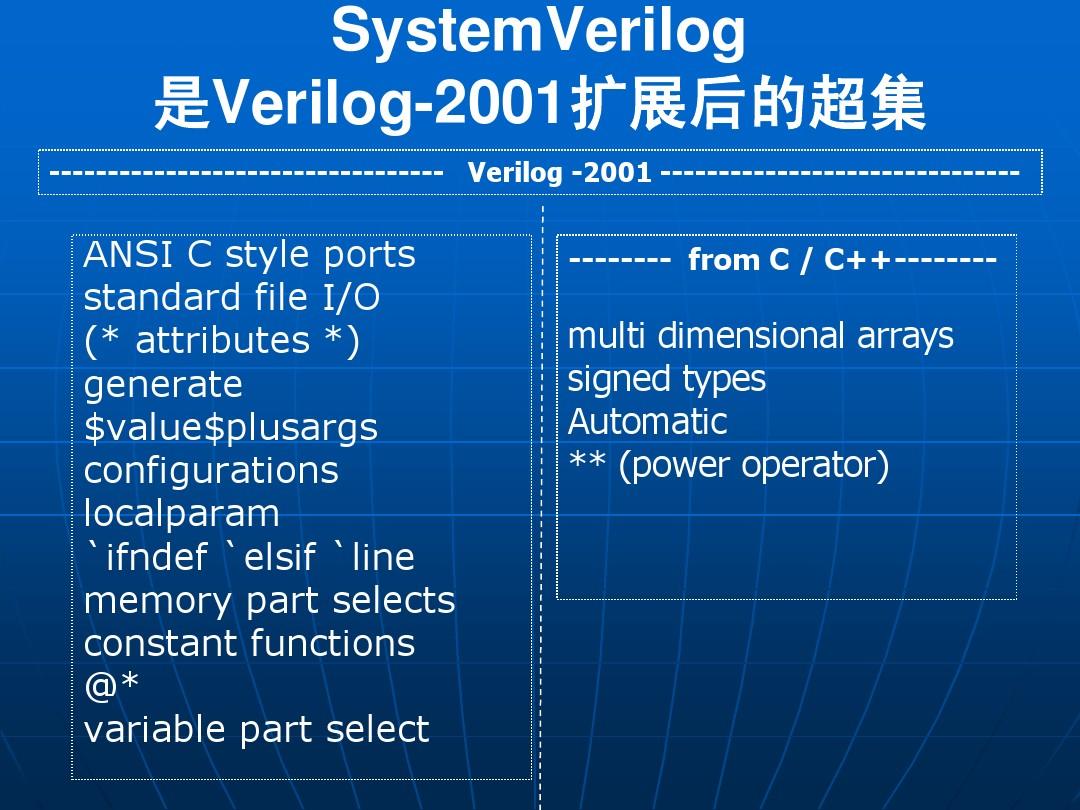

SystemVerilog簡稱為SV語言,是一種相當新的語言,它建立在Verilog語言的基礎上,是 IEEE 1364 Verilog-2001 標準的擴展增強,兼容Verilog 2001,將硬體描述語言(HDL)與...

《SystemVerilog數字系統設計》是2011年2月1日電子工業出版社出版的圖書,作者是茨沃林斯基。...

《SystemVerilog驗證》是2009年科學出版社出版的圖書,作者是克里斯·斯皮爾。...... 本書講解了SystemVerilog語言的工作原理,介紹了類、隨機化和功能覆蓋率等測試手段...

《SystemVerilog與功能驗證》是2010年機械工業出版社出版的圖書,作者是鐘文楓。...... 《System Verilog與功能驗證》重點介紹硬體設計描述和驗證語言System Verilog的基...

《SystemVerilog硬體設計及建模》是2007年科學出版社出版的圖書,作者是(英)StuartSutherland,SimonDavidmann,PeterFlake。...

內容介紹 SystemVerilog驗證方法學,ISBN:9787811240795,作者:(美)伯傑龍、等 1 ...... SystemVerilog驗證方法學,ISBN:9787811240795,作者:(美)伯傑龍、等...

《SystemVerilog數字系統設計》是2012年出版的圖書,作者是馬克。...... 《國外電子信息精品著作:System Verilog數字系統設計(影印版)》由由馬克編寫。System Verilog是2...

《SYSTEM VERILOG ASSERTIONS套用指南》是2006年清華大學出版的圖書,作者是SRIKANTH VIJAYARAGHAVAN[美]。...

Verilog HDL是一種硬體描述語言,以文本形式來描述數字系統硬體的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 ...

作為其主要驗證解決方案,VCS 可提供高性能仿真引擎、約束條件解算器引擎、Native Testbench (NTB) 支持、廣泛的 SystemVerilog 支持、驗證規劃、覆蓋率分析和收斂...

《System Verilog驗證——測試平台編寫指南》是2009年科學出版社出版的一本圖書,作者是克里斯·斯皮爾。...

VMM驗證方法學主要描述如何使用SystemVerilog創建採用覆蓋率主導、隨機約束生成、基於斷言驗證技術的綜合驗證環境,同時為可互用驗證組件指定了建庫數據塊。 VMM驗證方法學...

通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平台開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和...

Vivado 設計套件具備出色的用戶界面,支持System Verilog、SystemC、SDC 和Tcl 等多種ASIC 設計行業標準,這將大幅提高我們的設計生產力。賽靈思的Vivado 設計套件帶來...

Mentor公司的ModelSim是業界最優秀的HDL語言仿真軟體,它能提供友好的仿真環境,是業界唯一的單核心支持VHDL和Verilog混合仿真的仿真器。它採用直接最佳化的編譯技術、Tcl/...

夏宇聞老師為VERILOG設計方法在中國的推廣和套用做了大量工作,曾編寫和翻譯的著作有《Verilog 數字系統設計教程》、《Verilog HDL 數字設計與綜合》、《SystemVerilog ...