通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平台開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和接口的功能驗證環境。

基本介紹

- 中文名:通用驗證方法學

- 外文名:Universal Verification Methodology(UVM)

- 程式語言:SystemVerilog

- 用途:數字電路驗證

- 開發者:accellera

發展歷史

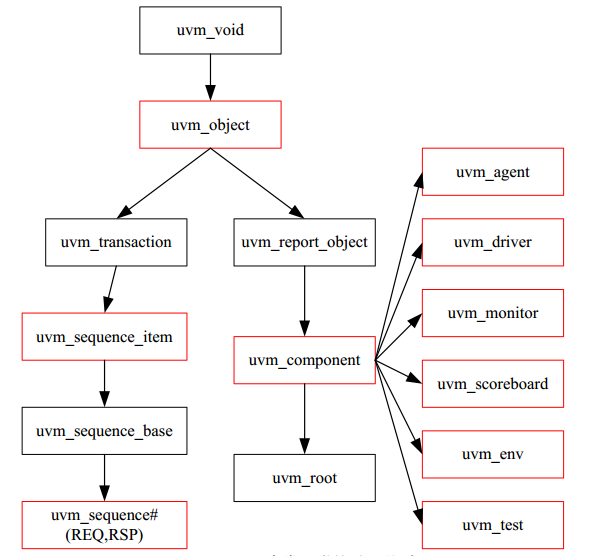

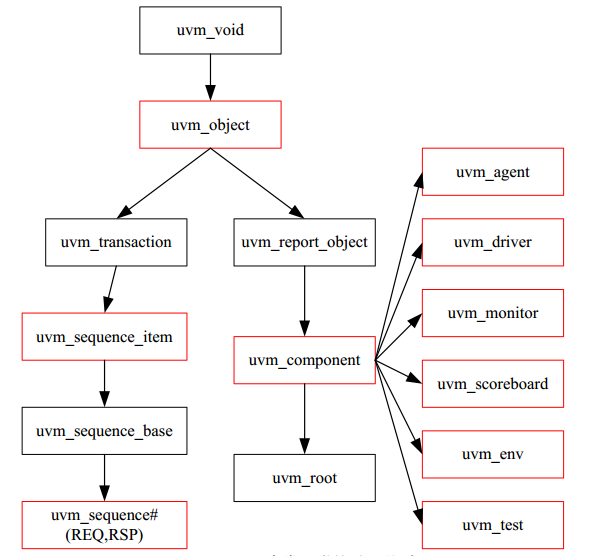

UVM類庫結構

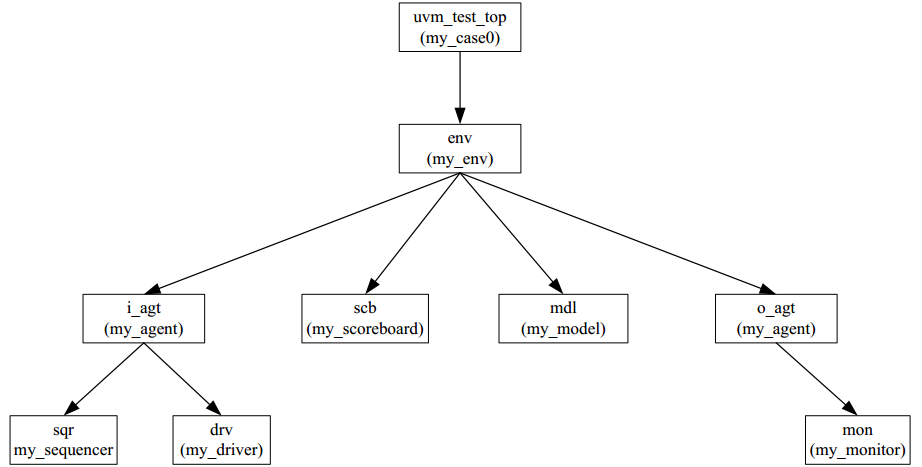

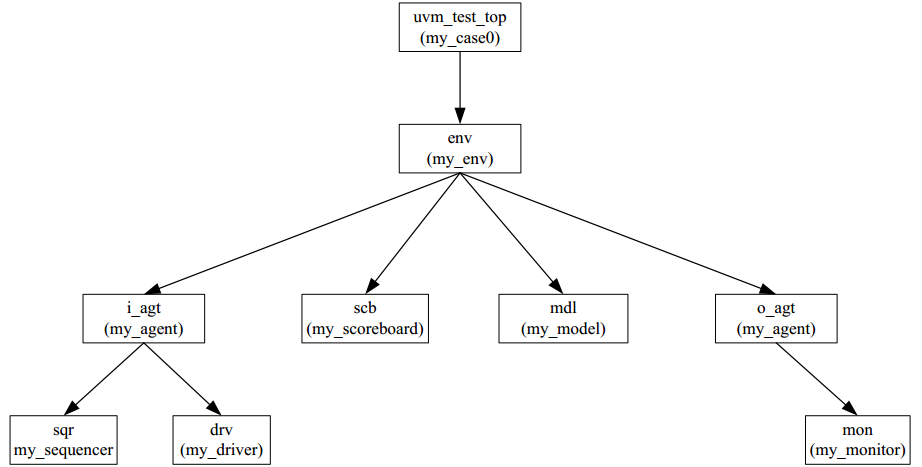

樹型組織結構

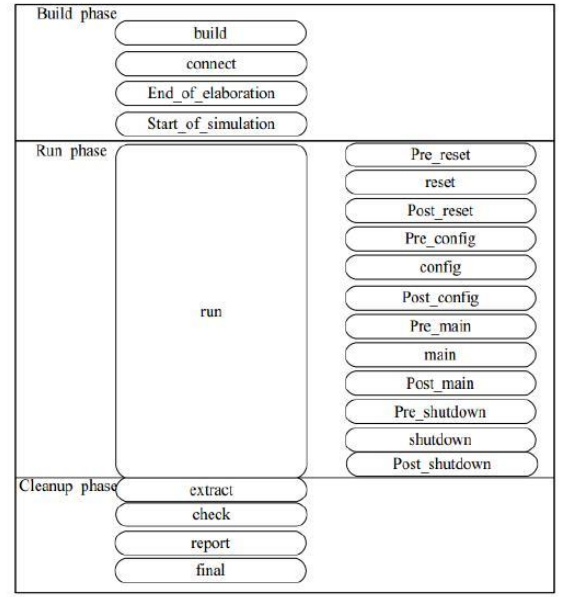

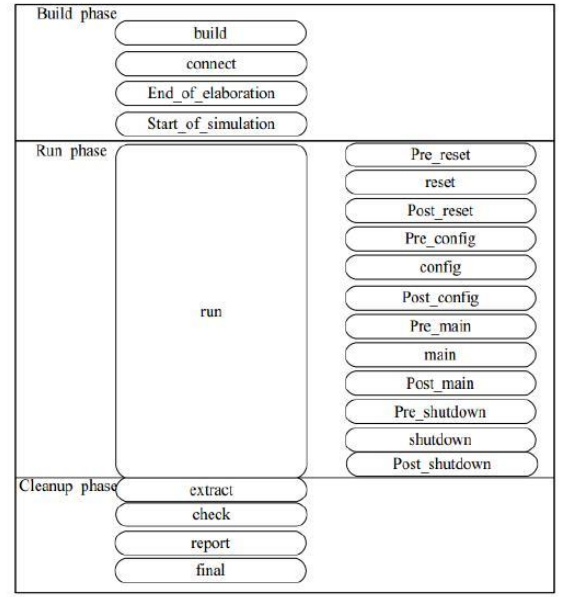

phase機制

通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平台開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和接口的功能驗證環境。

通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平台開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和...

《UVM實戰》是張強創作的網路與通信類書籍。...... 《UVM實戰》主要介紹UVM的使用。全書詳盡介紹了UVM的factory機制、sequence機制、phase機制、objection機制及暫存器模...

描述:uvmserv.exe is a process associated with IBM User Verification Manager Server from IBM Corporation.Recommendation for uvmserv.exe:...

《電子與嵌入式系統設計叢書:UVM實戰(卷1)》以一個完整的示例開篇,使得讀者一開始就對如何使用UVM搭建驗證平台有總體的概念。《電子與嵌入式系統設計叢書:UVM實戰(...

歌曲: Tuff Jam Uvm Dub詞條標籤: 娛樂 V百科往期回顧 詞條統計 瀏覽次數:次 編輯次數:2次歷史版本 最近更新: A溶酶體 突出貢獻榜 ballance1◇惓 ...

佛蒙特大學(University of Vermont,簡稱UVM)位於美國佛蒙特州的伯靈頓市(Burlington),建於1791年,同年佛蒙特州成為美國的第十四個州,是全美歷史最悠久的著名公立研究型...

《晶片驗證漫遊指南》,作者劉斌,出版於2018年04月,主要內容為全面介紹晶片驗證,從驗證的理論,到SystemVerilog語言和UVM驗證方法學,再到驗證項目話題。...

統一驗證方法學(英語:Universal Verification Methodology, UVM)是對積體電路設計的一種標準驗證方法學。...

引進世界頂級東芝納米加工中心UVM-450,和英國FORMTAIYSURF完善的檢測、測量系統,採用美國AMETEK Preci-tech公司Nanoform 250 UltraGrind 4軸單點金剛石精密車床、精密...