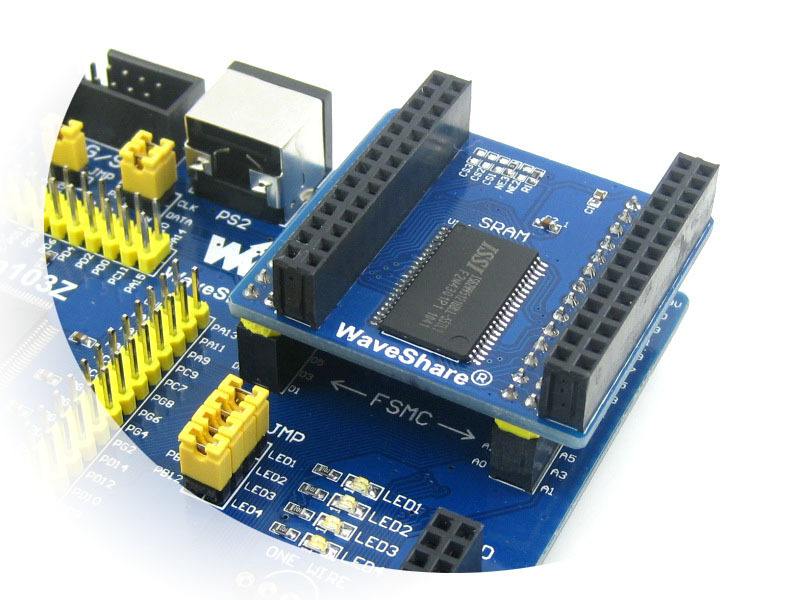

SRAM模組

介紹 RAM 結構框圖如圖1 所示。它主要由存儲矩陣(又稱存儲體)、地址解碼器和讀/寫電路 3 部分組成。存儲矩陣是存儲器的主體,其他兩部分稱為存儲器的外圍電路。

SRAM模組

SRAM模組 存儲矩陣是由許多存儲單元有規則地排列構成的,每一個存儲單元可以存儲一位二進制碼。對每個存儲單元用二進制碼編號,即構成存儲單元的地址,為了選中給定單元的地址,可以採用一元定址(又稱為字結構或單解碼結構),或者二元定址(又稱位結構或雙解碼結構)。其邏輯框圖如2 所示,圖中,存儲矩陣包含 16 個存儲單元,所以,需要 16 個地址。圖2(a)是一元定址,由 4 位地址碼便可構成 16 個地址,即 16 條字線,每條字線為 1 電平時便選中相應存儲單元。被選中單元通過數據線與讀/寫電路連線,便可實現對該單元的讀出或寫入。

圖 2(b)為二元定址邏輯圖,它有 X 和 Y 兩個地址解碼器。每個存儲單元由 X字線和 Y 字線控制,只有在 X 和 Y 字線都被選中時才能對該單元讀出或寫入。二元定址可以大大減少字線數量。所以,在大容量 RAM 中均採用二元定址。

SRAM模組

SRAM模組 靜態 MOS 存儲單元

圖 3 所示的是靜態 MOS 六管存儲單元。圖中,X i和 Yj為字線;I/O 為數據入/輸出端;R/ W 為讀/寫控制端。當 R/ W =0 時,進行寫入操作;當 R/ W =1 時,行讀出操作。

特點 電路均由增強型 NMOS 管構成,T1、T3和 T2、T4兩個反相器交叉耦合構成觸器。電路採用二元定址,當字線 Xi和 Yj均為高電平時,T5~T8均導通,則該單元選中,若此時R/ W為1,則電路為讀出態,三態門G1、G2被禁止,三態門G3工作,存儲數據經數據線 D,通過三態門 G3至 I/O 引腳輸出。若 R/ W 為 0,則三態G1、G2工作,三態門 G3被禁止,由 I/O 輸入數據經 G1、G2便寫入存儲單元。

SRAM模組

SRAM模組 靜態MOS-RAM(簡稱 SRAM)

SRAM產品種類繁多,在容量與功耗等指標上有很寬的覆蓋面,可供不同的場合套用,但基本電路結構大同小異。圖4是W2114 SRAM(1K*4位),這是一種典型結構,5H2112(256*4)和美國的HM6116(2K*8)位都是採用這種結構。它採用HC-MOS工藝(H表示高速),所以,具有高速、低耗、單一5V電源、外圍電路簡單、輸入輸出引腳公用、三態輸出、使用非常簡單以及存取時間短(為100ns)的特點。

SRAM模組

SRAM模組

SRAM模組 SRAM模組 CS為選通端, WE 為寫使能控制端,A0~A9為地址,I/O1~I/O4為輸入/輸出。顯然可見為二元定址和三態輸出結構。 CS為低電平有效,電路選通之後,若要寫入操作,則令 WE =0,輸入三態門被選通(高電平有效),數據通過輸入控制電路被寫入;與此同時,輸出三態門關閉,切斷了輸出與數據匯流排的聯繫。若要讀出,則令 WE =1,輸入三態門關閉而輸出三態門被選通,因而存儲數據被讀出。功能表示於下表。

SRAM模組

SRAM模組 SRAM模組

SRAM模組 SRAM模組

SRAM模組 SRAM模組

SRAM模組 SRAM模組

SRAM模組 SRAM模組

SRAM模組