基本介紹

- 中文名:協處理器

- 外文名:coprocessor

- 類型:一種晶片

- 用途:用於減輕系統微處理器

簡介

特定處理任務

核心相連

擴展指令集

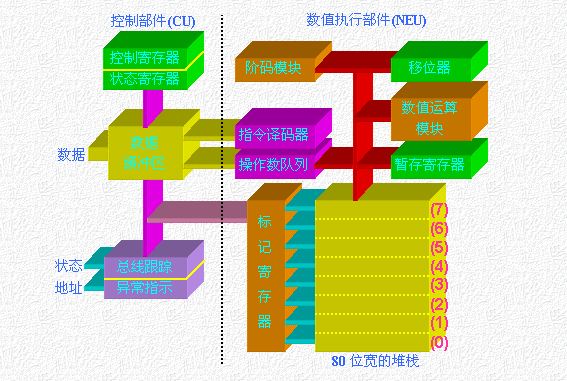

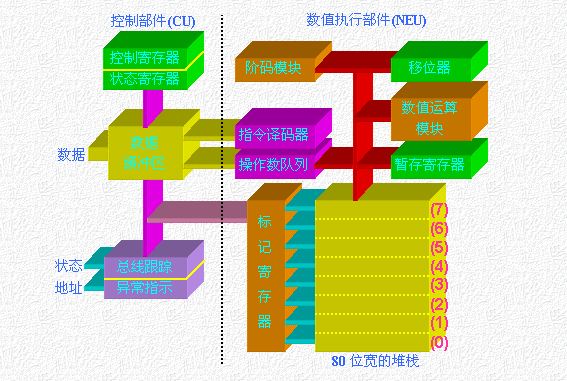

內部結構

協處理器(coprocessor),一種晶片,用於減輕系統微處理器的特定處理任務。協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和...

CELL處理器作為非對稱的多核處理器,其中SPU是協處理器...... CELL處理器作為非對稱的多核處理器,其中SPU是協處理器參考資料:Cell 處理器是由 Sony、Toshiba 和 ...

華為i3協處理器,是搭載在華為智慧型手機晶片上的一款低功耗智慧型感知處理器。i3是各種感測器的管理核心,能以較低的功耗運行,持續採集來自加速計、陀螺儀、指南針和接近...

在計算機科學中,浮點(floating point)是一種對於實數的近似值數值表現法,由一個有效數字(即尾數)加上冪數來表示,通常是乘以某個基數的整數次指數得到。浮點處理器...

蘋果A7處理器採用64位架構。菲爾·席勒在介紹iPhone 5s時更是將其冠以“全球首款搭載64位處理器的手機”的名號,並強調指出A7處理器的性能是A6處理器的兩倍。...

蘋果A8處理器指的是蘋果2014年9月推出的一款新的手機的處理器名稱。 蘋果iPhone6/Plus配備了20納米第二代64位A8晶片,同時也集成了專門的M8運動協處理器。它能...

輔處理器系統是根據輔助處理器功能需求設計開發,主要包括輔助處理器的通信、啟動、硬體管理控制、系統參數修正、存儲五個部分。...

集成性加法協處理器(CLA),是Piccolo C2000中的一款新型C編譯器實現,可採用C語言進行編程,旨在提升創新設計的水平。[1] 該CLA是一個32位浮點數學加速器,專為獨立...

網路處理器(Network Processor,簡稱NP),根據國際網路處理器會議(Network Processors Conference)的定義:網路處理器是一種可程式器件,它特定的套用於通信領域的各種任務...

八十年代末九十年代初,80486處理器面市,它集成了120萬個電晶體,時鐘頻率由25MHz逐步提升到50MHz 。並在X86系列中首次使用了 RISC(精簡指令集)技術,可以在一個...

中文翻譯版由英特爾和北京並行科技有限公司的技術專家陳健、李慧、楊昆、周姍、孫相征、游亮等人翻譯,是全面、系統地講解在英特爾至強處理器和至強融核協處理器上進行...

全息處理器(Holographic Processing Unit, HPU)是可以與CPU與GPU共同運作的一塊協處理器晶片,由微軟在2015年1月21日公布。...

微處理器由一片或少數幾片大規模積體電路組成的中央處理器。這些電路執行控制部件和算術邏輯部件的功能。微處理器能完成取指令、執行指令,以及與外界存儲器和邏輯...

內容介紹 介紹了Inter 80x86和80x87處理器和協處理器的演變、結構和編程。 1 ...... 介紹了Inter 80x86和80x87處理器和協處理器的演變、結構和編程。...

目前英國ARM架構占據手機處理器90%的市場份額。1、德州儀器優點:低頻高能且耗電量較少,高端智慧型機必備CPU缺點:價格不菲,對應的手機價格也很高2、Intel優點:CPU主頻...

數位訊號處理器從20世紀70年代的專用信號處理器開始發展到VLSI陣列處理器,其套用領域已經從最初的語音、聲納等低頻信號的處理髮展到雷達、圖像等視頻大數據量的信號...

中央處理器(Central Process Unit,CPU),是計算機的核心配件之一,其功能主要是解釋計算機指令以及處理計算機軟體中的數據,所謂的計算機的可程式性主要是指對CPU的編程...

至強融核™(Xeon Phi)協處理器,是首款英特爾®集成眾核(Many Integrated Core,MIC)架構產品。...

Xeon Phi是由美國英特爾公司於台北時間2012年11月12日正式推出的首款60核處理器,Xeon Phi並非傳統意義上的英特爾處理器(CPU),它更像是與CPU協同工作...

暫存器是中央處理器內的組成部分。暫存器是有限存貯容量的高速存貯部件,它們可用來暫存指令、數據和地址。在中央處理器的控制部件中,包含的暫存器有指令暫存器(IR)和...

16,000個運算節點,每節點配備兩顆Xeon E5 12核心的中央處理器、三個Xeon Phi 57核心的協處理器(運算加速卡)。累計32,000顆Xeon E5主處理器和48,000個Xeon ...