具有先進先出存儲規則的讀寫存儲器,又稱先進先出棧(FIFO)。

基本介紹

- 中文名:先進先出棧

- 外文名:FIFO stack

- 簡稱:FIFO

- 定義:有先進先出存儲規則的讀寫存儲器

- 系統:計算機

- 套用學科:計算機原理

概述

結構

具有先進先出存儲規則的讀寫存儲器,又稱先進先出棧(FIFO)。

具有先進先出存儲規則的讀寫存儲器,又稱先進先出棧(FIFO)。...... FIFO是先進先出棧,作為數據緩衝器,通常其數據存放結構是完全和RAM一致的,只是存取方式不同。...

先進先出(FIFO,first-in, first-out)是處理從佇列或堆疊發出的程式工作要求的一種方法,它使最早的要求被最先處理。...

(3)由於棧存儲單元只有11個,因此棧的層次最多11層。 [1] 堆疊指令分類 編輯 堆疊指令屬於輸出指令,分為先進先出(FIFO)和後進後出(LIFO)兩種指令。...

3.5.2 並行編譯3.5.3 容量不定的先進先出棧3.5.4 錯在哪裡第4章 庫所/變遷系統(p/t_系統)4.1 可達標識集4.1.1 定義和系統性質4.1.2 覆蓋樹...

8.3.4 FIFO(先進先出堆疊) 習題與思考題 第9章 仿真與邏輯綜合 9.1 仿真 9.1.1 仿真輸入信息的產生 9.1.2 仿真△ 9.1.3 仿真程式模組的書寫 9.2 邏輯綜合...

5.3.3 先進先出堆疊FIFO的設計 5.4 狀態機設計 5.4.1 狀態機概述 5.4.2 Moore狀態機的設計 5.4.3 Mealy狀態機的設計 5.4.4 容錯狀態機的設計 本...

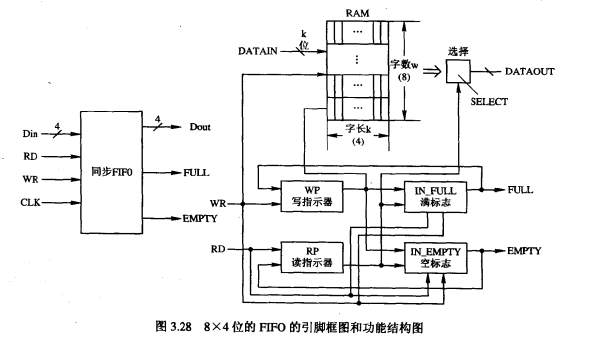

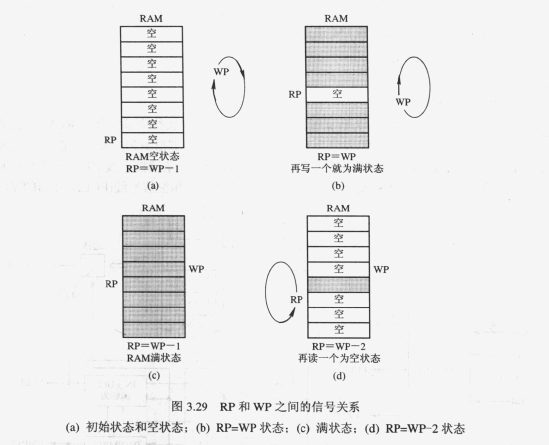

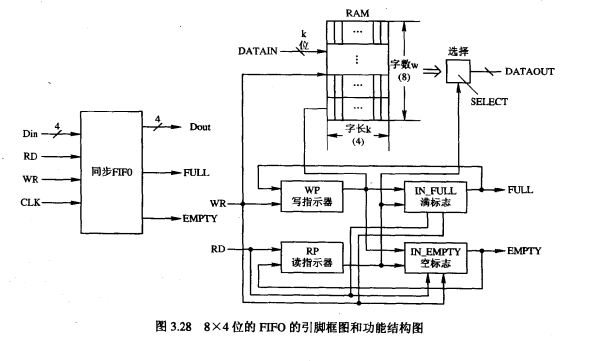

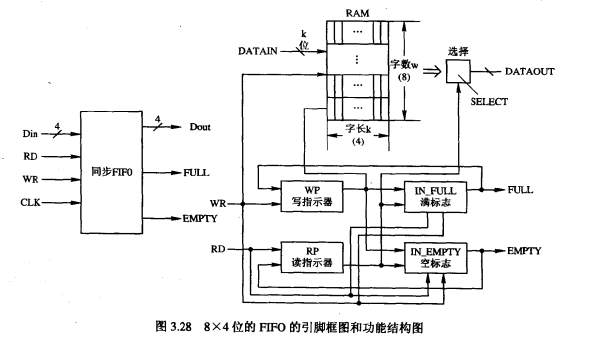

6.3 FIFO(先進先出堆疊)的設計6.3.1 FIFO的功能6.3.2 算法設計和邏輯框圖6.3.3 數據處理單元和控制器的設計6.3.4 設計輸入6.4 九九乘法表系統的設計...

4.3.4先進後出堆疊 4.4有限狀態機 習題 第5章數字系統的層次結構設計 5.1硬體的算法模型 5.1.1先進先出堆疊的算法模型. 5.1.2布思一位補碼乘法器的算法 模...

要點:堆,佇列優先,先進先出(FIFO—first in first out)[1] 。棧,先進後出(FILO—First-In/Last-Out)。中文名 堆疊 外文名 stack 領域 計算機 定義 數據...

8.3.4 FIFO(先進先出堆疊) 196習題與思考題 200第9章 仿真與邏輯綜合 2019.1 仿真 2019.1.1 仿真輸入信息的產生 2019.1.2 仿真Δ 206...