基本介紹

- 中文名:ADRF6510

- 濾波器:6極濾波器

- 特性:省電特性

- 單電源供電:5 V

概述,特性,套用,絕對最大額定值,引腳配置和功能描述,

概述

兩個通道匹配出色,而且在所有增益和頻寬設定下都具有很高的無雜散動態範圍,因此ADRF6510非常適合具有密集星座圖、多個載波並存在鄰近干擾的正交(I-Q)通信系統。

特性

一對匹配的可程式濾波器和可變增益放大器(VGA)

連續增益控制範圍:-5 dB至+45 dB

1 MHz至30 MHz,步進1 MHz,0.5 dB轉折頻率

可程式SPI

6 dB前端增益步長

IMD3:>55 dBc(1.5 V p-p複合輸出)

HD2、HD3:>60 dBc(1.5 V p-p輸出)

差分輸入和輸出

可調輸出共模電壓

可選直流輸出失調校正

套用

基帶I/Q接收機

分集接收機

ADC驅動器

絕對最大額定值

ADRF6510絕對最大額定值

ADRF6510絕對最大額定值注意,超出表中絕對最大額定值可能會導致器件永久性損壞。這只是額定最值,不表示在這些條件下或者在任何其它超出本技術規範操作章節中所示規格的條件下,器件能夠正常工作。長期在絕對最大額定值條件下工作會影響器件的可靠性。

引腳配置和功能描述

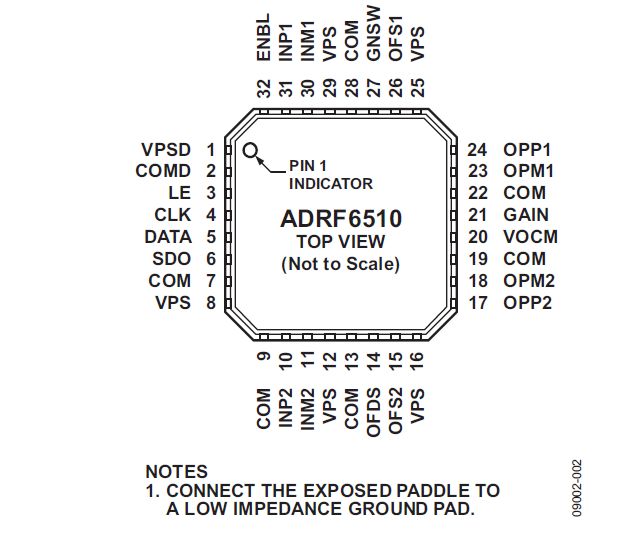

ADRF6510引腳配置

ADRF6510引腳配置引腳編號 | 引腳名稱 | 描述 | ||

1 | VPSD | 數字正電源電壓:4.75 V至5.25 V。 | ||

2 | COMD | 數字公共端。使用儘可能低的阻抗,連線至外部電路公共端。 | ||

3 | LE | 鎖存使能。SPI編程引腳。CMOS電平:VLOW < 0.8 V,VHIGH > 2 V。 | ||

4 | CLK | SPI連線埠時鐘。CMOS電平:VLOW < 0.8 V,VHIGH > 2 V。 | ||

5 | DATA | SPI數據輸入。CMOS電平:VLOW < 0.8 V,VHIGH > 2 V。 | ||

6 | SDO | SPI數據輸出。CMOS電平:VLOW < 0.8 V,VHIGH > 2 V。 | ||

7, 9, 13, 19, 22, 28 | COM | 模擬公共端。通過一個1 kΩ電阻,連線至外部電路公共端。 | ||

8, 12, 16, 25, 29 | VPS | 模擬正電源電壓:4.75 V至5.25 V。 | ||

10, 11, 30, 31 | INP2, INM2,INM1, INP1 | 差分輸入。400 Ω輸入阻抗。共模電壓範圍:1.5 V至2.5 V(默認:2.1 V)。 | ||

14 | OFDS | 禁用失調校正環路。將該引腳拉高,以禁用失調校正環路。 | ||

15, 26 | OFS2, OFS1 | 失調校正環路補償電容。將電容連線至電路公共端。 | ||

17, 18, 23, 24 | OPP2, OPM2,OPM1, OPP1 | 差分輸出。20 Ω輸出阻抗。共模電壓範圍:1.5 V至3 V(默認:VPS/2)。 | ||

20 | VOCM | 輸出共模設定點。在開路的情況下,默認值為VPS/2。 | ||

21 | 增益 | 模擬增益控制。0 V至2 V,30 mV/dB增益調整。 | ||

27 | GNSW | 前端增益切換:6 dB或12 dB。拉低,則增益為6 dB;拉高,則增益為12 dB。 | ||

32 | ENBL | 晶片使能。拉高以使能晶片。 | ||

EP | 底部焊盤。將裸露焊盤與低阻抗接地焊盤相連。 | |||