555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合積體電路。

基本介紹

- 中文名:555時基電路

- 類別:組合積體電路

簡介

它設計新穎,構思奇巧,用途廣泛,備受電子

專業設計人員和電子愛好者的青睞,人們將其戲稱為偉大的小IC。1972年,美國西格尼蒂克斯公司(Signetics)研製出Tmer ne555雙極型

套用介紹

555時基電路

555時基電路

555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合積體電路。

555時基電路

555時基電路《555時基電路》是2007年09月電子工業出版社出版的圖書,作者是陳有卿。本書可供電子電路設計、開發和套用人員及廣大電子愛好者閱讀,也可供大中專院校及職業高中...

《實用555時基電路300例》是2005年1月中國電力出版社出版的圖書,作者是陳有卿。...... 第一部分介紹了555時基電路的工作原理與業餘測試方法;第二部分分定時器、...

《555時基電路識圖》是2007年電子工業出版社出版的圖書,作者是孫余凱、吳鳴山、項綺明。...

555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合積體電路。...... 555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合積體電路...

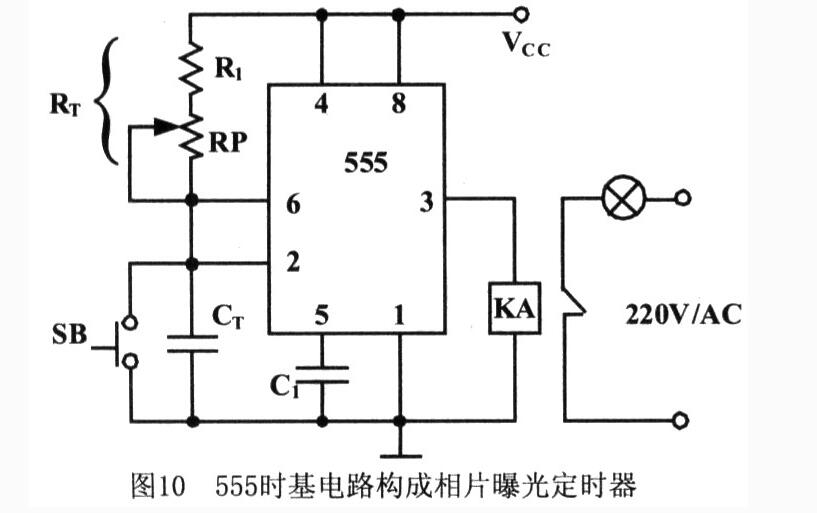

本書是關於555時基集成電路套用技術的圖書,全書共分10章。介紹了555時基集成電路原理與工作模式、555時基集成電路原理在彩燈控制電路、照明電路、定時器、報警器、...

《555時基實用電路解讀》圖文並茂、重點突出、直觀易懂、實用性強,適合廣大電子技術愛好者、家電維修人員和相關行業從業人員閱讀學習,並可作為職業技術學校和務工人員...

《555時基電路套用280例》是化學工業出版社出版的圖書,作者是趙光。...... 本書根據555時基電路的功能以及特點,以實例的形式介紹555時基電路在定時、延時方面的應...

《555套用電路精選》是2010年01月機械工業出版社出版的圖書,作者是張慶雙。...... 《555套用電路精選》分為兩部分。第一部分介紹了555時基集成電路的基礎知識,包括...

時基是一個時間顯示的基本單位。時基即時間基準,在電子線路中主要用來表示數字電路中的基準時鐘。...

NE555 (Timer IC)為8腳時基集成電路,大約在1971年由Signetics Corporation發布,在當時是唯一非常快速且商業化的Timer IC,在往後的40年中非常普遍被使用,且延伸出...

一、由分立件組成的魚類養殖用增氧控制電路二、由555時基電路組成的魚類養殖用增氧控制電路三、魚類孵化池控制電路四、自動投料控制電路...

時基集成電路555並不是一種通用型的集成電路,但它卻可以組成上百種實用的電路,可謂變化無窮,故深受人們的歡迎。...

《555時基電路》是2007年09月電子工業出版社出版的圖書,作者是陳有卿。本書可供電子電路設計、開發和套用人員及廣大電子愛好者閱讀,也可供大中專院校及職業高中...

《555時基電路原理、設計與套用》是2007年電子工業出版社出版的圖書,作者是陳有卿,葉桂娟。本書主要介紹了關於555時基電路的特點、原理和套用。...

《電工控制電路圖集(精華本)》是2015年化學工業出版社出版的圖書,作者是方大千...3.3.2採用555時基集成電路的多功能保護電路1623.3.3電流互感器多功能保護...

為了提高該電路的變換效率,PWM控制採用貴生動力專用研發的集成控制器件;脈衝產生電路採用了555時基電路與十進位計數器/分頻電路。DC/DC變換部分是使用貴生動力專用...

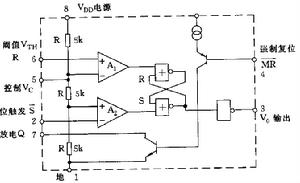

4.4 時間鑑別電路的繪製4.4.1 繪製電路的分析4.4.2 繪製三組電阻和發光二極體4.4.3 繪製RS觸發器4.4.4 繪製與非門4.4.5 繪製555時基電路模組...