基本介紹

- 中文名:頻率抖動技術

- 外文名:Frequency Jitter

- 作用:減少由PWM驅動信號產生的EMI

- 釋義:開關電源的工作頻率周期性地變化

- 套用:PWM晶片和TOPGX系列晶片中

- 優點:高效而且可靠、等

簡介,頻率抖動技術的套用示例,電磁干擾測試標準及原理,頻率抖動技術工作原理,頻率抖動技術與其它方法的比較,

簡介

由於採用脈寬調製(PWM)控制方式的開關電源的開關頻率不斷提高,使其高頻開關波形中的大量諧波成分通過傳輸線和空間電磁場向外傳播,從而造成了不可忽視的傳導和輻射干擾問題。

隨著通訊及控制技術的發展,各種高頻數字電路對開關電源電磁兼容性(EMC)的要求更加嚴格,如何減小電磁干擾(EMI)成為開關電源設計中的一個難點。與常用的抗干擾技術相比,頻率抖動技術(Frequency Jitter)是一種從分散諧波干擾能量著手解決EMI問題的新方法。頻率抖動技術是一種通過改善控制技術來最佳化性能的新方法,該方法首先在高頻數字電路中開始使用,現在已被集成開關電源晶片所採用而大量套用於小功率開關電源產品中,從而為抑制開關電源的電磁干擾提供了一種新的思路。

頻率抖動技術是指開關電源的工作頻率並非固定不變,而是周期性地變化來減小電磁干擾的一種方法。以下以TOPGX功率集成晶片為例,結合電磁干擾的產生機理和測量方法來說明頻率抖動技術的工作原理及作用。

頻率抖動技術的套用示例

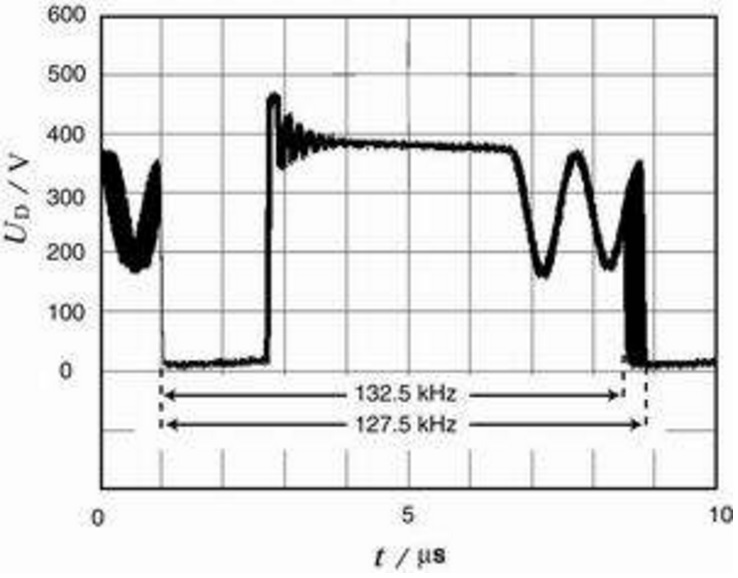

TOPGX系列晶片是一種內含PWM控制電路和MOSFET的功率晶片,工作頻率為132kHz,可周期性地以132kHz為中心頻率上下變動4kHz。能在4ms周期(頻率為250Hz)內完成一次從128 kHz至136 kHz之間的頻率抖動。

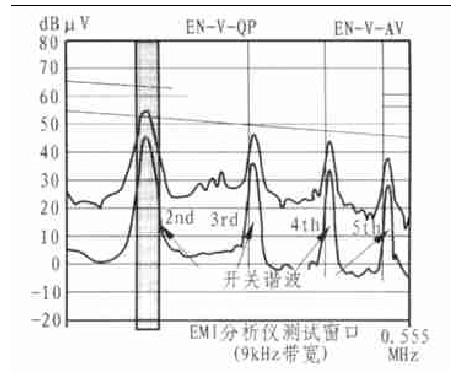

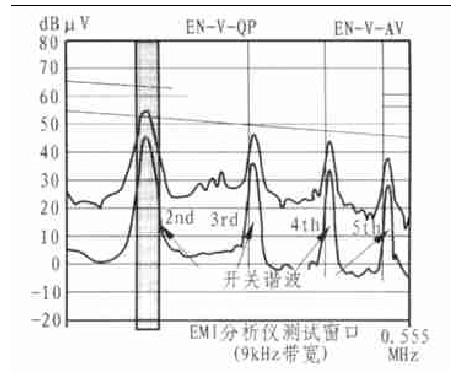

採用相同的外圍電路和初級峰值電流的情況下,對套用頻率抖動技術和未採用頻率抖動技術的電源準峰值(QP)和平均值(AV)進行了比較,結果發現,未採用頻率抖動技術時,各次諧波較窄而且離散,幅值在諧波頻率處較高;而採用頻率抖動技術時的諧波幅值明顯降低,並且變得平滑,高次諧波接近連續回響。可以明顯看出減小EMI的效果十分顯著。為了分析頻率抖動技術的工作原理,下面先解釋一下EMI的測試標準及測量原理。

電磁干擾測試標準及原理

國際無線電干擾特別委員會(CISPR)為美國聯邦通信委員會(FCC)分別制定的CISPR22和FCC標準已分別在歐洲和北美使用。歐洲的EN55022標準等同於CISPR22標準。A級為工業級,B級為民用級,B級標準比A級標準嚴格。其中150kHz~ 30MHz為傳導測量範圍,30MHz~ 1GHz為輻射測量範圍。 圖1

圖1

圖1

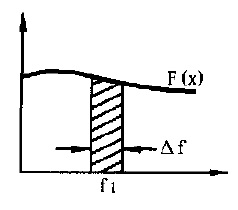

圖1測量電磁干擾的原理是用干擾分析儀將噪聲信號中的頻率分量以一定的通頻帶選擇出來,並予以顯示和記錄,當連續改變設定頻率時就能得到噪聲信號的頻譜。干擾分析儀以9kHz頻寬掃描整個頻帶,測量出噪聲信號的準峰值和平均值,圖1所示是9kHz掃描時的準峰值和平均值曲線。

頻率抖動技術工作原理

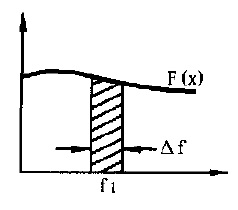

對噪聲信號進行諧波分析,可得出諧波波形中各次諧波的幅值和相角。在電磁兼容性技術中,人們所關心的只是將噪聲幅值限制在規定的限度內。各次諧波幅值隨頻率的分布稱為幅密度頻譜。在頻率f1處,頻頻寬為Δf的諧波幅度為F(f1)Δf,如圖2所示。 圖2

圖2

圖2

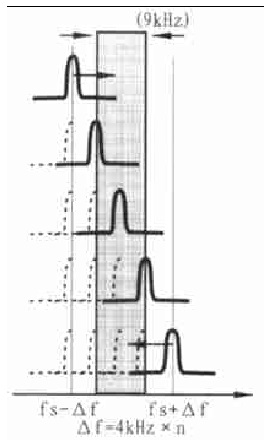

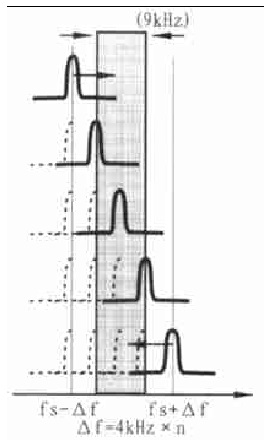

圖2周期干擾信號的頻譜為離散型,各譜線高度為二次諧波、三次諧波… …的幅值,譜線間的距離為基波頻率的整數倍。採用頻率抖動技術後,基波頻率變化幅值為± 4kHz,二次諧波為± 8kHz… … , n次諧波為± 4nkHz(如圖3所示)。因此可以看出:諧波次數越高,頻率分散越大。這樣,噪聲諧波頻率的分散使各次諧波在f1處能量的疊加降低,從而使噪聲能量得以分散和減小,這樣,就在整個頻帶上保證了幅值裕量,滿足了電磁兼容性的要求。 圖3

圖3

圖3

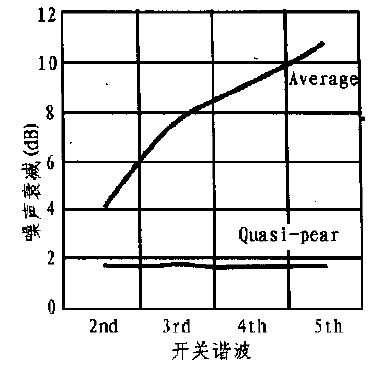

圖3採用頻率抖動技術後,其噪聲信號的準峰值(QP)隨頻率增加的變動不大,約下降2dB,而噪聲信號的平均值(AV)則隨著頻率的增加而下降得十分明顯。所以頻率抖動技術在高頻段效果更為顯著,圖4給出了噪聲衰減與開關諧波的關係曲線。另外,需要指出的是:實現頻率抖動技術需要為PWM發生器中的振盪器設定頻率調整環節。

圖4

圖4頻率抖動技術與其它方法的比較

頻率抖動技術較之於其它方法具有更突出的優點。由於形成開關電源電磁干擾的三個條件是干擾源、耦合途徑和受擾設備。因此常用的抑制電磁干擾方法有以下幾種:

(1)採用濾波元件,如共模電感、X1和Y1電容,X1電容用於輸入線間濾波, Y1電容在電路發生故障時只會斷路而不會短路,因此常用於初次級電路;

(2)在變壓器內部加禁止繞組,外包禁止銅帶,並將磁芯接地;

(3)在高頻開關(MOSFET和次級整流二極體)上加Snubber電路,以減小 和

和 ;

;

(4)通過完善PCB設計來減小高頻電流迴路的面積,對高頻元件採用Kelvin接法等。

這些方法可以有效地抑制電磁干擾,但每種方法都有其局限性,採用共模電感、X1和Y1電容的方法將受到體積、成本的制約;變壓器抗干擾技術要增加變壓器的繞制難度,絕緣也要十分小心;高頻開關上加Snubber電路會降低電源的效率,並增加高頻開關的損耗;而PCB設計需要豐富的經驗,並要考慮到方便產品製造(如機插元件要求水平布置等)。相比之下,頻率抖動技術採用功率半導體集成晶片的內部電路來改善EMI,高效且可靠,使用中不依靠電源設計人員的經驗,無需增加體積並能節省外圍元件的成本,也不會對電源的效率帶來任何負面影響,更不會給電源產品的製造增加任何不便。