閾值電壓 (Threshold voltage):通常將傳輸特性曲線中輸出電流隨輸入電壓改變而急劇變化轉折區的中點對應的輸入電壓稱為閾值電壓.在描述不同的器件時具有不同的參數。如描述場發射的特性時,電流達到10mA時的電壓被稱為閾值電壓。

基本介紹

- 中文名:閾值電壓

- 外文名:The threshold voltage

- 性質:專業術語

- 領域:物理學

概述

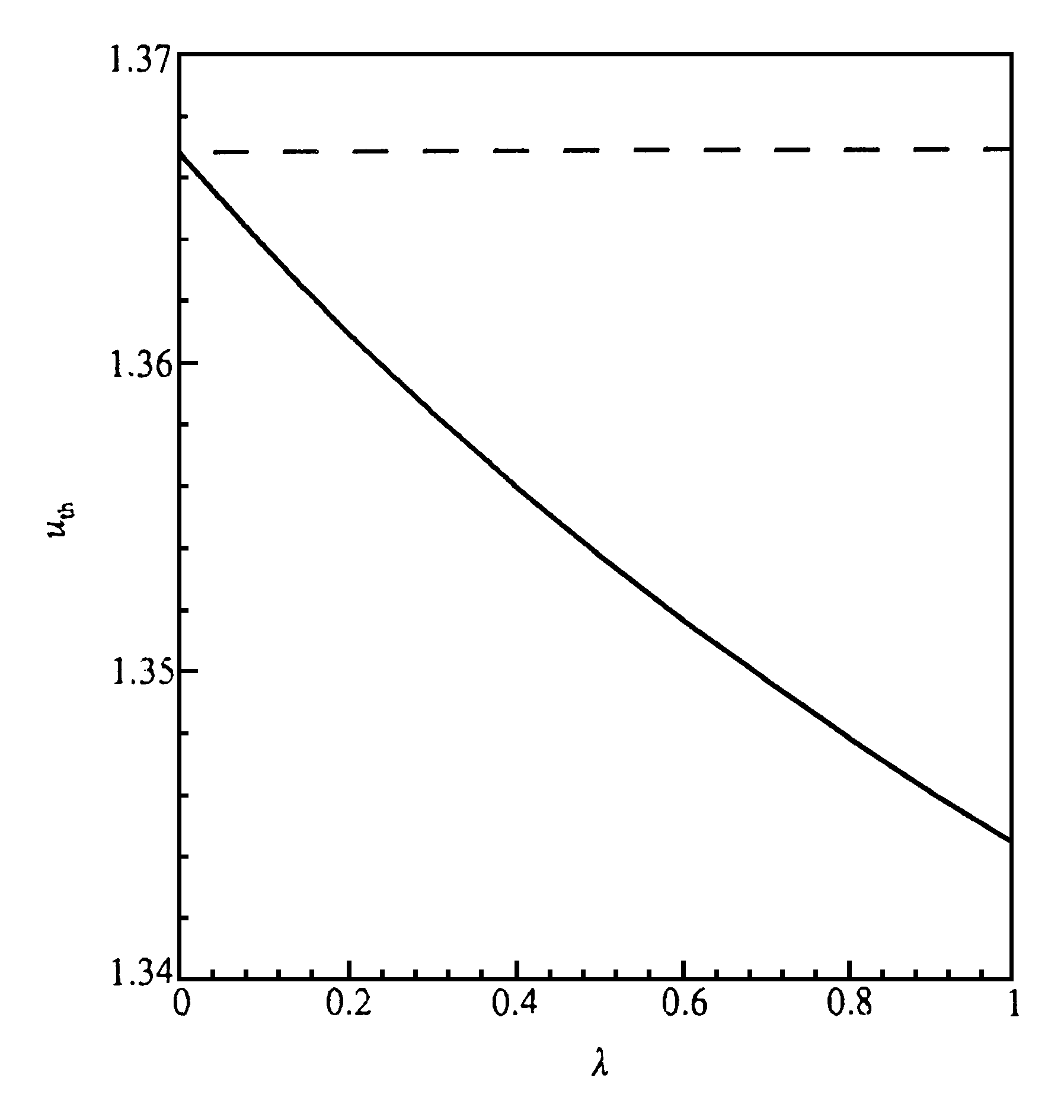

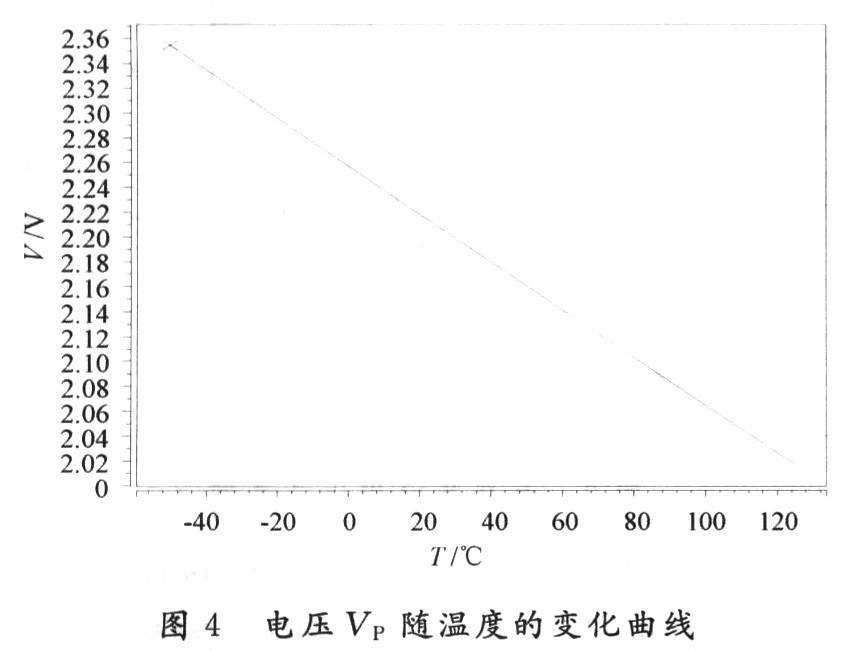

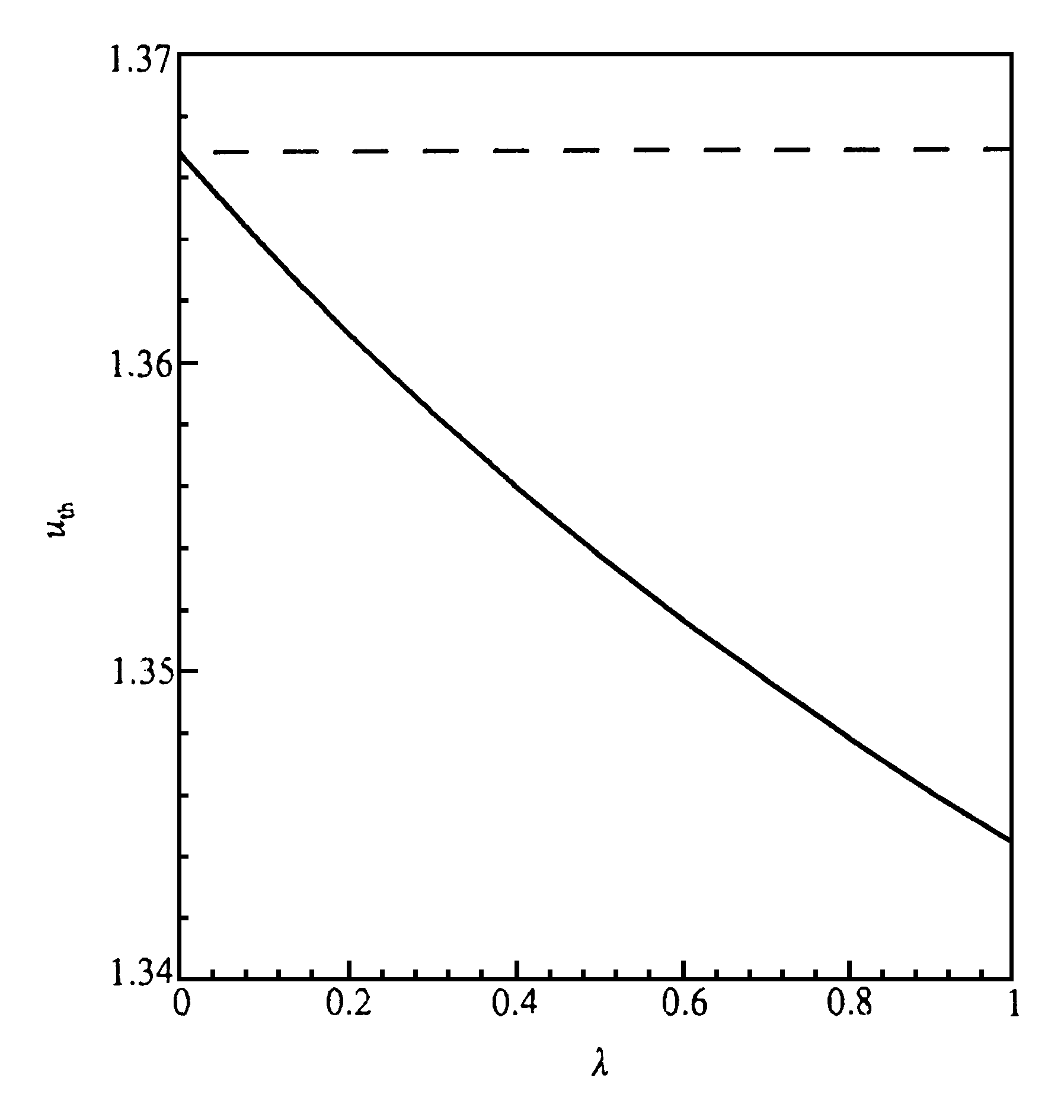

閾值電壓相關的學術圖片

閾值電壓相關的學術圖片影響因素

背柵的摻雜

閾值電壓 (Threshold voltage):通常將傳輸特性曲線中輸出電流隨輸入電壓改變而急劇變化轉折區的中點對應的輸入電壓稱為閾值電壓.在描述不同的器件時具有不同的參數。如描述場發射的特性時,電流達到10mA時的電壓被稱為閾值電壓。

閾值電壓相關的學術圖片

閾值電壓相關的學術圖片

閾值電壓 (Threshold voltage):通常將傳輸特性曲線中輸出電壓隨輸入電壓改變而急劇變化轉折區的中點對應的輸入電壓稱為閾值電壓.在描述不同的器件時具有不同的參數。...

耗盡型JFET的溝道摻雜濃度越高, 原始溝道越寬,則夾斷電壓就越高;溫度升高時,由於本徵載流子濃度的提高和柵結內建電勢的減小, 則夾斷電壓降低。...

電能表能夠啟動工作的最低電壓,此值為參比電壓下限(對寬量程的電能表此值為參比電壓下限)的60%。電能表的啟動工作是指電能表正常計量、顯示和記錄事件等,設計的...

閾值損失,在源-漏之間加有大小等於Vt的一個電壓時,通過器件的電流為0。這也就是MOSFET二極體用作為門電路有源負載時將會產生閾值損失的根源。...

高閾值邏輯電路是由二極體-電晶體邏輯電路 (DTL)和改進型二極體-電晶體邏輯電路(M-DTL)改進而來的一種高閾值雙極型中、低速數字積體電路,簡稱HTL電路。HTL電路的...

臨界轉換電壓上升率是驅動高電抗性的負載時,負載電壓和電流的波形間通常發生實質性的相位移動。...

亞閾值電流是在MOS管理想的電流-電壓特性中,當Vgs小於 Vt 時,漏極電流 Id 為0。...... 是金屬氧化物半導體場效應管柵極電壓低於電晶體線性導通所需的閾值電壓...

平帶電壓(Flat band voltage)就是在MOS系統中,使半導體表面能帶拉平(呈平帶狀態)所需要外加的電壓。...

《多電壓CMOS電路設計》是2008年機械工業出版社出版的圖書,作者是(土耳其)庫遜。...... 輸入電壓降壓型DC-DC變換器、多電源電壓積體電路內的信號傳輸、可變閾值電壓...

關斷電壓:通常將傳輸特性曲線中輸出電壓隨輸入電壓改變由急劇變化轉折區的終點到平穩低值對應的輸入電壓稱為關斷電壓.。...

·開啟電壓(又稱閾值電壓):使得源極S和漏極D之間開始形成導電溝道所需的柵極電壓;·標準的N溝道MOS管,VT約為3~6V;·通過工藝上的改進,可以使MOS管的VT值...

第一個影響閾值電壓的因素是作為介質的二氧化矽(柵氧化層)中的電荷Qss以及電荷的性質。這種電荷通常是由多種原因產生的,其中的一部分帶正電,一部分帶負電,其淨...

與一般觸發器不同的是,施密特觸發器採用電位觸發方式,其狀態由輸入信號電位維持;對於負向遞減和正向遞增兩種不同變化方向的輸入信號,施密特觸發器有不同的閾值電壓。...

閾值電壓負向漂移 目錄 1 基本概念和機理 2 NBTI效應的影響 ▪ 對器件 ▪ 對電路 負偏壓溫度不穩定性(NBTI:Negative Bias Temperature Instability)NBTI...

開態電阻,Rds(on):2ohm 工作溫度範圍:-65°Cto+150°C 封裝類型:SOT-23 電晶體類型:Enhancement 電壓Vgs@Rdson測量:10V 電壓,Vds典型值:60V 電流,Id連續:...