基本介紹

- 中文名:記憶單元

- 外文名:memory unit

- 定義:構成存儲器的基本成分

- 屬於:存儲器

- 組成:內部存儲和時序訪問控制

- 學科:計算機原理

概述

分類

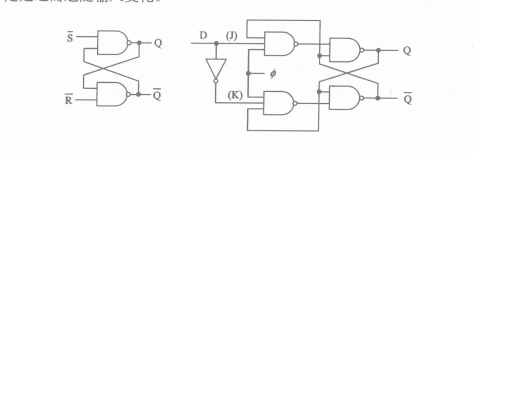

圖1

圖1

圖1

圖1

記憶單元是構成存儲器的基本成分,它可由各種材料製作,但只有滿足下列要求的媒體才有可能被選作記憶單元的材料。...

遵循艾賓浩斯遺忘曲線所揭示的記憶規律,對所學知識及時進行複習,這種記憶方法即為...③單元測驗:一個單元學完了,可以自測一下這個單元有哪些主要內容,學完有什麼收穫...

Memory是一個英語單詞,發音是英 'meməri 美 'mεməri ,詞性為名詞,意思有記憶;記憶力、記憶範圍、紀念等。 另音樂劇《貓》中有同名歌曲Memory。...

《記憶力訓練》指的是是一系列關於記憶力鍛鍊的DVD,主講人是謝華,記憶力是識記、保持、再認識和重現客觀事物所反映的內容和經驗的能力。...

記憶體實際上就是我們平時所說的存儲器,一般分為:固定不可擦的存儲器和易失性存儲器。 固定不可擦的存儲器:上面的信息一旦固化之後是固定不變,始終存在的,即使...

翻譯記憶(亦稱翻譯記憶體、翻譯記憶庫,translation memory,縮寫為TM)是電腦程式軟體的資料庫,用來輔助人工翻譯。有些使用翻譯記憶庫的軟體也常被稱為 TMM (Translation...

遺忘曲線是由德國心理學家艾賓浩斯(H.Ebbinghaus)研究發現,人體大腦對新事物遺忘的循序漸進的直觀描述,人們可以從遺忘曲線中掌握遺忘規律並加以利用,從而提升自我記憶...

大腦記憶密碼”終於被解開,在此項研究的所在地--華東師範大學腦功能基因組學重點實驗室,研究的主持者之一林龍年博士為記者詳細介紹了破譯“密碼”的全過程。...

記憶體單元一般採用半導體存儲單元,包括隨機存儲器(RAM),唯讀存儲器(ROM),以及高速快取(CACHE)。只不過因為RAM是其中最重要的存儲器。S(synchronous)DRAM 同步動態隨機...

記憶鞋墊又稱作慢回彈鞋墊;也就是人們常說的記憶棉(Memory Foam),是一種具有開放式單元結構(Open-cell)的聚氨酯高分子聚合物,該材料具有特殊的黏彈特性,體現很...

科學記憶是指人類基於生物學、心理學、人性學等認識記憶原理、遺忘規律,並在實踐基礎上得出的更快速、更有效的記憶方法。...

TM,即翻譯記憶,它是一個存儲了一個個“段”的資料庫,這些存儲了源文本和相應的語言的翻譯,這個“段”就是翻譯單元。翻譯記憶可以是用於幫助翻譯人員翻譯已翻譯的...

短期記憶(英語:Short-term memory)是記憶的一種類型。與長期記憶相比,短期記憶對信息的儲存時間較短,信息儲存的容量也很有限。...

單詞記憶方法,顧名思義就是記憶單詞的方法。採用五種主流記憶法把高中各單元單詞逐一進行修飾和加工,令學生達到舉一反三、事半功倍的單詞記憶效果,使記憶單詞效率...

記憶式鍵入,指當用戶在Word文檔中輸入自動圖文集中所包含詞條的前幾個字元時,Word會顯示建議提示,用戶可以根據需要輸入建議的詞條。...

聯想記憶是記憶的一種形式。通過與其他的知識單元的聯繫進行的記憶。相互之間存在聯繫的形式或概念構成知識在記憶中的具體形態。有兩個特點:一般是一對多的聯合關係...

長短期記憶人工神經網路是一種時間遞歸神經網路,是為了解決長期以來問題而專門設計出來的,所有的RNN都具有一種重複神經網路模組的鏈式形式。在標準RNN中,這個重複的...

《巧妙記憶》是2010年北京師範大學出版集團,北京師範大學出版社出版的圖書,作者是劉儒德。...

背誦(recitation)是通過誦讀的方式記住識記的閱讀材料。中國傳統語文學習方法之一。其主要方法有比較法、歸類法、熟記法、強記法、對比識記法、規律識記法、讀寫記憶...

存儲器(Memory)是現代信息技術中用於保存信息的記憶設備。其概念很廣,有很多層次,在數字系統中,只要能保存二進制數據的都可以是存儲器;在積體電路中,一個沒有實物...

上述的艾賓浩斯記憶曲線是艾賓浩斯在實驗室中經過了大量測試後,產生了不同的記憶...d) 相當於每個list被分為12個小的單元,每個小的單元自成一個複習系統;每6個...