基本概念

網路處理器(Network Processor,簡稱NP),根據國際網路處理器會議(Network Processors Conference)的定義:網路處理器是一種可程式器件,它特定的套用於通信領域的各種任務,比如包處理、

協定分析、

路由查找、聲音/數據的匯聚、

防火牆、

QoS等。

網路協定處理器使用的協定多為TCP/IP協定,TCP/IP協定歷來是處理網路上數據傳輸的通用語言,IP協定是TCP/IP協定族中最核心的協定,所有的TCP,UDP,ICMP以及IGMP數據都以IP數據報格式傳輸,處理IP協定要耗費大量的CPU資源。

網路傳輸協定

TCP/IP協定歷來是處理網路上數據傳輸的通用語言,傳統的TCP/IP技術在處理數據傳輸的過程中採用軟體實現,需要占用大量的處理器資源。隨著網路技術的發展,網路頻寬平均每12個月就增長3倍,美國西蒙公司己

經第一個推出了支持lOG到桌面的布線系統。而且,10G BaseTIEEE標準的草案己經於2004年6月出台,最終發布時間預計為2006年6月。同期CPU的處理速度則遵循了摩爾定律即每18個月增長2倍。而基本上1Hz的處理器最多可以處理每秒1 bit數據傳送所產生的負載。實驗表明,在800Mbit/s的線速度下,1GHz的Pentium3處理器資源占用率為100%,2.4GHz的Pentium4處理器資源占用率為30%。很明顯CPU的性能己經日益跟不上網路技術的進步。今後網路運用的瓶頸不再是頻寬資源,而是主機CPU處理TCP/IP協定棧的能力。

IP協定是TCP/IP協定族中最核心的協定,所有的TCP,UDP,ICMP以及IGMP數據都以IP數據報格式傳輸,處理IP協定要耗費大量的CPU資源。為實現減輕處理器負荷、提高網路利用率的目的,可通過硬體卸載IP協定的部分任務。

網路協定處理器的結構和原理

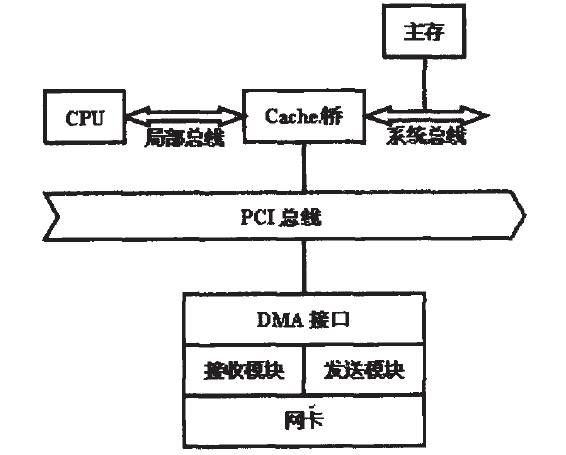

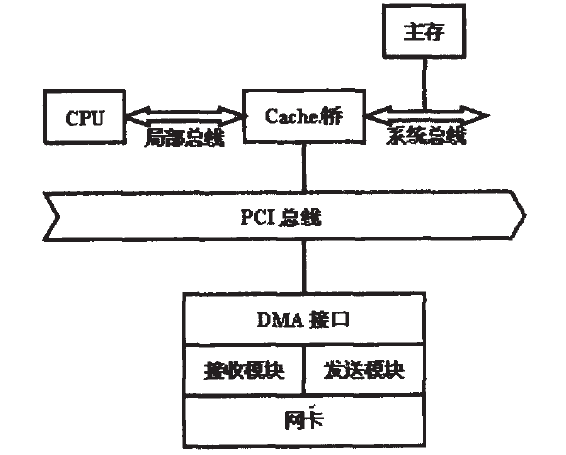

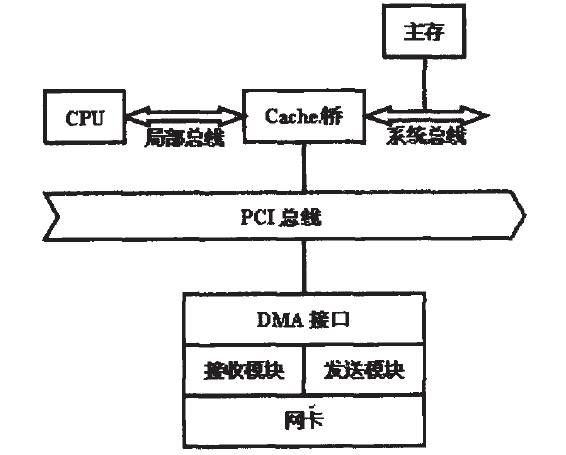

根據IP協定在TCP/IP協定棧分層中所處的位置,IP層協定處理器應包含3個模組:傳送端模組、接收端模組和DMA接口電路,如圖1所示。當主機傳送數據報時,數據經。MA接口到傳送端模組進行IP層協定處理再到網卡進行鏈路層協定處理,最後組裝為數據幀傳送到網路中。當主機接收到數據報時,數據依次經網卡、接收端模組、DMA接口,最終存入主存儲器中。下面詳細說明各組成部分的工作原理。

圖1

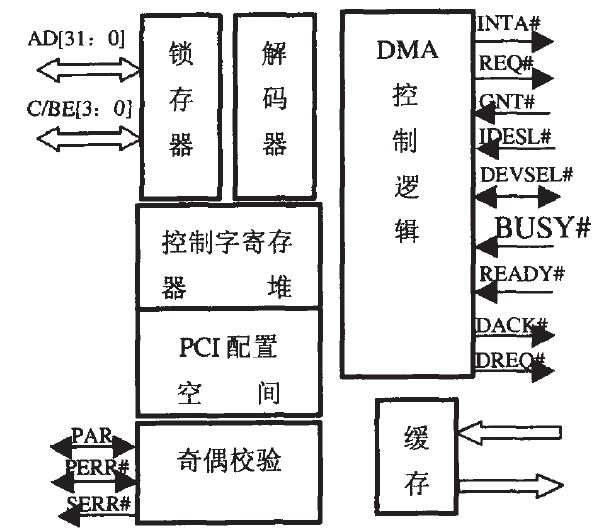

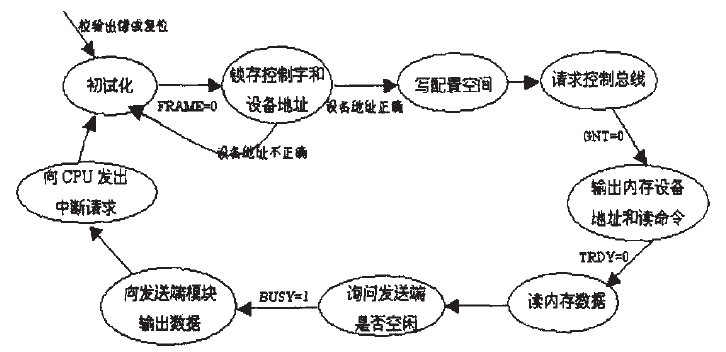

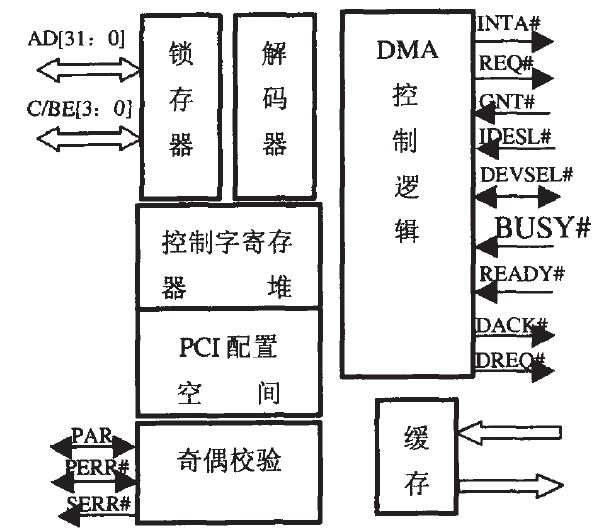

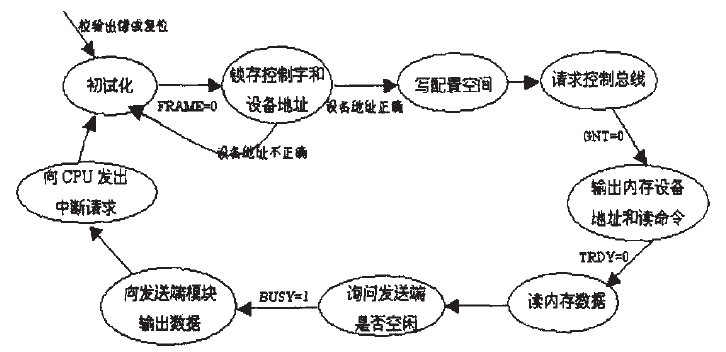

DMA方式,是一種由DMA控制器完成存儲器與外部設備或外部存儲器之間大量數據傳輸的方式。由於主存和。MA之間有一條數據通路,因此主存和設備交換信息時,不通過CPU,也不需要CPU暫停現行程式為設備服務,省去了保護現場和恢復現場。這一特點特別適合於高速I/O或輔存與主存之間的信息交換。PCI匯流排是32位並可升級到64位的獨立於CPU的處理匯流排,匯流排速度可達33/66MHz。通過將DMA邏輯和PCI接口規範緊密結合起來,構成一個靈活的基於PCI2.2規範的DMA接口電路,通過此接口電路,協定處理器可通過PCI匯流排與計算機記憶體直接交換數據。接口電路結構如圖2所示,圖中#號表示低電平有效。其工作流程分為讀、寫兩部分。圖3是

讀操作的流程圖,寫操作流程圖與之類似。

圖2

圖3

當進行讀操作時(即主機傳送數據報)依次進行以下操作:

(1)CPU通過PCI匯流排向DMA寫入控制字,此時DMA為從設備狀態,DMA接受到FRAME#信號後將輸入設備地址和控制字鎖存。

(2)判斷PCI匯流排所傳設備地址是否為協定處理器地址,若是,則進入數據傳輸狀態,將TRDY、DEVSEL信號置低電平,CPU所傳的控制信息(包括記憶體起始地址、位元組數、上層協定號、目的地址等)被寫入。MA配置暫存器中。若不是協定處理器地址,則不對其回響,返回初試狀態。

(3)控制字傳輸完後,DMA接口將REQ置低電平向匯流排請求控制權,此時。MA控制器為主設備狀態。

(4)當匯流排上GNT為低電平時表明。MA接口獲得匯流排控制權,DMA將FRAME置低電平,並傳送記憶體的設備地址和讀操作命令。

(5)記憶體準備好傳送數據後,匯流排發出TRDY#信號,DMA將數據讀入快取,此過程中若記憶體未準備好,TRDY為高電平,DMA控制器繼續等待。

(6)當DMA完成讀操作的前一個周期將FRAME置高電平,隨後一個周期後IRDY#也跳變為高電平,數據傳輸結束。

(7)DMA接口發出。REQ#信號詢問傳送端模組是否空閒,若傳送端模組空閒,則將快取中的數據以及位元組數、上層協定號,目的地址輸出給傳送端模組。

(8)快取數據空後,向CPU傳送中斷信號並返回空閒狀態。以上與匯流排進行數據交換的過程中,一旦出現奇偶校驗錯誤,則將PERK置低電平,並返回初始狀態,下同。

當進行寫操作時(即向主機傳送數據報)依次進行以下操作:

(1)接收端模組向DMA接口發請求。

(2)若DMA控制器處於空閒狀態,DMA接口將REQ置低電平向匯流排請求控制權。

(3)GNT為低電平表明DMA控制器獲得匯流排控制權,DMA將FRAME置低電平,並傳送記憶體設備地址和寫操作命令。

(4)記憶體準備好接受數據後,TRDY變為低電平,DMA將數據寫入主存中。此過程中若記憶體未準備好,TRDY為高電平,DMA控制器進入等待狀態。

(5)當DMA完成寫操作的前一個周期將FRAME置高電平,隨後一個周期後IRDY也變為高電平,數據傳輸結束。

(6)向CPU傳送中斷信號並返回空閒狀態。

以上兩個過程的最後,DMA都向CPU發出中斷請求,CPU接到中斷請求後,將進行一些後處理,包括:校驗送入主存的數據是否正確;決定是否繼續用DMA方式傳送其他數據塊,若繼續傳送,則又要對DMA接口些入信息字,若不需要傳送,則停止外設;測試在傳送過程中是否發生錯誤,若出錯,則轉錯誤診斷及處理錯誤程式。

嵌入式網路協定處理器

對於嵌入式網路協定處理器的研究,Intel公司專門投資支持全球100所大學進行協定處理器及其相關套用的研究,並每年召開一次Workshop進行交流與總結。同時,國外一些大公司推出了一系列的網路協定晶片產品,如Xilinx為65rim Virtex.5 LX和LXT FPGA平台增加三款新型小尺寸封裝器件,Virtex.5 LX20T將微控制器、波形發生器、網路協定以及其他功能整合在具有高性價比、高性能和低邏輯功耗的FPGA內。韓國WlZnet公司在2009年推出的固件網路協定晶片:W5100、W5300和W7100,該系列晶片將TCP/IP協定棧、乙太網MAC和PHY集成為一體,其中,W5100支持TCP,UDP,ICMP,IGMP,口v4,ARP,PPPoE,Ethemet等網路協定;支持4個獨立的Socket通信,內部16K位元組的傳送/接收緩衝區可快速進行數據交換,最大通信速率達到25Mbps;提供多種匯流排(兩種並行匯流排和SPI匯流排)接口方式。同年,德州儀器11推出了一款面向ZigBee RF4CE規範的RemoTI網路協定,包含11業界最佳的CC2530IEEE/802.15.4片上系統與軟體協定棧。