異步計數器是異步時序電路,其主要特點是內部各觸發器的時鐘脈衝端CP不全都連線在一起,因此各觸發器的翻轉時刻有先有後,其輸出可能會產生干擾毛刺現象,但其電路結構簡單。

基本介紹

- 中文名:異步計數器

- 外文名:ripple counter

- 亦稱:波紋計數器,行波計數器

- 缺點分類:工作速度慢

- 分類方法:計數器按計數脈衝的輸入方式

- 特點:各觸發器的翻轉時刻有先有後

異步二進制加法計數器

異步二進制減法計數器

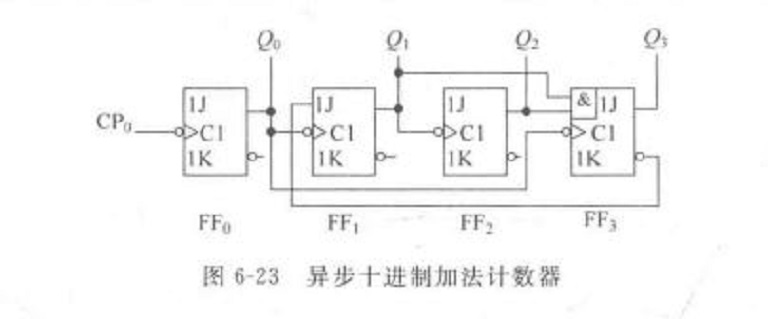

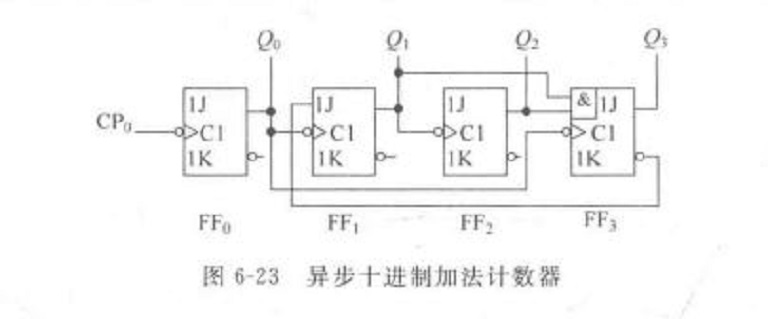

用JK觸發器構成的異步十進制計數器

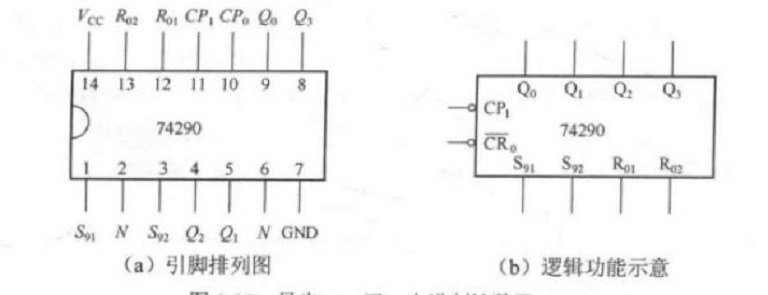

圖1

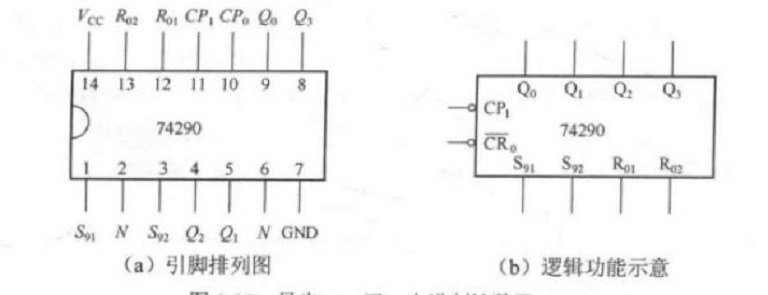

圖1引腳排列圖和邏輯功能

圖2

圖2

異步計數器是異步時序電路,其主要特點是內部各觸發器的時鐘脈衝端CP不全都連線在一起,因此各觸發器的翻轉時刻有先有後,其輸出可能會產生干擾毛刺現象,但其電路結構簡單。

圖1

圖1 圖2

圖2異步計數器是異步時序電路,其主要特點是內部各觸發器的時鐘脈衝端CP不全都連線在一起,因此各觸發器的翻轉時刻有先有後,其輸出可能會產生干擾毛刺現象,但其電路...

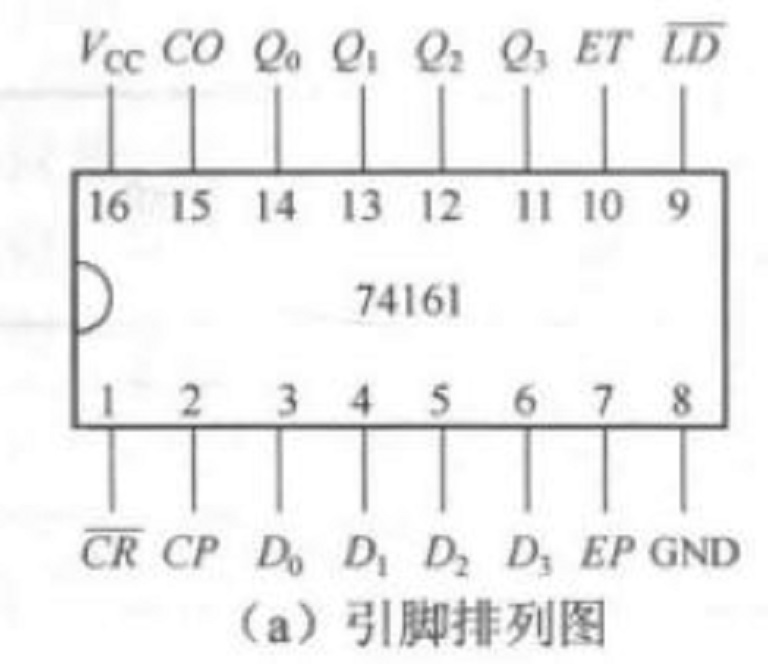

同步計數器指的是被測量累計值,其特點是大大提高了計數器工作頻率,相對應的是異步計數器。對於同步計數器,由於時鐘脈衝同時作用於各個觸發器,克服了異步觸發器所...

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈衝的個數,還可以實現分頻、定時、產生節拍脈衝和脈衝序列等。例如,計算機中的時序發生器、分頻器...

計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈衝的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,...

計數器是數字系統中用得較多的基本邏輯器件。計數器採用全自動貼片封裝工藝,具有很強的抗干擾能力,並具有多種輸出功能和控制功能,多種計數模式,廣泛運用於電力、...

既可加1計數又可減1計數的計數器叫做可逆計數器,也叫做雙向計數器。可逆計數器是可以進行正向和反向計數的計數器。這種計數器就是把加法計數器和減法計數器的作用...

6.6.5 深亞微米cmos電路的高容錯異步電路設計6.6.6 異步電路fpga設計技術6.7 小結第7章 異步電路設計舉例7.1 概述7.2 計數器...

《計數器分頻器鎖存器暫存器驅動器(分冊)》是2005年科學技術文獻出版社出版的圖書,作者是梁廷貴、王裕琛。...

中文名稱:計數器 英文名稱:counter 定義:通過傳動機構驅動計數元件,指示被測量累計值的器件。 套用學科:機械工程(一級學科);儀器儀表元件(二級學科);儀器儀表機械...

按計數增減可分為:加法計數器、減法計數器、加/減計數器,又稱可逆計數器。按計數器中觸發器翻轉是否同步可分為:異步計數器和同步計數器 [1] 。...

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或...

按計數增減可分為:加法計數器、減法計數器、加/減計數器,又稱可逆計數器。按計數器中觸發器翻轉是否同步可分為:異步計數器和同步計數器[1]。...

第八節 脈衝異步時序電路 本章小結 習題 第七章 常用時序邏輯部件 第一節 中規模同步集成計數器 第二節 中規模異步計數器 第三節 中規模暫存器與移位暫存器及其...

74LS193是同步四位二進制可逆計數器,它具有雙時鐘輸入,並具有異步清零和異步置數等功能。四位二進制可加減計數器74LS193引腳圖管腳及功能表。...

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。時序邏輯電路在邏輯功能上的...