基本介紹

- 中文名:時序邏輯系統

- 外文名:sequential logic system

- 學科:計算機科學與技術

- 類別:數字邏輯系統

- 分類:同步、異步

- 套用:計數器、暫存器

基本概念

時序邏輯電路

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。時序邏輯電路在邏輯功能上的...

由多個觸發器和多個組合邏輯塊組成的網路。常用的有:計數器、複雜的數據流動控制邏輯、運算控制邏輯、指令分析和操作控制邏輯。同步時序邏輯是設計複雜的數字邏輯系統...

行為時序邏輯(The Temporal Logic of Actions)是由萊斯利·蘭伯特(Leslie Lamport)發展的用於規範和推理並發自反應系統的時間邏輯。 主要套用於計算機科學,程式驗證。....

《時序邏輯程式設計與軟體工程(上冊)》是1999年科學出版社出版的圖書,作者是唐稚松。...

時序邏輯是指輸出不但和當前輸入的邏輯值有關,而且和在此以前曾經輸入過的邏輯值有關的邏輯系統。異步時序邏輯是電路的工作節奏不一致,不存在單一的主控時鐘,主要...

時序電路是計算機及其它電子系統中常用的一種電路。它和組合電路是完全不同的兩種類型電路。時序電路分為兩大類:同步時序邏輯電路和異步時序邏輯電路。在同步時序邏輯...

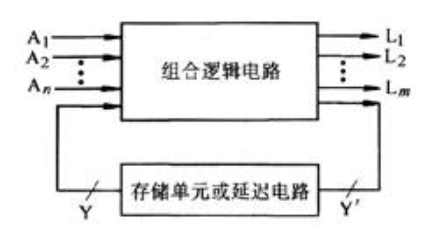

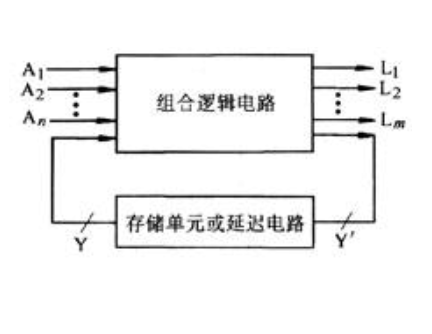

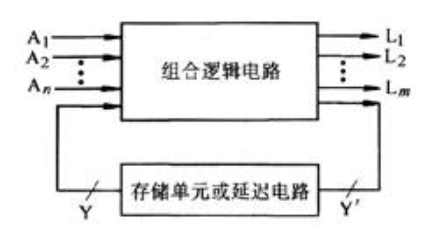

雖然每個數字電路系統可能包含有組合電路,但是在實際套用中絕大多數的系統還包括存儲元件,我們將這樣的系統描述為時序電路。時序電路,是由最基本的邏輯門電路加上反饋...

《邏輯設計與數字系統》是2005年清華大學出版社出版的圖書,作者是劉寶琴。...... 下冊,11-18章,主要內容有:電位型異步時序邏輯電路的分析與設計、運算電路、數字系...

一種典型的環形脈衝發生器及其解碼邏輯,它採用循環移位暫存器形式。 [2] 時序產生器時序產生器套用 編輯 時序產生器用於測試系統 基於向量測試法的測試系統的原理、...

邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”...

《邏輯與數學系統設計》是2008年清華大學出版社出版的圖書,作者是李晶皎。...... 組合邏輯電路、觸發器、時序邏輯電路、半導體存儲器、可程式邏輯器件、數字系統設計...

《數字邏輯電路與系統設計》是2008年07月電子工業出版社出版的圖書,作者是蔣立平。...... 《數字邏輯電路與系統設計》是2008年07月電子工業出版社出版的圖書,作者...

數字系統,是用數位訊號完成對數字量進行算術運算和邏輯運算的電路稱為數字電路,或數字系統。...

數字系統與邏輯設計是 北京航空航天大學出版社出版的一本圖書,作者馬金明...... 《數字系統與邏輯設計》全面系統地介紹數字...組合邏輯電路和時序邏輯電路的分析、設計...

《計算機系統原理》一書,從硬體和軟體兩個方面闡述計算機系統的工作原理,內容包括...2.3.3同步時序邏輯電路的分析2.3.4同步時序邏輯電路的設計習題...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

《數字邏輯電路與系統設計(第2版)》是2013年電子工業出版社出版的圖書,作者是蔣立平。...

《數字系統邏輯設計》對數字系統邏輯電路分析與設計的基本知識、基本理論和基本方法進行了系統介紹。針對各種不同規模的邏輯器件,舉例說明邏輯電路分析與設計的全過程。...

對象處理了這個事件、是否是期望的對象處理了這個事件、是否獲得期望的結果,同樣也無法控制事件發生的次序,系統的邏輯和時序的正確性必須通過複雜的時序邏輯和前後條件...