基本介紹

- 中文名:多路選擇器

- 外文名:multiplexers

多路選擇器分類

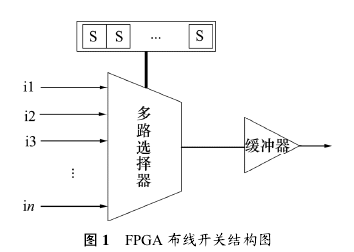

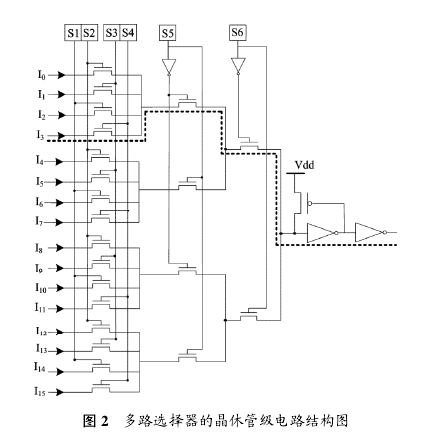

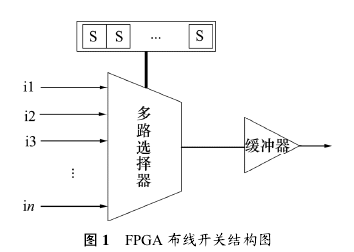

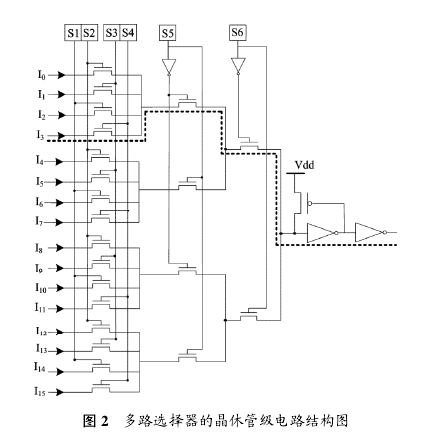

FPGA中多路選擇器結構

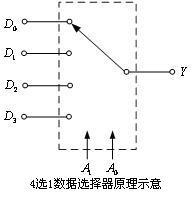

多路選擇器是數據選擇器的別稱。在多路數據傳送過程中,能夠根據需要將其中任意一路選出來的電路,叫做數據選擇器,也稱多路選擇器或多路開關。...

數據選擇器(data selector) 根據給定的輸入地址代碼,從一組輸入信號中選出指定的一個送至輸出端的組合邏輯電路。有時也把它叫做多路選擇器或多路調製器(...

在多路數據傳送過程中,能夠根據需要將其中任意一路選出來的電路,叫做數據選擇器,也稱多路選擇器或多路開關。 產品規格 有4選1數據選擇器、8選1數據選擇器(型號為...

通道價格昂貴,致使機器中所設定的通道數量勢必較少,一般一個通道通常連線多個外部設備,通道多路輸出選擇器是指通道中選擇器根據地址選擇一個設備進行I/O/操作。...

數據選擇器(data selector) 根據給定的輸入地址代碼,從一組輸入信號中選出指定的一個送至輸出端的組合邏輯電路。通道數據選擇器是指數據選擇器在通道所連線的設備...

雙RISC核子系統從PE陣列獲取圖像預處理結果並行進行高級圖像處理,並將處理結果通過多路選擇器MUX輸出。PE陣列控制器和雙RISC子系統之間能夠互相通信,實現PE陣列並行處理...

74HC4051是8通道模擬多路選擇器/多路分配器,帶有3個數字選擇端(S0至S2),1個低有效使能端(E),8個獨立輸入/輸出端(Y0至Y7)和1個公共輸入/輸出端(Z)。...

C8051F340/1/2/3/4/5/6/7系列器件使用Silicon Labs的專利CIP-51微控制器...F340/1/2/3/4/5/6/7內部有一個10位SAR ADC和一個差分輸入多路選擇器。...

OLMC中的四個多路選擇器分別是輸出數據選擇器OMUX、乘積項數據選擇器PTMUX、三態數據選擇器TSMUX和反饋數據選擇器FMUX,它們在控制信號AC(0)和AC1(n)的作用下,可...

4.8.2 C8051F31X的模/數轉換器1634.8.3 工作方式1654.8.4 模擬多路選擇器1674.8.5 可程式視窗檢測器1684.8.6 暫存器1714.8.7 模/數轉換實驗:A/D178...

這樣 ,多路選擇器可在前三個周期選擇輸入時鐘直接輸出 , 而在後兩個周期選擇輸出‘0’ ,就可以得到脈衝串“ 1010100000” , 從而完成 3 /5 倍的分頻 ,得到 ...

實戰項目6設計比較器電路3.2比較器電路3.2.1比較器設計3.2.2使用FPGAEditor查看細節實戰項目7設計多路選擇器電路3.3多路選擇器3.3.1多路選擇器設計...

除了12位的ADC子系統ADC0之外C8051F02x還有一個8位ADC子系統即ADC1它有一個8通道輸入多路選擇器和可程式增益放大器該ADC工作在500ksps的最大採樣速率時可提供...

這種設備把網橋、路由器和多路選擇器上的數據轉化到數字線路上使用的雙極性數位訊號。中繼器和電路驅動器在長途線路中出現的信號畸變可能使得數位訊號變得不可辨識。...

6.1.3多路選擇器和多路分配器6.1.4數值比較器6.1.5奇偶發生/校驗器6.2半導體存儲器6.2.1概述6.2.2隨機讀寫存儲器6.2.3隻讀存儲器6.3可程式邏輯器件...