並行處理器指可以一次可處理多個運算的處理器。雙核處理器也是並行處理器,因為其一次可運行兩個運算(以此類推),但其本質上還是串列處理器的組合,所以提起並行處理器,一般指經特殊設計的多執行緒處理器。

基本介紹

- 中文名:並行處理器

- 外文名:Parallel processor

- 簡稱:PP

- 學科:計算機科學與技術

- 特點:並行

- 優勢:速度快

基本概念,國內外並行處理器發展現狀,並行處理器結構,並行處理系統,並行處理器系統的種類,基於並行處理器的快速車道線檢測系統,

基本概念

數據處理已迅速普及到工業、商業和刷一會的各個領域,不過由於受到軟體發展的限制,還不能進一步發展。但是,在科學技術的套用上,計算機還有嚴重的缺點,即使是現有的大型計算機系統,在計算效率上還差幾個數量級。要想適應新的問題推的需要,使計算效率有根木的提高,那就只有呆用一種絕然不同的計算機體系結構,以擺脫指令和數據串列處理的“馮諾依曼瓶預”,當然還要改變現行的程式設計語言。計算機體系結構,如以並行處理原理為基礎,在結構上就具有把計算效率提高到必要量級的潛在可能性。

並行處理器指可以一次可處理多個運算的處理器。雙核處理器也是並行處理器,因為其一次可運行兩個運算(以此類推),但其本質上還是串列處理器的組合,所以提起並行處理器,一般指經特殊設計的多執行緒處理器。

國內外並行處理器發展現狀

Stanford大學的Imagine流處理器。它的主要計算結構為8個SIMD(Single Instruction Multiple Date)模式工作的處理單元簇。處理單元簇使用VLIW(Very Long Instruction word)方式控制,其特點是利用長指令對多個功能單元同時操作,達到並行的目的,VLIW有助於發掘ILP(Instruction Level Parallel)。另一方面,利用SIMD發掘DLP(Data Level Parallel)。 Imagine使用了3級存儲器層次結構,並在數據流控制上提出來流處理的概念,緩解了處理器對外存頻寬的依賴。

Motorola Labs主持研製的RSVP流處理器與Imagine有些區別。RSVP只有一組功能單元,每個功能單元64位,可以劃分為最多4個片(slice),每一組slice有自己的控制流,所以RSVP是一個MIMD(Multiple Instruction Multiple Date)結構。

國內的流處理器主要由國防科技大學研究。其提出了X流處理器,FT64和MASA。這3種流處理器結構類似,都是以Imagine為基礎加以改進的設計。其中MASA-I實現了與Imagine的指令兼容,而X流處理器、FT64實現了雙精度浮點科學運算。

GPU也是一種典型的並行處理器。在套用方面GPU偏重於數據並行和任務級並行,因此GPU中一般將8一16個處理單元組合成一個SIMD模組,每個處理單元包含1個或多個運算單元。整體採用多個這樣的SIMD模組組合成MIMD以更好地支持任務級並行。如NVIDIA的Fermi處理器,比起上一代的GT200系列處理器,Fermi採用了超標量的結構,一個時鐘可以向計算陣列發射2~4條指令,同時Fermi開始支持可讀寫的數據Cache。與NVIDIA不同,AMD的HD5000系列處理器沒有採用超標量的結構,而是採用了VLIW技術,最多可以同時在每個SIMD陣列執行5條指令。SIMD模組間通訊方式前者主要採用L2 Caehe或者片外存儲器,後者還可以使用一塊較小的全局片上存儲器通訊。通過對GPU的組織可以發現,本應注重數據級並行的GPU也開始使用一些CPU的技術來提高指令並行性和通用計算能力,進一步提升性能。

並行處理器結構

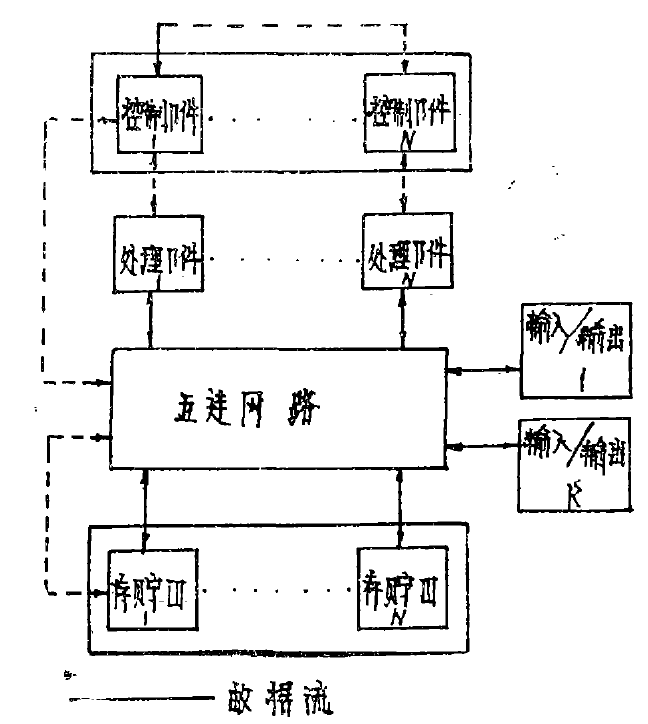

並行處理器結構圖如圖所示:

這種系統有N個處理部件(PE),M個主存存賒體(M個記憶體模組)和一些或者N個控制部件(CU)以及輸入/輸出通道;最重要的系統部件是互速網路,它可以使各個部件進行數據或按制信號方面的通信。

並行處理系統

所有的並行處理系統均可視為以處理器為節點的網路。設計並行處理時必須考慮許多問題,其中的兩個重要問題是處理系統的網路拓撲結構和節點處理器的設計。高速數位訊號處動系蛛屬於專用機,其拓撲結構和節點設計與所要實現的算法有密切的關係,且對其通用性不需要而且也不應該有很高的要求(通用機有很高的通用性,但相應地有很大的管現開銷)。良好的專用並行處理系統應具有如下一些共同特點。

(1)模組化處理系統由種類不多的模組組成。這既便於節點及通訊硬軟體設計,又便子系統的擴展,而且也降低了系統的複雜性;

(2)流水處理這可以大大提高處理速度,是並行系統必須具有的特點之一;

(3)局域性這包括局域的數據流和控制流。由於無論在晶片級還是系統級,通訊問題均是關鍵,因而局域性非常重要。

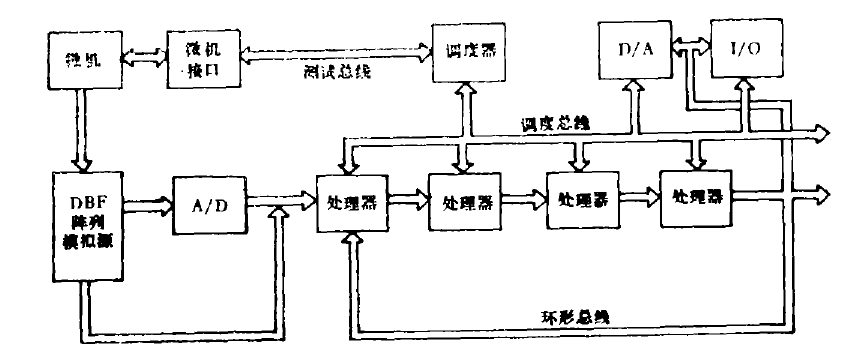

並行處理系統的框圖如圖:

處理系統的中心部分由一個調度器及四個處理器組成,系統設計成可以很易擴展其處理器的數量,系統還包含A/D、D/A及串口和並口。系統的重構通過對調度器和其它處理器的軟體設定實現。系統可設定成線性、環形、星形、車輪形等各種結構形式,以適於多種套用。

調度器亦是一個處理器,用於系統的調度和控制,也可完成一定的處理運算。它主要用於向處理器發出各種控制命令,控制調度匯流排的復用,轉發微機和各處理器之間的控制和數據。所有程式和初始數據均由微機產生,再經由調度器轉至各處理器。要顯示列印的結果亦由調度器轉至微機。

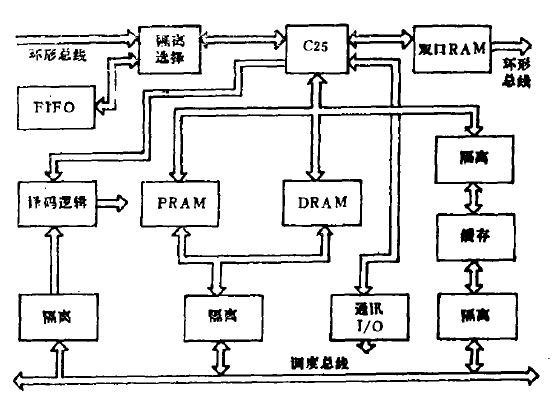

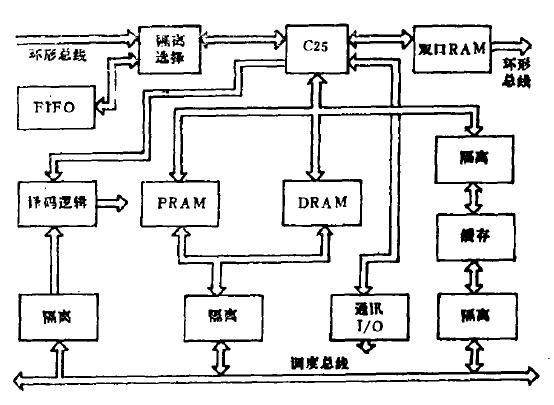

系統的運算主要由處理器完成。現系統有 個接水上一樣的處理器,只是在第一個處理器中加入FIFO,用於作為輸入數據通道。處理器的組成如圖:

系統共有三種匯流排: 測試匯流排、調度匯流排和環形匯流排。測試匯流排用於傳輸微機和處理系統間的數據、微機向處理系統傳送程式、初始化信息及控制命令;調度匯流排完成調度器和其餘處理器的信息傳輸;環形匯流排將四個處理器連線成環形結構。

並行處理器是實時實現許多需要完成複雜計算(如矩陣計算)的數位訊號處理系統的不可避免的選擇。

並行處理器系統的種類

如果按性質來進行分類,則有些處理器是模凌兩可的:既可算作這一類,又可算作另一類;按照費林的意見,又可分為單指命流多數據流系統和多指令流多數據流系統。這裡列出的只是一些重要的應算作並行處理器的系統:

(1)向量/流水線處理器:

STAR-100(CDC公司)

CYBER 203/205(CDC公司)

T1-ASC(德克薩斯儀表公司)

Cray-1(克雷研究公司)

(2)並行處理器系統

ILLIAC IV(依里諾斯大學,布勞斯公司)

SOLOMOM(西屋公司)

PEPE(貝爾實驗室、布勞斯公司系統發展公司)

BSP(布勞斯公司)

DAP(ICL公司)

CHOPP(哥倫比亞大學;蘇里萬學會)

C.mmp.Cm(卡內其/梅隆大學)

T16(Tandem公司)

EGPA(埃爾朗根/諾爾貝爾格大學)

(3)相聯處理器

STARAN(古得依爾宇航公司)

ECAM(霍尼威爾公司)

OMEN(商特爾公司)

ALAP(休斯飛機公司)

(4)算法數組處理器(流水線計算機)

IBM 2938/3835(IBM公司)

MAP III(數據控制公司)

UAP(尤尼瓦克公司)

AP-120B/190L(浮點系統公司)

FPS-164(浮點系統公司)

ATP(Datawest公司)

基於並行處理器的快速車道線檢測系統

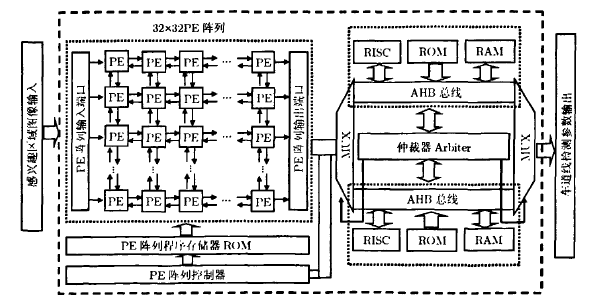

如圖為本文提出的並行快速車道線檢測片上系統的構架圖。

它包含一個32X32的PE陣列、陣列程式存儲器ROM和陣列控制器、雙RISC核子系統、仲裁器和多路選擇器MUX等模組。PE陣列包含有陣列輸入和輸出連線埠。整個陣列構成一個並行單指令多數據(SIMD)系統,在陣列控制器的控制下,通過陣列程式存儲器ROM供給指令,實現各種圖像並行預處理。雙RISC核子系統則有兩個RISC處理器及相應的指令存儲器ROM和數據存儲器RAM構成,它們通過AHB匯流排互聯。雙RISC核通過仲裁器控制多路選擇器MUX,實現和PE陣列以及外部的互連。雙RISC核子系統從PE陣列獲取圖像預處理結果並行進行高級圖像處理,並將處理結果通過多路選擇器MUX輸出。PE陣列控制器和雙RISC子系統之間能夠互相通信,實現PE陣列並行處理和雙RISC核並行處理之間的同步,從而使整個系統協調一致工作。

這個系統充分考慮檢測過程圖像處理的並行特徵。基於圖像處理的檢測過程,包含有大數據量低複雜度的圖像預處理和小數據量高複雜度的高級圖像處理。圖像預處理是由整塊圖像所有像素共同參與的過程,呈現出數據量的龐大,而每個像素的處理僅僅是和相鄰像素之間按一定權重因子的加減運算,屬於低複雜度的局部運算。因而圖像預處理是一個適合於2維並行的處理。本系統中,採用PE陣列的2維並行結構來實現圖像的預處理,從而顯著提高圖像預處理的速度。而高級圖像處理實現檢測的過程,是基於預處理結果獲取的特徵信息,因而數據量大為減小,且數據量之間相關性不大,需要做各種變換,涉及多次的乘法,查詢,統計,排序等。