同或門(英語:XNOR gate或equivalence gate)也稱為異或非門,是數字邏輯電路的基本單元,有2個輸入端、1個輸出端。當2個輸入端中有且只有一個是低電平(邏輯0)時,輸出為低電平。亦即當輸入電平相同時,輸出為高電平(邏輯1)。

基本介紹

- 中文名:同或門

- 外文名:equivalence gate

- 別名:異或非門

- 說明 :是數字邏輯電路的基本單元

基本信息,實現,符號,積體電路,

同或門(英語:XNOR gate或equivalence gate)也稱為異或非門,是數字邏輯電路的基本單元,有2個輸入端、1個輸出端。當2個輸入端中有且只有一個是低電平(邏輯0)時,輸出為低電平。亦即當輸入電平相同時,輸出為高電平(邏輯1)。

同或門(英語:XNOR gate或equivalence gate)也稱為異或非門,是數字邏輯電路的基本單元,有2個輸入端、1個輸出端。當2個輸入端中有且只有一個是低電平(邏輯0)時...

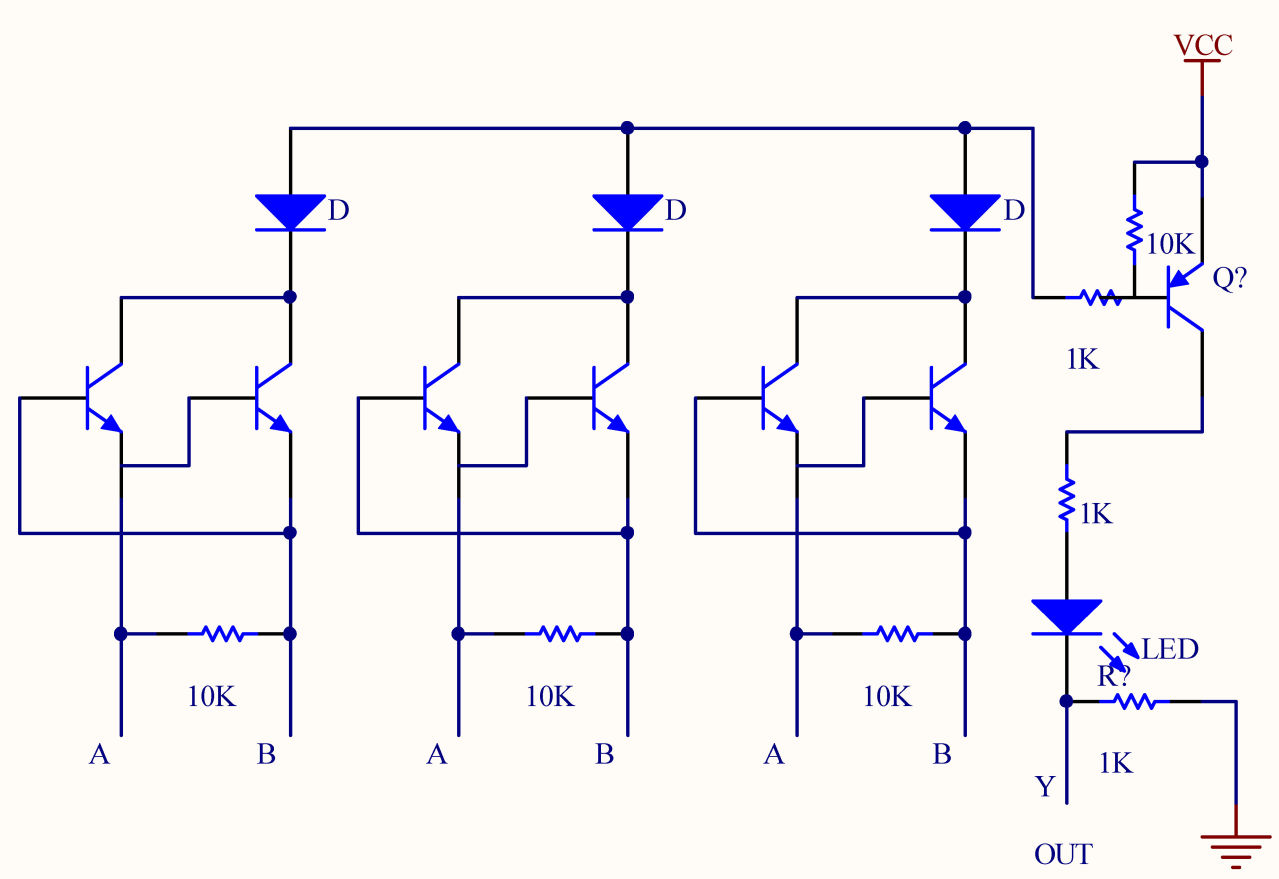

同或門: 與異或門相反。 輸入相同時輸出為高, 否則為低。 AB + A'B' 輸入 A B 0 0 0 1 1 0 1 1 輸出 AxnorB 1 0 0 1 邏輯...

在異或門的輸出端或者其中一個輸入端加非門,可以很方便的等效實現同或門。方案A為純火把設計。如果不需要外部輸入端,朝後的兩個火把可以用拉桿代替,即方案B。方案...

彙編語言和VHDL語言中的同或。用於單片機C51、FPGA等開發板中。電路表示則為同或門,雙輸入若相同則輸出為1,不同則輸出為0! 例如:1 xnor 1=1;1 xnor 0=0;...