二極體邏輯電路(Diode logic circuit)是用晶體二極體作為操作開關的邏輯電路。二極體邏輯電路優點是電路形式簡單,工作電壓範圍不受限制,但二極體邏輯電路中只有邏輯與門,或門,不能實現非門。

基本介紹

- 中文名:二極體邏輯電路

- 外文名:diode logical circuit

- 學科:計算機科學與技術

- 類別:邏輯電路

- 優勢:電路簡單

- 缺點:不能實現“非”邏輯

基本概念,二極體的工作原理,P-N結的單嚮導電性,二極體的單嚮導電性,二極體邏輯電路,二極體與門電路,二極體或門電路,三種邏輯電路的比較,

基本概念

二極體邏輯電路(Diode logic circuit)是用晶體二極體作為操作開關的邏輯電路。二極體邏輯的優點是電路簡單。但是並不是所有的邏輯功能都可以用二極體邏輯來實現的,二極體邏輯電路中只有邏輯與門,或門,不能實現非門。在幾個二極體邏輯電路級聯的時候會出現電壓降的問題,所以二極體邏輯電路只能單獨使用,不能級聯。二極體邏輯的使用:二極體邏輯一般是用於構建二極體—電晶體邏輯(DTL)門電路中。

二極體的工作原理

P-N結的單嚮導電性

利用二極體實現邏輯電路主要是利用了二極體的單嚮導電性,二極體之所以具有單嚮導電性,是因為製作二極體的半導體中P-N結的作用,下面首先對P-N結做一些介紹。

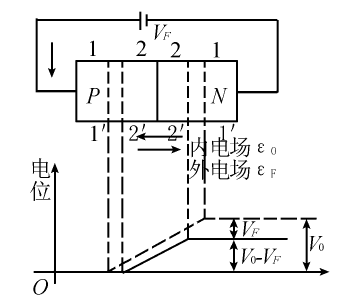

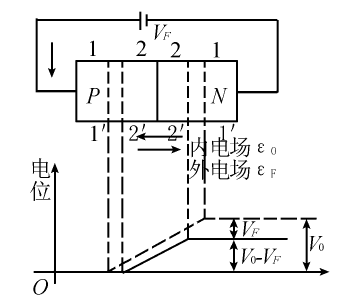

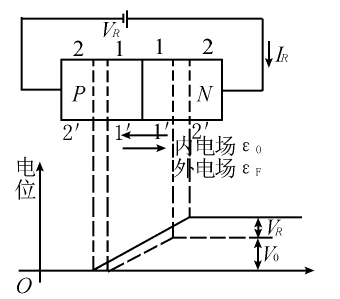

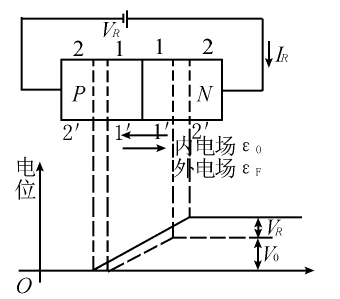

P-N結是在一塊半導體中,摻入施主(如矽元素)雜質,使其中一部分成為N型半導體。其餘部分摻入受主雜質(如硼元素)而成為P型半導體,當P型半導體和N型半導體這兩個區域共處一體時,這兩個區域之間的交界層就是P-N結。P-N結很薄,結中電子和空穴都很少,但在靠近N型一邊有帶正電荷的離子,靠近P型一邊有帶負電荷的離子。這是因為,在P型區中空穴的濃度大,在N型區中電子的濃度大,所以把它們結合在一起時,在它們交界的地方便要發生電子和空穴的擴散運動.由於P區有大量可以移動的空穴,N區幾乎沒有空穴,空穴就要由P區向N區擴散。同樣N區有大量的自由電子,P區幾乎沒有電子,所以電子就要由N區向P區擴散.隨著擴散的進行,P區空穴減少,出現了一層帶負電的粒子區;N區電子減少,出現了一層帶正電的粒子區。結果在P-N結的邊界附近形成了一個空間電荷區,P型區一邊帶負電荷的離子,N型區一邊帶正電荷的離子,因而在結中形成了很強的局部電場,方向由N區指向P區。當結上加正向電壓(即P區加電源正極,N區加電源負極如圖1)時,這時電場減弱,N區中的電子和P區中的空穴都容易通過,因而電流較大;當外加電壓相反(圖2)時,則這時電場增強,只有原N區中的少數空穴和P區中的少數電子能夠通過,因而電流很小。這就是P-N結的單嚮導電性。

圖1

圖2

二極體的單嚮導電性

二極體多用半導體材料製成,由於其中P-N結單嚮導電性的作用,故二極體具有單嚮導電性。

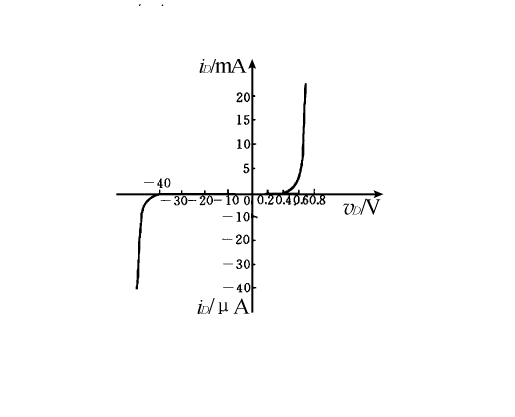

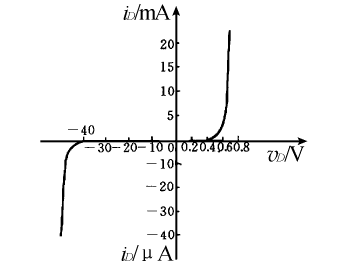

(1)正向特性

在電子電路中,將二極體的正極接在高電位端,負極接在低電位端,二極體就會導通,這種連線方式,稱為正向偏置。導通後二極體兩端的電壓基本上保持不變(鍺管約為 0.3V,矽管約為 0.7V),稱為二極體的“正向壓降”。二極體正嚮導通電壓很低與高電壓相比可以近似認為為零。如圖6。

(2)反向特性

在電子電路中,二極體的正極接在低電位端,負極接在高電位端,此時二極體中幾乎沒有電流流過,此時二極體處於截止狀態,這種連線方式,稱為反向偏置。

二極體邏輯電路

二極體與門電路

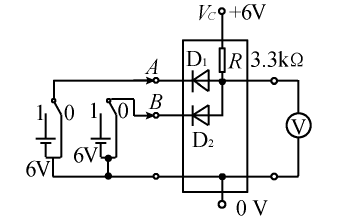

如圖,若輸入端中有任意一個例如 為0V,

為0V, 為+6 V,在這種情況下,D1導通,使Y點電壓鉗制在0V。此時D2受反向電壓作用而截止,所以

為+6 V,在這種情況下,D1導通,使Y點電壓鉗制在0V。此時D2受反向電壓作用而截止,所以 。由此可見,與門幾個輸入端中,只有加低電壓輸入的二極體才導通,並把Y鉗制在低電壓(接近0V),而加高電壓輸入的二極體都截止。

。由此可見,與門幾個輸入端中,只有加低電壓輸入的二極體才導通,並把Y鉗制在低電壓(接近0V),而加高電壓輸入的二極體都截止。

若輸入端A,B都處於高電壓+6V,這時,D1和D2都截止,所以輸出端Y點電壓 與+

與+ 相等,即

相等,即 =+6V。

=+6V。

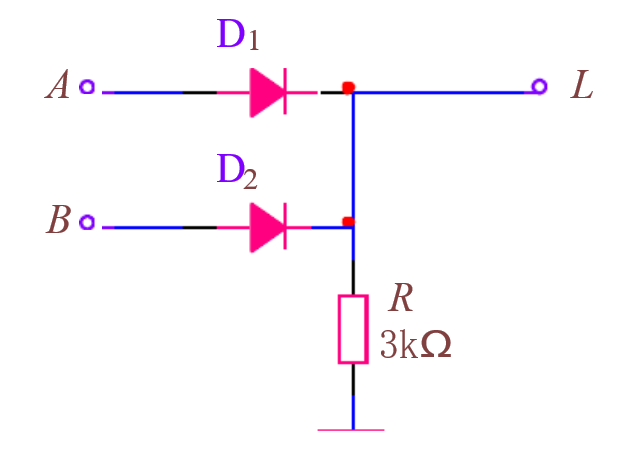

二極體或門電路

或門電路為:

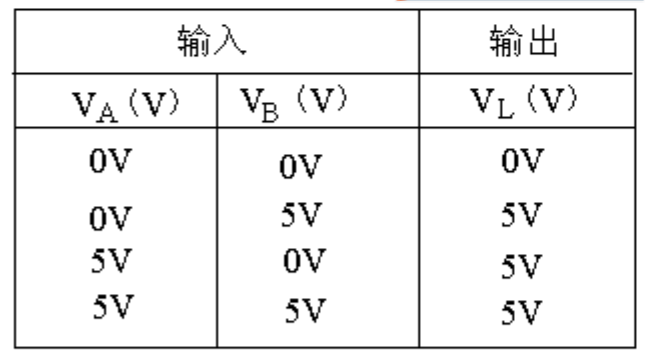

輸入與輸出電壓之間的關係表為:

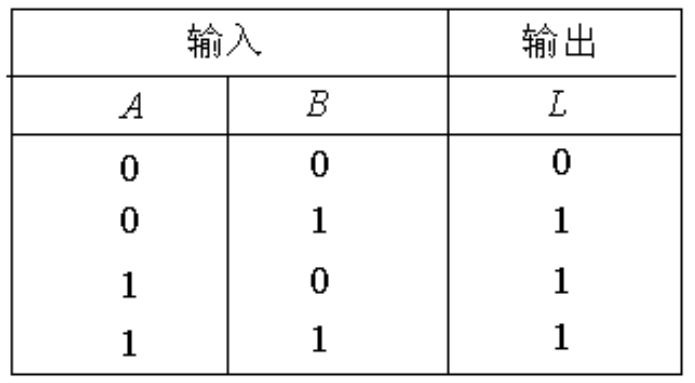

從而得出或門邏輯真值表為:

三種邏輯電路的比較

隨著現代科技的發展,人們的生活已經離不開數字電路。邏輯門電路是數字電路中最基本的邏輯元件。所謂門就是一種開關,它能按照一定的條件去控制信號的通過或不通過。門電路的輸入和輸出之間存在一定的邏輯關係(因果關係),所以門電路又稱為邏輯門電路。基本邏輯關係為“與”、“或”、“非”三種。常用的有CMOS邏輯,TTL邏輯和二極體邏輯,下面是三種邏輯的比較:

(1)二極體邏輯電路優點是電路形式簡單,工作電壓範圍不受限制,用開關管或超快恢復二極體、肖特基二極體可以達到較高的速度,但驅動能力相對較弱,功耗相對較大,輸入阻抗相對較低,綜合起來造成扇出係數很低。並且由於不能實現邏輯非門,不能級聯,二極體邏輯的使用是很受限制的。

(2)TTL邏輯電路缺點是電路形式比二極體邏輯電路要複雜,工作電壓範圍較窄,輸入阻抗高於二極體邏輯電路但不如CMOS邏輯電路,功耗略大,優點是速度較高,驅動能力也較強,綜合起來扇出係數中等。

(3)CMOS邏輯電路缺點是電路形式比二極體邏輯電路要複雜,工作電壓範圍寬於TTL邏輯電路但明顯小於二極體邏輯電路,優點是速度較高,驅動能力也較強,而且輸入阻抗極高,綜合起來扇出係數最大。CMOS比TTL的噪聲容限更大,抗干擾能力,驅動負載能力更強。正由於這些優點,CMOS的使用占據了主導地位。