主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,

| 中文名稱 | 主時鐘 |

| 英文名稱 | master clock |

| 定 義 | 用於控制其他時鐘頻率的時鐘。 |

| 套用學科 | 通信科技(一級學科),支撐網路(二級學科) |

基本介紹

- 中文名:主時鐘

- 外文名:master clock

- 定義:用於控制其他時鐘頻率的時鐘。

- 套用學科:通信科技,支撐網路

定義

最佳主時鐘算法

系統主時鐘

組成單元

時鐘源的選擇

鎖相環

主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,

| 中文名稱 | 主時鐘 |

| 英文名稱 | master clock |

| 定 義 | 用於控制其他時鐘頻率的時鐘。 |

| 套用學科 | 通信科技(一級學科),支撐網路(二級學科) |

主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,...

時鐘頻率(又譯:時鐘頻率速度,英語:clock rate),是指同步電路中時鐘的基礎頻率,它以“若干次周期每秒”來度量,量度單位採用SI單位赫茲(Hz)。它是評定CPU性能的...

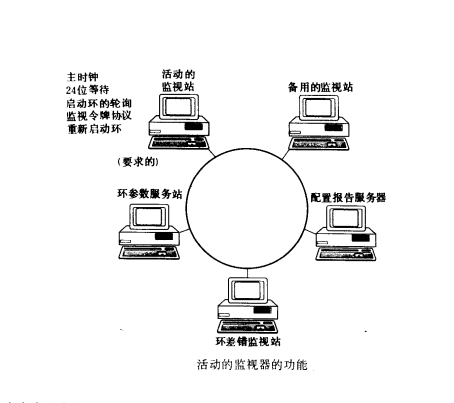

精確時鐘同步協定(IEEE1588)是關於網路測量和控制系統的時間協定,可達到較高的網路對時精度,實現高精度的時間同步。最佳主時鐘算法(BMC)是IEEE1588的最主要的核心...

《主題時鐘鬧鐘》是一款IOS平台的套用。...... 在有限的時間內免費 主題時鐘,多報警終於來到了在App Store ! 它有百日咳12夢幻般的原始的時尚主題,你不會找到任何...

《主宰時間》是連載於起點中文網的一部小說,作者是裂月屠龍。中文名 主宰時間 作者 裂月屠龍 小說進度 連載 連載網站 起點中文網 ...

本名理察·“瑞普”·亨特(Richard “Rip ”Hunter),是金色先鋒的兒子,也是一位時間旅行者,還是“時間之主”的一員,這個組織的目標就是要保護歷史本身。...

主要套用於要求有統一時間進行生產,調度的單位如:電力,機場、輕軌、捷運、體育場館、酒店、醫院、部隊、油田、水利工程等領域。大區域時鐘系統主要由母鐘和多台子鐘...

基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。...

《時鐘》 作者:高爾基。高爾基在這本書中真實地描述了自己苦惱的童年,反映了當時社會生活的一些典型的特徵,特別是繪出了一副俄國小市民階層風俗人情的真實生動的...

實時時鐘的縮寫是RTC(Real_Time Clock)。RTC 是積體電路,通常稱為時鐘晶片。實時時鐘晶片是日常生活中套用最為廣泛的消費類電子產品之一。它為人們提供精確的實時...

時鐘發生器是用來產生時鐘信號的器件。常用於數字產品中,產品中所有的組件將隨著所產生的時鐘信號來同步進行運算動作。數字產品必須有時鐘的控制,才能精確處理數位訊號...

介紹美國DALLAS公司推出的具有涓細電流充電能力的低功耗實時時鐘電路DS1302的結構、工作原理及其在實時顯示時間中的套用。它可以對年、月、日、周日、時、分、秒進行...

時鐘電路就是產生像時鐘一樣準確運動的振盪電路。任何工作都按時間順序。用於產生這個時間的電路就是時鐘電路。時鐘電路一般由晶體振盪器、晶震控制晶片和電容組成。...

時鐘是生活中常用的一種計時器,人們通過它來記錄時間。至今為止,在中國歷史上有留下記載的四代計時器分別為:日晷、沙漏、機械鐘、石英鐘。...

大時鐘,動畫《超神學院》和《雄兵連》系列中的設定。大時鐘是神河文明模擬整個宇宙的計算雲。...

簡稱主頻,計算機的中央處理器中有 一個不斷地按固定頻率產生時鐘 脈衝信號的脈衝信號源,或叫主時鐘,它所產生的頻率就是主頻率。主頻率是衡 量一台計算機速度的...

電腦主頻率,簡稱主頻,每一台 電子計算機的中央處理器中均有 一個不斷地按固定頻率產生時鐘脈衝信號的裝置,這個裝置叫脈衝信號源,或叫主時鐘,它所產生的頻率就是...

主從同步是在一個交換節點設立一高精度的基準時鐘,通過傳輸鏈路把此基準時鐘信號送到網中各個從節點,各個從節點利用鎖相環技術把本地時鐘頻率鎖定在基準時鐘頻率上...

進入孔徑範圍內的主時鐘周期會不經過翻譯直接傳遞給AGP。設定值為:4MB,8MB,16MB,32MB,64MB,128MB,和256 MB。AGP Master 1 W/S Write (AGP匯流排寫入的1個等待...

虛擬機中自帶的一種增強工具,相當於VirtualBox中的增強功能(Sun VirtualBox Guest Additions),是VMware提供的增強虛擬顯示卡和硬碟性能、以及同步虛擬機與主機時鐘的驅動...

3. 指某個一定的時間,小時:鐘頭(小時,如“開了一個鐘頭的會“)。 從以上解釋來看,“鐘”的意義已相當清晰,主要與古代樂器及時間有關。 ●再說“锺”,解釋...

推動一系列齒輪運轉,借擒縱調速器調節輪系轉速,以指針指示時刻和計量時間的計時器...天津等6大鐘表主產區;從產量來看,我國已成為世界鐘錶生產大國,鐘錶產量穩居世界...

宋元明時鐘姓實際已經成為南方的著名姓氏。宋元明600餘年,鐘姓的分布總格局變化...創建者:聽濤閣主 詞條貢獻榜 突出貢獻者: 菲爾普斯批發部 梅家靈 猜...