基本介紹

- 中文名:串並轉換

- 外文名:serial/parallel conversion

- 別名:串並變換

- 類別:SIPO,PISO

數據傳輸

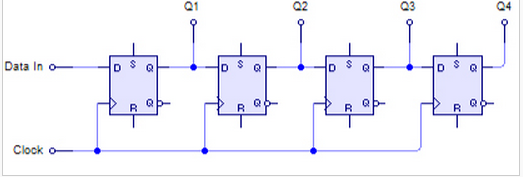

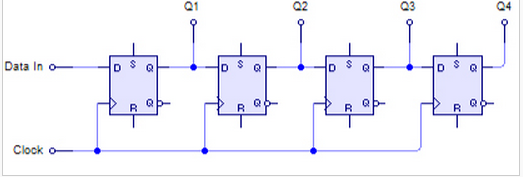

串列並行輸出(SIPO)

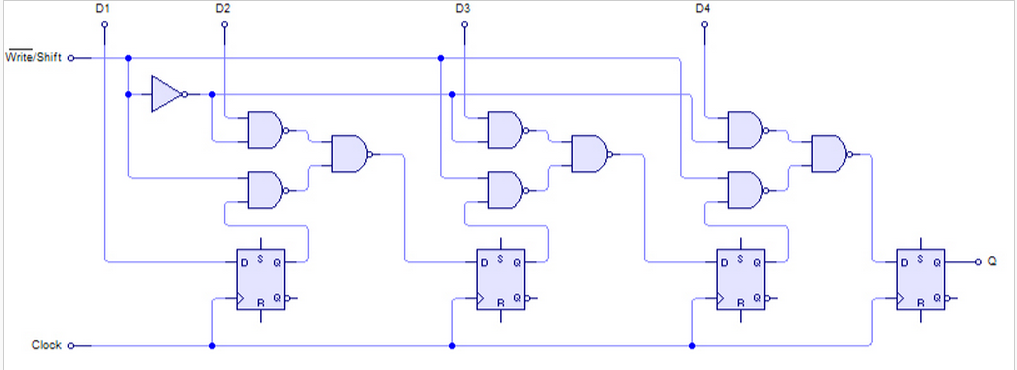

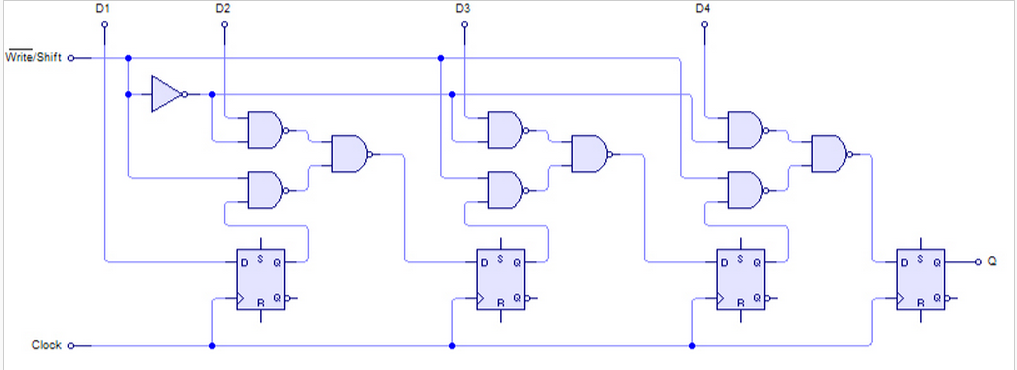

並行串列輸出(PISO)

串並轉換是完成串列傳輸和並行傳輸這兩種傳輸方式之間轉換的技術。移位暫存器可以實現並行和串列輸入和輸出。 這些通常配置為“串列輸入,並行輸出”(SIPO)或“並行,...

串並轉換是通信類術語,是指並串轉換的逆過程。...... 串並轉換是通信類術語,是指並串轉換的逆過程。中文名 並串轉換 性質 通信類術語 目錄 1 定義 2 作用...

串轉換在實際的電路中使用比較多,尤其在通信線路方面的復用和分解方面,原理上就是一個串轉換和並轉換的過程。舉個簡單的例子,計算機串口傳送數據的過程,如果滿足...

數據類型轉換是數據輸入輸出過程中經常遇到的問題,輸入時,計算機系統要把用戶從鍵盤上輸入的字元串轉變成相應的數值,並存儲在記憶體中;輸出時,要把計算機內部存儲的二...

串口轉換編輯 鎖定 本詞條缺少名片圖,補充相關內容使詞條更完整,還能快速升級,趕緊來編輯吧!1.RS-232-C是美國電子工業協會EIA(Electronic Industry Association)...

本發明描述了一種電能轉換器,該電能轉換器包括:N個變壓器,每個變壓器分別包括初級線圈和次級線圈(S↓[N]);初級電路,與變壓器的初級線圈連線在其上的兩個輸入端...

光纖轉換器編輯 鎖定 光纖轉換器是RS-232/422/485串列數據通過光纖的遠距離傳輸,可以完成串口到光纖的轉換,並且可以延長串列通信信號的傳輸距離。...

而且通過數學推導可知,可以通過Burrows-Wheeler變換得到的字元串計算後綴數組的變體,進而線上性的時間複雜度和空間複雜度內計算後綴數組。除...

電路理論中涉及到“等效”概念的知識點包括:電阻串並聯等效變換、電阻星形聯結和三角形聯結等效變換,兩種電源模型的等效變換,非正弦周期量(電流和電壓)與正弦量的...

在OFDM傳播過程中,高速信息數據流通過串並變換,分配到速率相對較低的若干子信道中傳輸,每個子信道中的符號周期相對增加,這樣可減少因無線信道多徑時延擴展所產生的...

串口轉WiFi模組TLN13UA06支持串口透明數據傳輸模式並且具有安全多模能力,使傳統串 口設備更好的加入無線網路。中文名 串口轉WIFI 額定功耗 小於1W 存儲溫度 -40~...