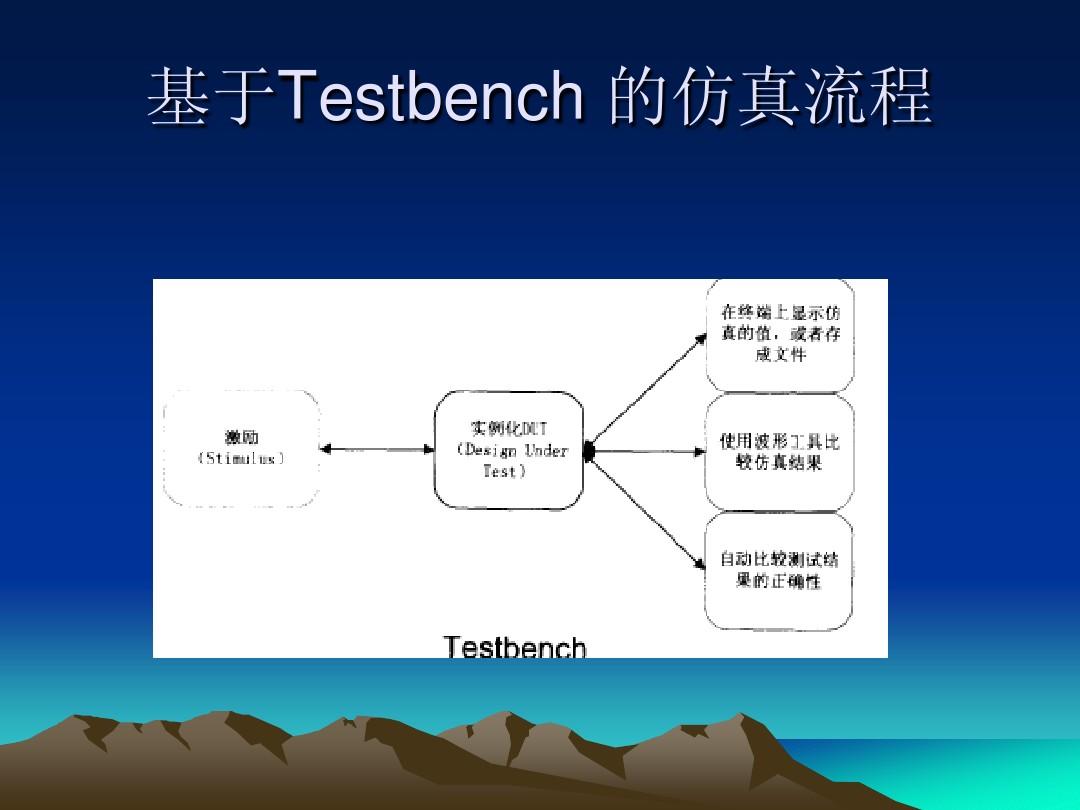

testbench是一種驗證的手段。首先,任何設計都是會有輸入輸出的。但是在軟環境中沒有激勵輸入,也不會對你設計的輸出正確性進行評估。那么此時便有一種,模擬實際環境的輸入激勵和輸出校驗的一種“虛擬平台”的產生。在這個平台上你可以對你的設計從軟體層面上進行分析和校驗,這個就是testbench的含義。

基本介紹

- 外文名:testbench

- 初級套用:testbench更像一個激勵的產生器

- 舉例:可能有幾個input和output

- 數據輸出:一個dataout的

testbench是一種驗證的手段。首先,任何設計都是會有輸入輸出的。但是在軟環境中沒有激勵輸入,也不會對你設計的輸出正確性進行評估。那么此時便有一種,模擬實際環境的輸入激勵和輸出校驗的一種“虛擬平台”的產生。在這個平台上你可以對你的設計從軟體層面上進行分析和校驗,這個就是testbench的含義。

testbench是一種驗證的手段。首先,任何設計都是會有輸入輸出的。但是在軟環境中沒有激勵輸入,也不會對你設計的輸出正確性進行評估。那么此時便有一種,模擬實際...

根據數字積體電路設計的工程需求,本書重點關注了testbench的設計編寫、驗證和測試技術,深入講述了基於VerilogHDL的開關級、門級、RTL級、行為級和系統級建模技術,從而...

7.5.1單頂層testbench1887.5.2多頂層testbench1917.6擴展verilog的高層建模能力1927.7小結1937.8問題與思考193第8章verilog語義和仿真原理195...

jpeg圖像壓縮模組、加密模組、ata控制器、8位risc-cpu等及各個實例模組相應的testbench,所舉實例具有很強的實用性和代表性,每個實例均給出了介紹、功能分析、程式...

2.2.2Testbench例程2.3Verilog HDL仿真方法2.4嵌入式邏輯分析儀2.5正弦波信號發生器及仿真實驗2.6擴展實驗設計第3章狀態機與交通燈設計實驗...

7.5實例:結構化testbench的編寫7.5.1單頂層testbench7.5.2多頂層testbench7.6擴展Verilog的高層建模能力7.7小結7.8問題與思考第8章Verilog語義和仿真原理...

4.2.1 驗證程式(Testbench)的組成4.2.2 實用構造Trestbench技術4.3 基於斷言的驗證4.4 時序驗證4.4.1 靜態時序分析概述4.4.2 靜態時序分析中的基本概念...

2.6.2時序電路Testbench基本結構2.6.3文本界面的Testbench2.7Verilog實例2.7.1Lab1: 門級電路設計與仿真2.7.2Lab2: 簡單時序電路設計與仿真...

7.5.7 TestBench舉例 211本章小結 218思考與練習 218第三篇 基於FPGA的接口開發第八章 UART串口通信控制器 2198.1 UART傳輸系統 219...

10.6 建立仿真Linux作業系統的testbench 305結束語 318附錄A 啟動Linux作業系統的全部列印log信息 320附錄B 兼容ARM9處理器核心帶注釋的Verilog RTL代碼 329...