基本介紹

- 中文名:積體電路匯流排

- 外文名:Inter-Integrated Circuit

- 簡稱:IIC

- 套用:外圍器件接口

- 所在領域:嵌入式系統

- 所屬領域:電子

IIC簡介

硬體結構

數據傳輸

開始和停止條件圖3

開始和停止條件圖3

開始和停止條件圖3

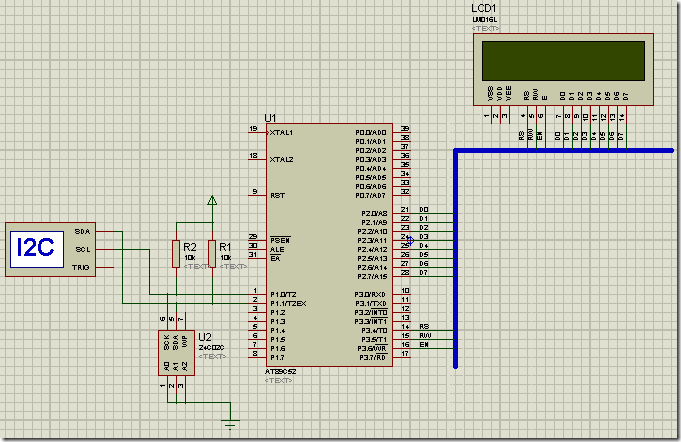

開始和停止條件圖3iic硬體結構 編輯 I2C串列匯流排一般有兩根信號線,一根是雙向的數據線SDA,另一根是時鐘線SCL。所有接到I2C匯流排設備上的串列數據SDA都接到匯流排的SDA上,各設備的時鐘...

IIC-China是國內最大型展示IC套用技術及高品質元器件的權威盛會,是業內設計工程師、技術人員和採購人士不能錯過的全方位交流平台。2009年春秋巡展吸引數以萬計的...

IIC,發現國外那些人和事! 在這個全球化時代,意味著大家的思維、信息、出行、人脈都會走向全球化,而語言障礙阻撓著我們了解外面的世界。IIC試圖做些改變,聚合了通曉...

IIC隱形助聽器是新推出的一種小型的助聽器,比一般的CIC助聽器更小,佩戴時可以達到側方90度觀察完全隱形,可見其形狀之小。IIC隱形助聽器在聲學上也有一系列的優勢,是...

佳博58100IIC是一款電子產品,列印方式是熱敏式。...... 佳博58100IIC是一款電子產品,列印方式是熱敏式。中文名 佳博58100IIC 列印方式 熱敏式 介質寬度 紙寬:57...

佳博58130IIC基本參數 編輯 產品類型:微型印表機列印方式:熱敏式列印寬度:48mm緩衝區:4KB行間距:3.75mm(可用命令調整行間距)接口類型:並口、串口、USB、網路接口...

捷寶TR-982IIC是一款電子產品,尺寸為255X133X105。...... 捷寶TR-982IIC是一款電子產品,尺寸為255X133X105。中文名 捷寶TR-982IIC 商品編號 1269109 商品毛重...

方正晶靈IIC30是一款電子產品,儲存內容可分區加密,PC鎖功能,軟體防寫。...... 方正晶靈IIC30是一款電子產品,儲存內容可分區加密,PC鎖功能,軟體防寫。...

TrojanDownloader.Small.iic“小不點”變種iic是一個體積很小的木馬下載器,從指定站點自動下載病毒程式並在被感染計算機上自動運行。...

方正晶靈IIC20編輯 鎖定 本詞條缺少信息欄、名片圖,補充相關內容使詞條更完整,還能快速升級,趕緊來編輯吧!存儲容量:64接口類型:USB2.0...

IIC:是指點燃能量uJ,280,>180,60...80,<60;T6:是指溫度組別,即電氣設備按其最大表面溫度被分在不同的溫度組別。氣體的溫度組別按不同的點燃溫度劃分。T6是...

USB2I2C是一個U轉I2C匯流排 (I2C/IIC/TWI/SMBUS)的接口晶片。...... USB2I2C:USB轉I2C/IIC/TWI/SMBUS專用,通過USB2I2C晶片可以非常方便地實現PC機USB匯流排和下...

國外已經將隱形助聽器統一稱為IIC隱形助聽器,用以區分以前的偽“隱形助聽器”CIC,RIC等。隱形助聽器優點: 編輯 隱形助聽器即IIC助聽器佩戴外觀及與常規CIC助聽器的佩戴...

0-IIa+IIc型胃腺瘤①0-IIa+IIc型胃腺瘤②0-IIa+IIc型胃腺瘤③0-IIa+IIc型早期胃癌①0-IIa+IIc型早期胃癌②0-IIa+IIc型早期胃癌③...

USB-I2C提供主I2C接口,實現PC上位機和下位控制器之間的直接數據輸入輸出,而不再需要單片機/DSP/MCU等的監控。在同步串口方式下,USB2I2C晶片還支持兼容I2C(IIC)...

International Review of Intellectual Property and Competition Law (IIC), 2011/8,pp. 926-952.10. Das GmbH-Recht in China aus rechtsvergleichender Sicht,...