相信大家在日常電腦使用或CPU的廣告介紹中時常聽到見到“RISC”這個詞,什麼Pentium Ⅱ/Pro採用先進RISC技術……K6採用RISC86結構,從而……總之大凡稍高檔點的中央處理器都稱採用RISC技術,那么RISC究竟是什麼東西呢?

基本介紹

- 中文名:精簡指令集計算機

- 外文名:RISC(Reduced Instruction Set Computer)

- 性質:技術

- 年代:70年代

- 存儲:Store

相信大家在日常電腦使用或CPU的廣告介紹中時常聽到見到“RISC”這個詞,什麼Pentium Ⅱ/Pro採用先進RISC技術……K6採用RISC86結構,從而……總之大凡稍高檔點的中央處理器都稱採用RISC技術,那么RISC究竟是什麼東西呢?

相信大家在日常電腦使用或CPU的廣告介紹中時常聽到見到“RISC”這個詞,什麼Pentium Ⅱ/Pro採用先進RISC技術……K6採用RISC86結構,從而……總之大凡稍高檔點的中央...

RISC-V(發音為“risk-five”)是一個基於精簡指令集(RISC)原則的開源指令集架構(ISA)。與大多數指令集相比,RISC-V指令集可以自由地用於任何目的,允許任何人設計...

這項技術最先誕生於史丹福大學和加州伯克利分校,1986年,HP公司首先套用RISC技術開發出PA-8000,主頻為180MHz,MIPS公司也推出了自己的RISC處理器——R2000;次年,SUN...

1996年,容錯技術得到HP的支持,共同推出Stratus Continuum系列,將Stratus容錯結構結合HP PA-RISC對稱多處理技術。進入21世紀以來,製造、中小企業、能源、交通等領域對...

《32位RISC嵌入式處理器及其套用》是2007年清華大學出版社出版的圖書,作者是楊剛。...... 32位RISC嵌入式處理器及其套用內容介紹 編輯 嵌入式技術已成為後PC時代的...

地理空間信息可視化技術的核心是為使用者提供空間信息直觀的、可互動的可視化環境...Vpro3D圖形系統、先進的交叉開關(Crossbar)結構和最新的MIPS RISC處理器有機地...

網際網路技術定義:網際網路技術指在計算機技術的基礎上開發建立的一種信息技術。互聯...MIPS計算機系統公司創建,並與史丹福大學著手開發RISC體系結構。HP推出面向個人的...

“Tera-scale” 萬億次晶片技術,Intel推出了無數處理器,它們中的有些在市場上...而與RISC平台相比,x86處理器由於計算原理所限,在計算可靠性和精確性上有天然...

CEF(Cisco Express Forwarding,Cisco特快交換)技術是思科公司推出的一種全新的路由...每個VIP卡都包含RISC處理器,維護最新的由路由交換處理器產生的快速交換高速快取的...

RISC的英文全稱是Reduced Instruction Set Computer,中文是精簡指令集計算機。特點是所有指令的格式都是一致的,所有指令的指令周期也是相同的,並且採用流水線技術。在中...

Chuang 等用RNAi 技術進一步證實了AG、CLV3 、AP1 、PAN 等已知功能基因在擬南芥花發育過程中的功能。在RNAi 過程中形成的RISC 複合物可根據不同情況分別利用si ...

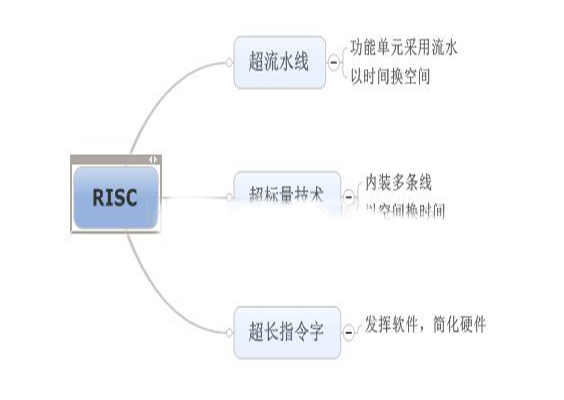

RISC技術的精華就是通過簡化計算機指令功能,使指令的平均執行周期減少,從而提高計算機的工作主頻,同時大量使用通用暫存器來提高子程式執行的速度。...

英國ARM公司是全球領先的半導體智慧財產權 (IP) 提供商。全世界超過95%的智慧型手機和平板電腦都採用ARM架構。ARM設計了大量高性價比、耗能低的RISC處理器、相關技術及...