DDFS-Direct Digital Frequency Synthesizer 直接數字頻率合成。

基於相位累加器的DDS改進模型。為了區分它與DDWS的不同,將這這種結構稱為直接數字

頻率合成(DDFS)。

基本介紹

- 中文名:直接數字頻率合成

- 外文名:Direct Digital Frequency Synthesizer

- 縮寫:DDFS

- 基於:相位累加器的DDS改進模型

DDFS-Direct Digital Frequency Synthesizer 直接數字頻率合成。

基於相位累加器的DDS改進模型。為了區分它與DDWS的不同,將這這種結構稱為直接數字

頻率合成(DDFS)。由於採用了數控振盪器(NCO)硬體設計,使得輸出頻率控制變得簡單。隨著晶片級DDFS的問世及技術產品的不斷升級,對DDFS技術的深入研究和工程程套用取得了引人注目的成果,並逐漸成為DDS的主流結構,以至於人們習慣於用DDS來特指DDFS。

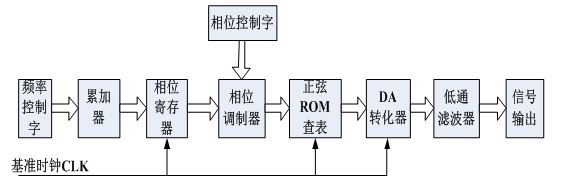

直接數字頻率合成(DDFS)技術,原理如圖2所示。

圖2 直接數字頻率合成(DDFS)原理框圖

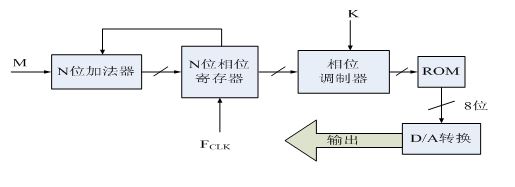

DDS的工作原理是以數控振盪器的方式產生頻率、相位可控制的正弦波。電路一般包括基準時鐘、頻率累加器、相位累加器、幅度/相位轉換電路、D/A轉換器和低通濾波器(LPF)。頻率累加器對輸入信號進行累加運算,產生頻率控制數據X(frequency data或相位步進量)。相位累加器由N位全加器和N位累加暫存器級聯而成,對代表頻率的2進制碼進行累加運算,是典型的反饋電路,產生累加結果Y。幅度/相位轉換電路實質上是一個波形暫存器,以供查表使用。讀出的數據送入D/A轉換器和低通濾波器。

圖3

DDFS具有頻率轉換時間短、近載頻相位噪聲性能好、精度高,產生的信號頻率範圍寬等優點。DDS技術的實現依賴於高速、高性能的數字器件。可程式邏輯器件以其速度高、可線上編程,以及有強大EDA軟體支持等特性,十分適合實現DDFS技術。