簡介

CD4027 包含了兩個相互獨立、互補對稱的J-K 主從

觸發器的單片

積體電路。

每個觸發器分別提供了J、K、置位、復位、時鐘輸入和經過緩衝的Q 及Q非輸出信號。此器件可用作移位暫存器,且通過將Q輸出連線到數據輸入,可用作計數器和觸發器。在時鐘上升沿觸發時,加在D 輸入端的邏輯電平傳送到Q 輸出端。置位和復位與時鐘無關,而分別由置位或復位線上的高電平完成。

規格參數

工作電壓:3V~18V

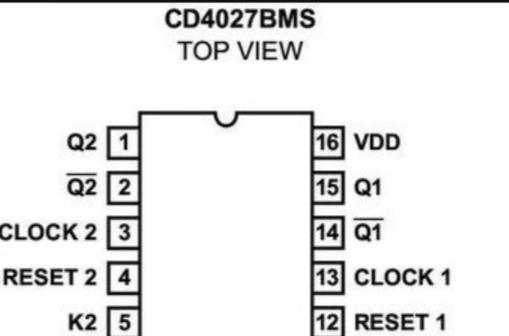

引腳功能

Q-原碼輸出端

Q非-反碼輸出端

CLK-時鐘輸入端

Vss-地

Vdd-正電源

RST-清零

SET-置位