簡介,高速 BiCMOS 技術,MOS 器件的電學性能,NpN器件的電學性能,CMOS、BiCMOS 邏輯門的比較,發展中的BiCMO技術,BiCMOS技術在亞微米領域中的發展,BiCMOS 技術在高密度存儲器中的套用,

簡介

隨著新世紀國中國電信和移動通信事業、微電子技術和計算機網路技術的蓬勃發展,國內對各種通信電子電路和通信專用大規模和超大規模積體電路(簡稱ASIC)的性能要求越來越高。通信技術領域迫切期待著越來越多的高性價比的設備和產品問世!順應於此,有必要研發高性價比的各種通信ASIC和通信器材、設備新品,以滿足人們日益增長的使用需求。為此,從筆者查閱的大量的相關文獻資料來看,雙極型電路具有速度高、電流驅動能力強和模擬精度高等特點,而CMOS電路則在高集成度和低功耗方面有著無可比擬的優勢。在以不斷追求更高性能和更為時尚的當今積體電路(IC)製造業,這兩種工藝優勢互補的結合,即產生新型的BiCMOS電路,完全是水到渠成、無法阻擋的。

高速 BiCMOS 技術

CMOS工藝和BiPolra工藝是兩種主要的矽積體電路工藝,它們有各自的優點。CMOS器件有集成度高、功耗 低、輸入阻抗高等優點。BiPolar器件有截止頻率高、驅動能力大、速度快、噪聲低等優點。它們的優缺點正好互相補充,將它們集成同一晶片上形成BiCMOS工藝,製得的器件性能定將超出單一工藝。

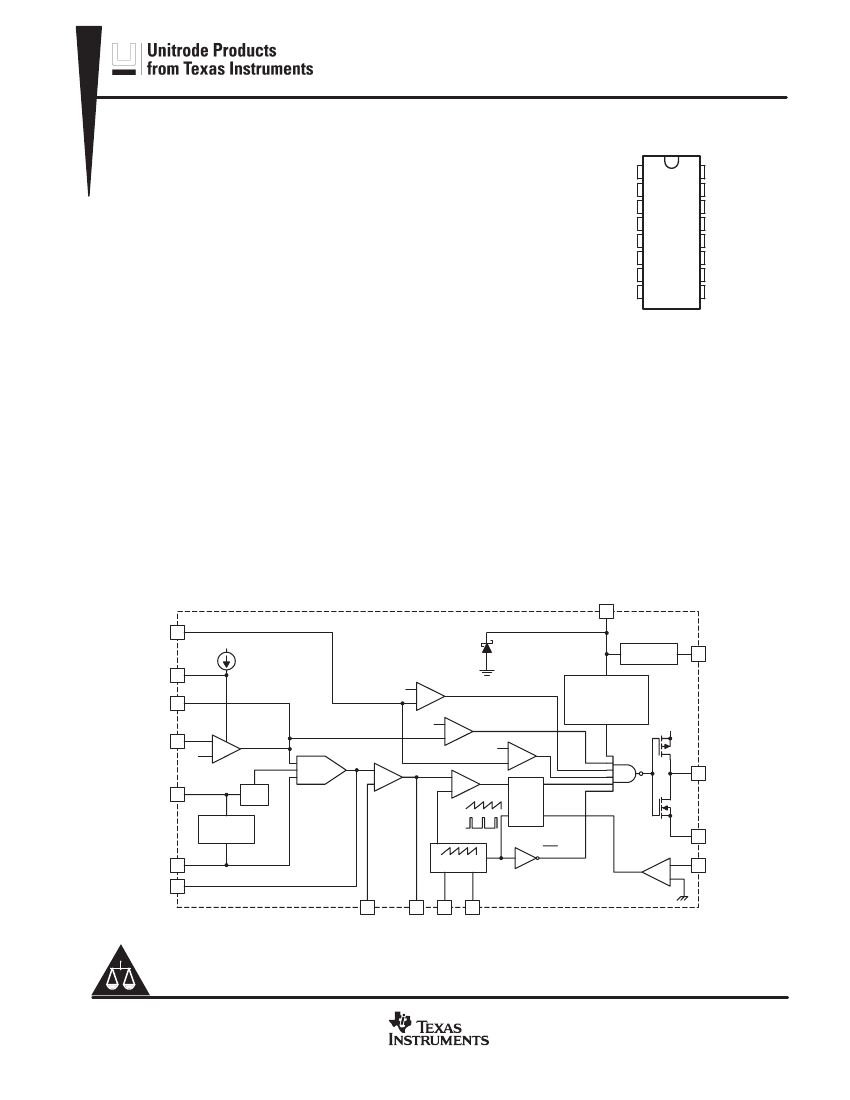

形成 BiCMOS工藝的方案現有很多,大致可歸納為兩大 類:一 類是以CMOS工藝為基礎,另一類是以Bipolar 工藝為基礎。採用原有的 2um N阱CMOS工藝基礎上選用雙埋層、雙阱、外延結構來形成 BiCMOS工藝。

套用SUPREM lll 和SEDAN III 設計了Bi-CMOS工藝流程。成功地將縱向NPN管和CMOS器件集成在同一晶片上,而且製得了BiCMOS反相器門及與非門。

MOS 器件的電學性能

測量得到 L= 2um的NMOS和PMOS器件的源漏穿通電壓分別為1 IV和8V。

由Latch 一 up測試單元測得的 Latch一uP 觸發電壓>17V, 維持電壓>10V。表明器件可在SV電源下安全套用 。

NpN器件的電學性能

擊穿電壓BVcbo和BVceo 的測量結果與計算結果相一致,分別為20~24V和8~10V。

收集極串聯電阻Rcs是NPN器件的重要參量之一, 它的大小直接影響電路工作速度。計算和測得的結果相一致。為80 ~ 100歐姆。

CMOS、BiCMOS 邏輯門的比較

對BiCMOS 試驗版圖上的CMOS、BiCMOS反相器和與非門進行了延遲時間td 的測量。測試時邏輯門的負載 電容CL需要外接。因管芯未封裝,測試台探針、弓線約2PF的分布電容將作為負載的一 部分。

BiCMOS反相器的 td 隨 CL 增加很緩慢的增加。說明在大電容負載情況下BiCMOS反相器的速度和驅動能力大大優於CMOS反相器。與非門的比較結果與上面一致。

測量還發現,金屬發射極管作驅動電路的 BiC -MOS門的延遲時間比採用多晶發射極管的大,這是由於前者β較低的緣故。

發展中的BiCMO技術

BiCMO技術將雙極器件和CMO器件有機結合起來,充分發揮它們各自長處,使其既具有雙極電路高速、強驅 動能力的優點,又具有CMOS高集成度、低功耗的優點,已成為LSI 和VLSl電路的重要發展方向。論證了BiCMOS 技術在亞微米領域中的發展及其器件性能,並闡述了該技術在高密度存儲器中的套用。

BiCMOS技術在亞微米領域中的發展

在亞微米領域中,由於VLSI /ULSI 電路需要低功耗,BiCMOS 技術趨向以CMOS工藝為基礎。為了在性能、 功率、 密度和成本方面實現共同的目標,雙極和CMOS器件結構已熔合成混合的亞微米BiCMOS技術。

1、亞微米BiCMOS 技術基本工藝結構:

把NPN雙極管併入基本的雙阱CMOS結構,最簡單的方法是雙極集電極用n阱,雙極基區加 一層掩蔽層。在這 種結構中,雙極發射極的形成、雙極集電極的摻雜增強、以及NMOSn+源/漏的形成是同時完成的。雙極電晶體的 非本徵基區摻雜和PMOSp+源/漏也一起形成。從雙極觀點出發,該結構的性能由高集電極串聯電阻加以權衡,另外,發射極結深取決於n+源/漏深度,結深度比高性能雙極器件所需深度深。

2、亞微BiCMOS 技術器件性能:

在不改變CMOS 電特性的前提下,將雙極元件併入基本的CMOS工藝是很有益的。由於該工藝使用原始單一 的CMOS電路準則,使所有CMOS電路的設計變得明朗簡易,從而改進了混合技術的成本一效率比。例如,增加最小的設計投資就能將標準的CMOS元件改進成具有ECL輸入/輸出接口能力的BiCMOS電路。

為了提高低壓BiCMOS的性能,門設計中也有一些改進方法,包括BiNMOS,合併式BiC-MOS,以及互補BiCMOS。

一 種新型的非常規BiCMOS技術,稱為MCBiCMOS( 即合併互補BiICMOS,與常規的BiCMOS和CMOS相比, M CBiCMOS結構有以下優點:

( 1) 晶片上電路結構緊湊,晶片面積小,同樣條件的晶片占用面積只有常規BiCMOS的一半,與CMOS相當。

( 2) 工作速度高、負載能力強。在同等條件下的門延時是常規BiCMOS的50% 一60%,高速ECL相當。

( 3) 低壓工作特性好。

MCBiCMOS結構良好的電路性能和占用較小晶片面積使其更適合於製作大規模、高性能的專用積體電路。

BiCMOS 技術在高密度存儲器中的套用

高密度存儲器的存取時間由整個存取路徑決定,因為存儲器陣列本身是這路徑的獨一元件。在MOS存儲器外 圍增加相對少量的雙極器件,能明顯增進存儲器整體存取速度,而對於整個器件總數來講 所增加的器件數是微不足道的。況且,在這種場合中使用相對少量的雙極器件,使純雙極存儲器中傳統的效率問題不再衝突。

1、存儲器工藝中的BiCMOS技術:

利用存儲器工藝模組製造高性能雙極電晶體, 往往很出色 。

使用雙層多晶矽工藝已製造了幾代CMOS SRAM。第一層多晶形成MOS電晶體柵,第二層在四管CMOS存儲 器單元中形成高阻抗負載電阻。第二層多晶與存儲器單元中的矽襯底接觸。因為多晶一襯底接觸已存在於這樣的工藝中,於是只需增 加最小的複雜性就能產生一個具有多晶矽發射極的雙極電晶體。發射極是由摻雜劑從摻雜多 晶層向存在注入基區的矽襯底擴散而產生的。

2、工藝複雜性:

大多數BiCMOS工藝設計者使用埋層和外延來得到足夠的 集電極阻抗和基極推出效應的遏制。雙極管也需要 產生一 個基區,通常用離子注入的方法。一共同第三增強層使用附加的深集電極區 ( 集電極深阱或集電極柱塞 ) 以減少集電極阻抗。多數存儲器BiCMOS工藝將這些元件( 埋層和外延、基區、和深集電極 ) 加入核心CMOS工藝 ,從而產生高性能BiCMOS。