雙極-CMOS積體電路(BiCMOS),BiCMOS器件和電路及其製造技術,先進的BiCMOS技術在通信領域的典型套用,BiCMOS技術在通信領域的套用前景和發展趨勢,

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)雙極-CMOS積體電路(BiCMOS)由雙極型門電路和互補金屬-氧化物——半導體(CMOS)門電路構成的積體電路。特點是將雙極(Bipolar)工藝和CMOS工藝兼容,在同一晶片上以一定的電路形式將雙極型電路和CMOS電路集成在一起,兼有高密度 、低功耗和高速大驅動能力等特點。

雙極-CMOS積體電路(BiCMOS) 高性能BiCMOS電路於20世紀80年代初提出並實現,主要套用在高速靜態存儲器、高速門陣列以及其他高速數字電路中,還可以製造出性能優良的模/數混合電路,用於系統集成。有人預言,BiCMOS積體電路是繼CMOS積體電路形式之後最現實的下一代高速積體電路形式。

BiCMOS器件和電路及其製造技術 (1)高速BiCMOS器件製作技術

1)以CMOS為基礎的BiCMOS工藝

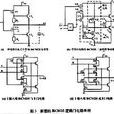

BiCMOS技術是將單、雙極兩種工藝合適地融合在一起的技術,但這絕不是簡單、機械地摻和在一起,很多工藝可以一塊兒或設法結合在一起做。目前BiCMOS工藝主要有兩種:一是以CMOS為基礎的BiCMOS工藝,這種工藝對保證CMOS器件的性能較為有利;二是以雙極工藝為基礎的BiCMOS工藝,這種工藝比較張揚BJT器件的性能。圖1是以CMOS為基礎的0.8μm BiCMOS器件的縱向剖面圖。

BiCMOS-C型是只使用少數雙極性電晶體來驅動長線一輸出快取器,而BiCMOS-E型則主要是以ECL技術為主,用CMOS電晶體做為大型存儲部件。這兩種類型的BiCMOS由於需要將雙極性晶

雙極-CMOS積體電路(BiCMOS)體管和MOSFET(金屬氧化半導體場效應電晶體)集成於同一晶片,生產工藝複雜,比製造同種複雜程式的CMOS器件花費要高,它的成功與否將取決於CMOS、GaAs在其各自套用領域取得成功的程度。BiCMOS-E性能不及GaAs與純ECL技術,因此在高檔套用場合性能不能與GaAs與純ECL相抗衡。另一方面,BiCMOS的價格又不如CMOS便宜,因此,BiCMOS-C必須爭取在價格上接近於CMOS,而在性能上又要能趕上GaAs技術。

雙極-CMOS積體電路(BiCMOS) 由圖1可見,以外延雙阱CMOS工藝為基礎,在N阱內增加了N+埋層和集電極接觸深N+注入(圖中左邊BJT),以減少BJT器件的集電極串聯電阻阻值,降低飽和管壓降;用P+區(或N+區)注入製作基區;發射區採取多晶矽摻雜形式,與MOS器件的柵區摻雜形式一致,製作多晶矽BJT器件。因此這種高速BiCMOS製造工藝原則上不需要增加其它的重要工序。

2)以雙極工藝為基礎的BiCMOS工藝

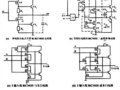

目前在國外,先進的雙極工藝一旦被開發出來,就被用於BiCMOS工藝。以雙極工藝為基礎的BiCMOS工藝即為一例,這種工藝的BiCMOS既顧全了CMOS器件,使其與純CMOS工藝中的器件相比性能毫不遜色;同時又兼顧了BJT器件,使其與新的純雙極工藝中的器件不相上下。

這種工藝是在雙阱CMOS工藝中加上精心設計的4張版圖來製作BJT器件的。該BiCMOS工藝中BJT器件的外基區和PMOS管的源、漏區同時形成,BJT器件的發射區可與NMOS管的源、漏區同時形成。所製作的BiCMOS器件縱向剖面圖如圖2所示。

雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) (2)高速BiCMOS電路製作工藝和微細加工技術的特殊考慮

1)雙阱結構中的阱結構尺寸及其埋層

對BiCMOS電路來說,需要仔細研究CMOS阱和BJT器件的集電極的工藝要求。一個主要的工藝設計折衷方案涉及到外延層和阱的輪廓特性。對於BJT器件,一方面集電極-發射極之間的反向擊穿電壓U(BR)CEO、集電極電阻和電容,以及生產工藝的可控制性決定了外延層的最低厚度;另一方面,如果外延層太厚,特徵頻率fT就會下降而集電極電阻RC值就會增大。對於MOS器件,在製作PMOS器件時使用N+埋層就要求外延層必須足夠厚,以避免過大的結電容和PMOS器件的背偏置體效應(back-bias body effect)。

雙阱結構中的N阱不僅影響PMOS器件,而且也可作為NPN型BJT器件的集電極。因此,除了應充分保證CMOS器件的性能以外,N阱摻雜既要足夠重以防止Kirk效應(Kirk effect),同時又應足夠輕,以增高BJT器件的U(BR)CEO。

2)外延層與自摻雜

在兩種類型的埋層上生成輕摻雜的薄外延層,對外延沉積工藝來說是一種挑戰。必須使在垂直和水平方向的兩種類型雜質的自摻雜儘量地小,以避免在阱中需要過量的反摻雜。

3)利用雜質離子注入降低MOS器件閾值電壓

在PMOS器件的溝道區通過硼離子注入調節,降低其閾值電壓;製作NMOS器件溝道區時注入磷離子,不僅可使NMOS器件的閾值電壓分散性大為減小,而且還可減小N阱同P型襯墊的摻雜濃度比值。這一技術意味著N阱區摻雜濃度可以降低,因而NMOS器件的閾值電壓大為減小,結果使通信用BiCMOS電路可在低電源電壓(3.3V)下工作。

4)用矽柵自對準工藝減小交疊電容

製作MOS器件時採用矽柵自對準(在柵下源、漏區極少擴展)工藝,使柵-源和柵-漏擴散區的重疊大大減小,柵-源及柵-漏交疊電容相應地大為減小。這樣做有利於矽柵雙阱BiCMOS電路的工作速度得以提高。此外,矽柵自對準工藝也可明顯減小設計同樣溝長的MOS器件所需要的版圖尺寸,因而晶片的集成度得到了提高(大約提高30%)。

5)用高電阻率P型矽襯墊來提高工作速度

BiCMOS器件應採用高電阻率P型矽襯墊,這樣既與CMOS、射極耦合邏輯電路(ECL)和砷化矽(GaAs)工藝有良好的兼容性,又降低了NMOS器件的結電容,有利於提高通信和信息處理用BiCMOS電路的速度。

先進的BiCMOS技術在通信領域的典型套用 (1) 通信用數字邏輯電路、數字部件和門陣列等

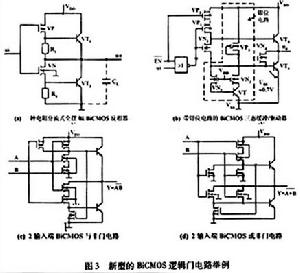

由第二節可知,BiCMOS電路的最佳化組合是用CMOS電路充當高集成度、低功耗的電路部分,而僅用雙極型電路來做輸入/輸出(I/O)電路部分,這是最早的BiCMOS數字積體電路的設計方案。後來,更先進的BiCMOS技術將BJT器件也集成到邏輯門中。與傳統的CMOS門一樣,由於門電路輸出端兩管輪番導通,所以這種BiCMOS邏輯門靜態功耗接近於零,而且在同樣的設計尺寸下,它們的速度將更快。儘管BJT器件的加入會增加20%的晶片面積,但是考慮到其帶負載能力的增強,BiCMOS門的實際集成度比CMOS門將有所增加。比較典型的BiCMOS邏輯門有:反相器(非門)、三態緩衝/驅動器、與非門和或非門,它們分別如圖3(a)、(b)、(c)、(d)所示。本課題對這4個門均已進行了硬體電路實驗,所得實驗數據為:平均傳輸延遲僅為十幾納秒,靜態功耗近似為零,動態平均功耗也只有1~2mW。

雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) BiCMOS邏輯門在通信數字部件(如編碼器、解碼器和模/數轉換器等)和門陣列的套用中極為廣泛,因為它的扇出數一般為5~8,如此大的扇出數意味著具有較強的帶負載能力,而且BiCMOS門比CMOS門能更快速地驅動這些負載。另外,BiCMOS門中的器件尺寸可以是一致的,這就降低了通信數字部件在物理設計上的難度;不同的CMOS電路對減小單位負載的傳輸延遲往往不同,而對於BiCMOS電路,由於雙極型推挽BJT器件隔開了CMOS電路的主體與負載,使得不同電路中負載的狀況變差都是相同的,這樣就簡化了通信和信息處理用數字邏輯部件和電路的設計任務,提高了工作效率。

(2) 通信用數位訊號處理器(DSP)和微處理器(CPU)

若通信DSP和CPU等採用CMOS工藝,則晶片外主線就要有較大的帶電容負載的能力。傳統的接口驅動電路採用雙極工藝製作,這樣可以保證數據傳輸速度,但是功耗卻大了些。以32位CPU為例,它包含有10個或者更多的接口器件,但同一時間內只有一條主線是激活的,亦即每一條主線有90%的時間不工作。由於這種接口器件是單純雙極型的,即使不在工作時它也在不停地消耗功率,所以整個CPU的靜態功耗將會增大。

如果用BiCMOS器件做成接口驅動電路,則處於非門工作狀態的驅動器取用的電流就要小多了。在很多情況下,靜態功耗可以節省接近100%,而傳統主線接口驅動電路的功耗約占整個系統功耗的30%,故這種節電效果非常顯著,因而特別適用於手機、個人數字處理器和筆記本電腦等一類使用電池的通信、計算機和網路設備中。更為有利的是,BiCMOS數字積體電路的速度與先進的雙極型電路不相上下,這與高速數字通信系統的速度要求是相適應的。

用0.8μm BiCMOS已研製出主頻為100MHz的32位CPU電路。該電路中CMOS器件占97%,而BJT器件只占3%,BJT器件僅用於驅動大負載電容或放大小的電平擺幅信號。圖4為算術邏輯單元(ALU)中四位一組的BiCMOS進位傳輸電路。圖中Φ1為系統時鐘,Φ2為預充時鐘。由於BJT器件的存在,預充電平決定於BJT器件發射結壓降,所以預充電平降低為0.8V上下。電平擺幅的減小有利於提高該電路的運算速度。32位字長的ALU要求有8個這樣的進位傳輸電路,它的總傳輸延遲只有7.2ns,功耗也只有十幾毫瓦。

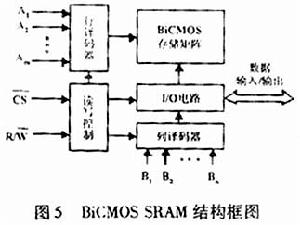

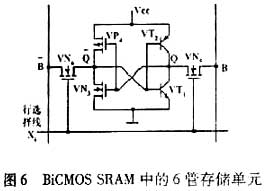

(3) 通信用BiCMOS SRAM和ROM等

由於純CMOS工藝無法生產出通信專用的高速度、大負載驅動能力的SRAM和唯讀存儲器(ROM)晶片,而BiCMOS SRAM和ROM晶片擁有與CMOS SRAM和ROM較為接近的集成度、功耗和更高的速度,故先進的BiCMOS技術給SRAM和ROM產品的速度、容量和功耗等性能指標的調和、折衷和互補提供了迴旋餘地。現以BiCMOS SRAM為例,介紹圖5所示的設計方案。它的主體存儲矩陣用P阱中專門設計的BiCMOS存儲單元組成,所設計的6管BiCMOS存儲單元如圖6所示,製作這種BiCMOS存儲矩陣的模組區與CMOS的大致相同或略高;而圖5中的地址解碼器、字線/位線驅動器和讀寫控制電路及靈敏放大器等則可用BiCMOS電路。與全CMOS SRAM相比,本文提出的BiCMOS SRAM在低壓(VDD=3.3 V)下,其存儲單元存取速度提高了接近3倍,讀/寫一次僅需時6~8 ns,而且其備用單元功耗約為45.2nW/bit,而實用單元功耗也只有6.89μW/bit,均為較低的存儲單元功耗水平。這一結果充分表明了新的BiCMOS SRAM電路結構是通信用高速、低壓SRAM中較為理想的一種設計方案。

雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS) 同理,該設計思路同樣適用於ROM和可程式邏輯器件(PLD)的字線/位線驅動器、改寫電路和讀控制電路以及其它通信ASIC晶片的存儲系統中。

(4) 通信模/數混合電路的套用

用BiCMOS工藝可以將模擬和數字電路集成在同一塊晶片上。當然晶片上大部分面積是有數位訊號處理功能的CMOS單元電路,而剩下的晶片面積(約占15%~20%)用來做模擬電路單元以及晶片與外界模擬世界的接口電路。這些模擬電路單元包括I/O(包含電阻和NPN型BJT器件)、用BJT器件製作的運算放大器、參考電壓和電流源、鎖存比較器和NPN型BJT器件組成的模擬電路(例如直接用來驅動LED的電路)等。這種專用晶片可以用來做SDR系統的ADC和DAC、接/發射機的模/數混合電路以及其它通信系統套用場合。

因為MOS管的閾值電壓UTH對工藝過程和器件尺寸非常敏感,而BJT器件的開啟電壓UBE比UTH更容易精確控制,所以BJT器件更容易得到性能良好的匹配對管。這種優良匹配對管的雙極型集成運算放大器的補償電壓比MOS運放小一個數量級。BiCMOS運算放大器具有雙極型電路部分的低輸入補償電壓和高增益,以及CMOS電路部分的低功耗和高集成度。這種強強聯合的先進工藝,亦被用於軟體無線電(SDR)系統中的高速、低功耗A/D和D/A轉換器。

BiCMOS技術在通信領域的套用前景和發展趨勢 (1) 通信SOC高性能BiCMOS技術的一個重要研發方向

最近幾年來,通信套用頻率正在不斷增加,幾乎所有套用領域都將進入雙吉赫茲頻段。如何順應通信形勢發展的要求,將通信系統中多種功能集成在一個晶片上,即組成片上系統(System On a Chip,簡稱SOC),則無疑是一種較佳的解決方案。這樣一來,SOC不再僅僅限於低頻CMOS晶片的設計中,而且也包括了高頻有線和無線通信BiCMOS晶片,這是當今高性能BiCMOS技術的一個重要研發方向。

SOC的概念是在20世紀90年代提出來的,它既克服了多晶片集成系統製作和運行中所產生的一些困難,又獲得了更高的系統性能。例如,現在的CPU晶片工作速度非常高(傳輸延遲小於幾十皮秒),但是如果存儲器晶片依舊與CPU分開,則由於訪址延時的加入,這種高速性能在計算機通信和未來個人通信中就體現不出來。即便使用光束傳送信號,延時也只有3.3ps/mm。這就要求把存儲器和CPU集成到一個晶片上去。可以預見,將更多功能集成到一個晶片上,還能解決今後晶片管腳數目增多、測試困難和成本較高等一系列問題。

現在的SOC主要有3種類型:一是以CPU為核心,集成各種存儲器、控制電路和系統時鐘等,乃至集I/O功能和A/D、D/A轉換功能於一個晶片上;二是以數位訊號處理器(DSP)為核心,多功能集成;三是上述2種之混合或者把系統算法與晶片結構有機結合的SOC。

總之,SOC的發展並不僅僅是設計上的問題,而且也是先進的工藝技術的實現問題。SOC是很多模組的集成,而且各種模組電路功能的不同,對工藝的要求也是不一樣的,有的要求高集成度,有的要求高速,有的要求強驅動,有的則要求低功耗;有的是數字電路,而有的則是模擬電路。但是,BiCMOS工藝更能滿足如此複雜的技術要求,先進的BiCMOS技術將會使發展通信SOC如虎添翼。

(2) 低壓、全擺幅、高速BiCMOS電路的一個研究熱點

如今,數字通信和internet網路的電子產品對其中VLSI晶片低電源電壓、全輸出邏輯擺幅的要求日趨迫切。例如攜帶型電子產品(如手機、筆記本電腦和個人數字助理等)因用電池供電,故電源電力極為有限,降低電源電壓不僅對減少電池充電次數、延長電池壽命,而且對減小IC器件的電場強度,以防止熱擊穿或熱電子效應,都是非常必要的。先進的BiCMOS技術已被證明在低壓、高速方面優於CMOS技術。但是,BiCMOS數字積體電路存在的問題是:降低電源供電電壓,勢必影響到提高工作速度。目前已設計成功的邏輯單元電路有:瞬時飽和全擺幅式、電荷泵抽取式、鉗位全擺幅式(圖3(b))、自舉全擺幅式BiCMOS數字邏輯集成門電路、BiCMOS三態門和BiCMOS連線邏輯電路等等。

雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS) 雙極-CMOS積體電路(BiCMOS)

雙極-CMOS積體電路(BiCMOS)