硬體描述語言(Hardware Description Language,HDL)是電子系統硬體行為描述、結構描述、數據流描述的語言。非過程計算機硬體描述語言是指不顯式處理過程細節的硬體描述語言。這裡所說的過程細節,不是指待解問題及其解法的本質所要求的的,而是指為計算機上實現求解任務而設定的計算細節及其執行順序。

基本介紹

- 中文名:非過程計算機硬體描述語言

- 外文名:Non process computer hardware description language

- 學科:軟體工程

- 特點:不顯式處理過程細節

- 有關術語:硬體描述語言

- 功能:描述電路的功能、行為

簡介,硬體描述語言,相關硬體描述語言,

簡介

非過程計算機硬體描述語言是使人們無須關心問題的解法和計算過程的描述,只要指明輸入數據所要完成的加工項目和輸出形式,就能得到所需要的結果,而其餘工作都由系統予以完成的硬體描述語言,主要特徵如下:數據的聯想引用機制;數據的高級操作符;不指明可變性順序。聯想引用機制是指不指明訪問路徑、只需給出條件或性質的描述;高級操作符是指可直接表示集合、數組的運算的操作符;可變性順序是指改變執行次序也不影響處理結果的順序。

硬體描述語言

1970年代以來,積體電路的複雜程度按照半導體業界摩爾定律的趨勢急劇增長。電路設計人員的工作量不斷增加,這使得他們必須放棄以往那樣從特定的電子元件,如CMOS、雙極性電晶體為基礎,來開始複雜電路的設計工作。設計流程的關注重心開始轉到電路系統的數據流動以及有關時序的信息,這樣的設計抽象級別被稱為“暫存器傳輸級”。設計人員通過使用硬體描述語言,可以將精力放在電路邏輯功能、時序的設計上,而不需要一開始就考慮具體的器件製造工藝以及它們對電路功能的影響。

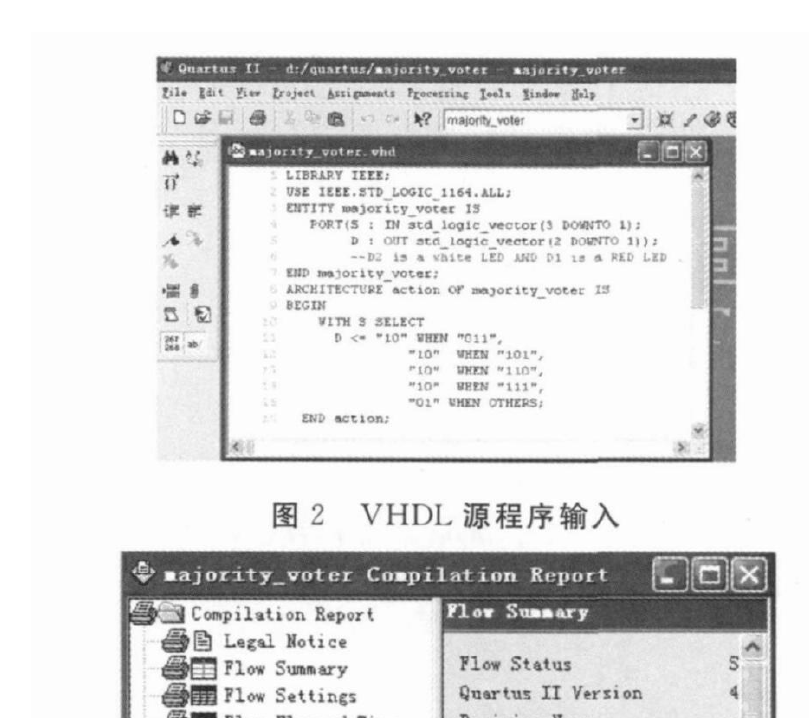

在傳統的硬體電路設計中,主要的設計檔案是電路原理圖,而採用HDL設計系統硬體電路時主要使DHL編寫源程式。所謂硬體描述語言 是一種用形式化方法來描述數字電路和設計數字邏輯系統的語言,它可以使數字邏輯電路設計者利用這種語言來描述自己的設計思想。

硬體描述語言在很多地方可能和傳統的軟體程式語言類似,但是最大的區別是,前者能夠對於硬體電路的時序特性進行描述。硬體描述語言是構成電子設計自動化體系的重要部分。小到簡單的觸發器,大到複雜的超大規模積體電路(如微處理器),都可以利用硬體描述語言來描述。常見的硬體描述語言包括Verilog、VHDL等。

硬體描述語言是對電路系統的結構、行為的標準文本描述。硬體描述語言和一些並行程式語言一樣存在並行性的表達方式。然而,和大多數用於軟體設計的程式語言不同,硬體描述語言可以描述硬體系統在不同時間的時序行為,而時序性正是硬體電路的重要性質之一。在計算機輔助設計中,用於描述電路模組中連線、各層次模組之間互連的硬體描述語言代碼,被稱為“網表”。硬體描述語言可以在結構級(或稱邏輯門級)、行為級、暫存器傳輸級這幾種不同的層次上對電路進行描述,實現同一功能的硬體描述語言也可以使用任一層次的硬體描述語言代碼來描述。通過邏輯綜合,後兩種層次的硬體描述語言代碼可以被轉換到低抽象級別的門級描述,但是採用不同廠商的工具、使用不同的綜合設定策略可能會產生不同的結果。

相關硬體描述語言

Verilog是一種用於描述、設計電子系統(特別是數字電路)的硬體描述語言,主要用於在積體電路設計,特別是超大規模積體電路的計算機輔助設計。Verilog是電氣電子工程師學會(IEEE)的1364號標準。

Verilog能夠在多種抽象級別對數字邏輯系統進行描述:既可以在電晶體級、邏輯門級進行描述,也可以在暫存器傳輸級對電路信號在暫存器之間的傳輸情況進行描述。除了對電路的邏輯功能進行描述,Verilog代碼還能夠被用於邏輯仿真、邏輯綜合,其中後者可以把暫存器傳輸級的Verilog代碼轉換為邏輯門級的網表,從而方便在現場可程式邏輯門陣列上實現硬體電路,或者讓硬體廠商製造具體的專用積體電路。設計人員還可以利用Verilog的擴展部分Verilog-AMS進行模擬電路和混合信號積體電路的設計。

SystemC是一種基於C++語言的用於系統設計的計算機語言,是用C++編寫的一組庫和宏。它是為了提高電子系統設計效率而逐漸發展起來的產物。IEEE於2005年12月批准了IEEE1666-2005標準。

通常,系統由軟體部分和硬體部分組成,系統的一部分功能由軟體實現,而另一部分功能則由硬體實現。早期的系統比較簡單,系統工程師將準備設計的系統劃分為軟體部分和硬體部分,分別由軟體工程師和硬體工程師進行設計、仿真、實現和改進,最後再將軟體部分和硬體部分結合起來形成系統。軟體工程師使用C和C++等程式設計語言,因為這些語言專長於描述串列執行的程式,用來仿真軟體部分;而硬體工程師則使用VHDL和Verilog等硬體描述語言,因為這些語言專長於描述並行運行的硬體,用來仿真硬體部分。但是,隨著電子系統的不斷發展,系統結構越來越複雜,系統元件也越來越多,這就要求系統工程師在先期劃分軟體和硬體時,就對整個系統性能有很好的了解和掌握,以便更好地劃分軟體和硬體,減小設計中不必要的失誤所帶來的損失和風險。SystemC也就由此孕育而生,因為它能夠滿足對軟體和硬體協同仿真的需求。