門陣列法是根據用戶要求,用門陣列母片實現特定功能積體電路的一種半定製設計方法。

基本介紹

- 中文名:門陣列法

- 外文名:gatearray

原理,缺點,

原理

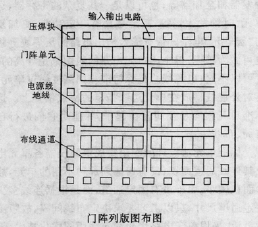

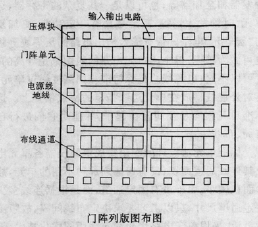

門陣列母片是一種“半成品”積體電路。它是在一個晶片上把單元門電路排列成陣列形式;每個門具有相同的版圖形狀,門與門之間暫不相連,構成一個不具有任何完整功能的陣列;在行、列之間留有布線通道;輸入輸出電路的幾何圖形排列在晶片四周;電源線和地線一般呈網狀分枝遍布晶片,如圖所示。 圖1

圖1

圖1

圖1利用這種“半成品”積體電路根據用戶要求製做某種功能的新電路時,生產廠家在計算機輔助設計系統上,首先對照母片的電路結構,對其上的單元電路進行分配,儘可能使每一個都能與待製造電路的單元對應起來。利用單元電路的電性能參數,對全部電路進行邏輯模擬,完成電路性能驗證。以適當原則(如連線最短或延時最小等)將互連線分配到各通道區,完成單元間的互連。依此布線設計所做的布線掩膜對母片上的單元進行連線和刻孔等工藝,就可獲得所需功能的電路。

一個門陣列母片上可預布幾千個、上萬個基本門電路,僅通過連線設計可實現許多邏輯功能,故這種設計模式的自動化程度高,設計周期短,設計成本低。從製造方面看,積體電路製造的大部分工藝步驟已在母片上進行,故整個電路的製造時間大為縮短,保證了成品質量,適於大批量工業化生產。

缺點

門陣列不適於功能過於複雜的電路。有限品種的母片,且其上只有單一的基本單元,若用它去滿足規模和複雜性各不相同的電路要求,勢必有一些單元不能被用上,使晶片面積利用率下降,一般只能達到50%~60%。這種設計模式不能保證全部互連線都能自動地完成,往往需要人工進行未能連通部分的剩線處理,這種人工處理的速度很慢,是它的另一缺點。

常規門陣列結構的缺點,如布線通道尺寸固定,浪費布線面積,在組成宏單元時,有一些電晶體無法利用:單元之間隔離區占用面積較多等。常規門陣列套用上不靈活、門利用率低。門海技術是將電晶體的基本單元鋪滿整個晶片;無事先確定的布線通道區;宏單元之間採用柵隔離技術;宏單元間的連線在無用的器件區上進行等。採用這些措施可以使晶片的利用率由50%~60%增加到80%以上。門海技術是第二代門陣列的典型代表。