電路結構

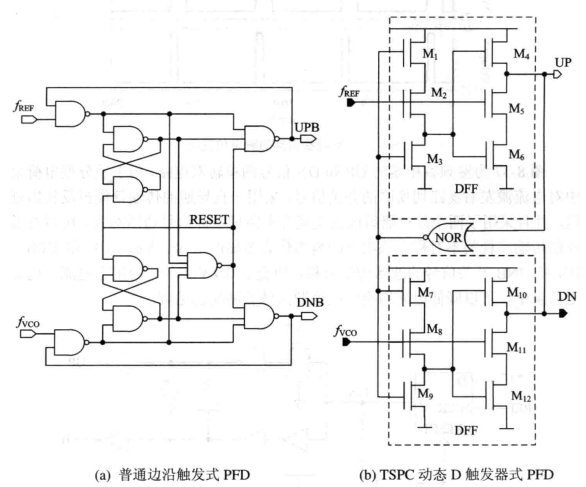

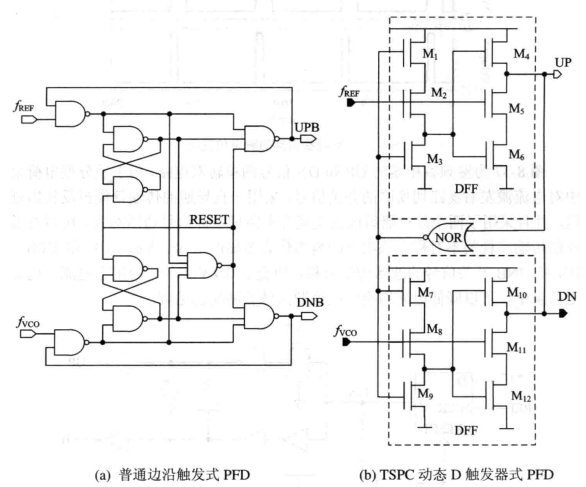

鑒頻鑒相器(PFD)電路的常見結構包括如下圖所示的普通邊沿觸髮式PFD和真單相時鐘(True Single Phase Clocking,TSPC)動態D觸發器式PFD。

電路結構

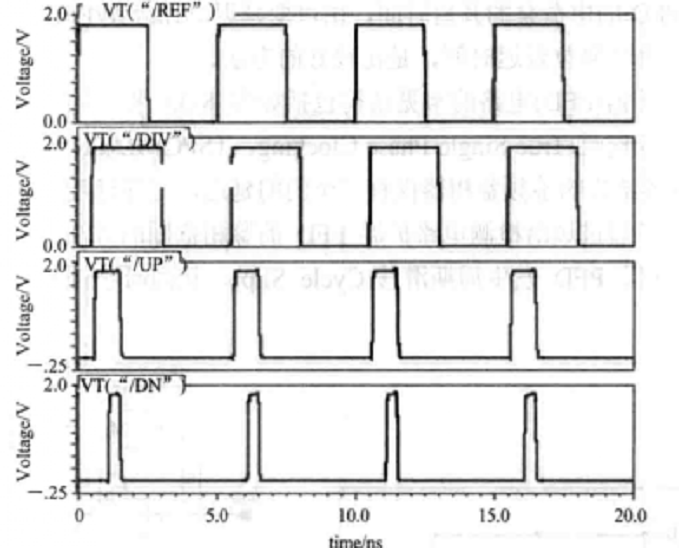

電路結構TSPC觸發器結構的鑒頻鑒相器僅有三個門的延遲,工作速度快,套用廣泛。最近又出現了通過邊沿檢測電路擴展PFD的鑒相範圍的方法,可以避免輸入相位差過大時,PFD發生周期滑移(Cycle Slip),從而減小鎖相環捕獲和鎖定時間。

特點

1、做相位比較時,dclock和data的上升沿必須出現。

2、dclock的脈衝寬度和data的脈衝寬度無關緊要。

3、鑒頻鑒相器不會鎖定在輸入數據的諧波上。

4、在環路鎖定時,鑒頻鑒相器的輸出(Up和Down)都是邏輯低電平,消除了環路濾波器輸出信號上的波動起伏。

5、這種鑒頻鑒相器的噪聲抑制能力較差。

噪聲會使data或dclock信號出現電壓起伏,由於這種鑒頻鑒相器的噪聲抑制能力較差,較大的電壓起伏會影響鑒頻鑒相器的輸出。

設計約束

鑒頻鑒相器( PFD)/鑒相器產生一個與兩個輸入信號相位差成比例的輸出信號,其中一個輸入信號是同定的,有很穩定的頻率,一般由石英晶體產生。另一個輸入信號是可變的,穩定性較差,是由振盪器的輸出信號分頻後得到的。鑒頻鑒相器/鑒相器在環路中的作用是矯正兩個輸入信號的差值,並通過微量地改變VCO的控制電壓來實現頻率鎖定。

目前有四種常用的鑒頻鑒相器/鑒相器。

(1)模擬或乘法結構鑒相器,建立在相同頻率的兩個正弦信號的相乘上。

(2)異或門結構鑒相器,基本的時序電路結構,依靠輸入信號過零點信息工作。

(3)觸發器結構鑒相器,也是一種依靠過零點工作的

時序電路。

(4)能提供頻率相關信號的結構:它是一個鑒頻鑒相器,區別於上述三種的是只能鑒相。這些模組的功能是當PLL輸出信號未鎖定時將環路鎖定。

電路結構

電路結構