FH-CDMA簡介

跳頻

跳頻是“多頻、選碼、頻移鍵控”,即用偽碼序列構成跳頻指令來控制頻率合成器,並在多個頻率中進行選擇的移頻鍵近代。它由所傳信息碼與偽隨機碼序列模二加的組合來構成跳頻指令,由它來隨機選擇傳送頻率。

碼分多址(CDMA)

碼分多址是以擴頻信號為基礎,利用不同碼型實現不同用戶的信息傳輸。擴頻信號是一種經過偽隨機序列調製的寬頻信號,其頻寬帶通常比原始信號頻寬高几個量級。常用的擴頻信號有兩類:跳頻信號和直接序列擴頻信號,本文主要介紹的是跳頻碼分多址(CDMA)。

跳頻碼分多址(FH-CDMA)

在FH-CDMA系統中,每個用戶根據各自的偽隨機(PN)序列,動態改變其已調信號的中心頻率。各用戶的中心頻率可在給定的系統帶內改變,該系統頻寬通常要比各用戶已調信號的頻寬寬得多,使用的頻道是動態變化的。FH-CDMA中各用戶使用的頻率序列要求相互正交,即在一個PN序列周期對應的時間區間內,各用戶使用的頻率在任一時刻都不相同。

FH-CDMA系統結構

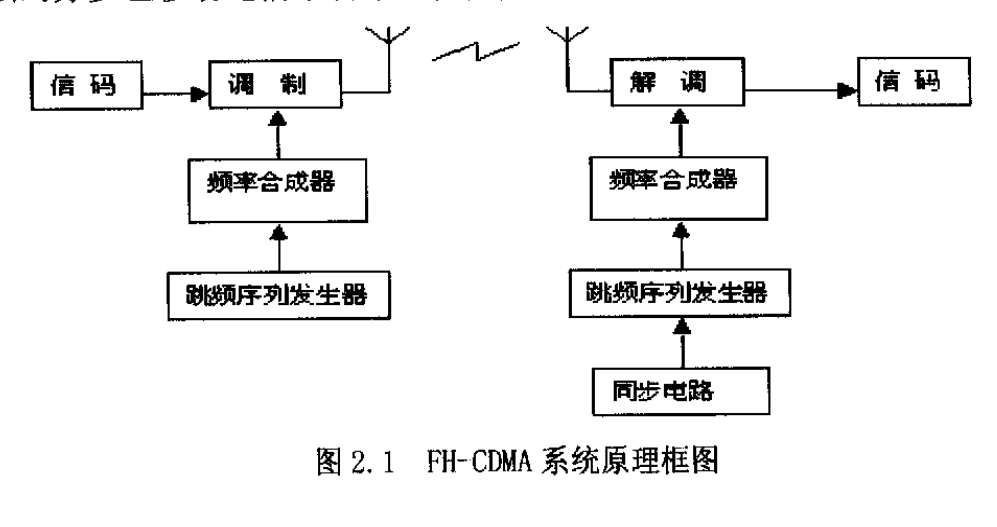

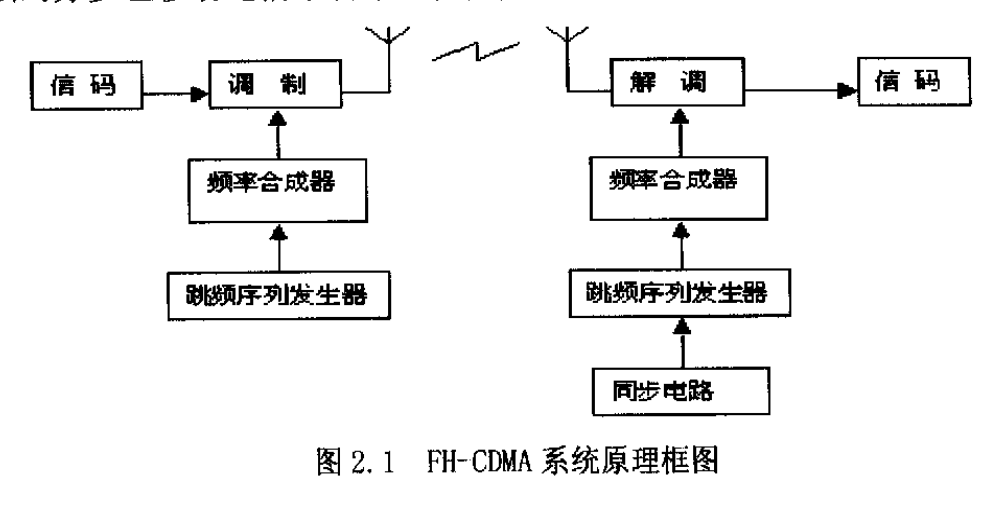

跳頻碼分多址移動通信系統原理框圖如圖所示。

基帶信號對載波調製後發射,載頻來自頻率合成器,在跳頻序列(常見PN序列即偽噪聲序列:Pseudo Noise sequence)的控制下隨機跳變(最簡單的控制方法是以序列值作為頻道號)。收端的本振亦來自跳頻序列控制的頻率合成器,接收頻率隨機跳變。當收發兩端頻率按同一跳頻序列隨機跳變,並且達到同步時,接收端就可解調出有用信息。當收發兩端頻率按不同跳頻序列隨機跳變時,兩端頻率在任何時刻都不相同或相同的機率極小,即頻率序列相互正交或準正交,接收端收不到發射端的信息。以上兩種情況,前者對應同地址FH-CDMA用戶正常通信過程;後者對應不用地址FH-CDMA用戶之間互相干擾關係。

主要性能指標

處理增益和抗干擾容限是FH-CDMA移動通信系統的兩個重要性能指標。

處理增益

處理增益G也稱擴頻增益(Spreading Gain)它定義為頻譜擴展前的信息頻寬

與頻帶擴展後的信號頻寬W之比:

在FH-CDMA通信系統中,接收機作擴頻解調後,只提取偽隨機編碼相關處理後的頻寬為

的信息,而排除掉寬頻帶W中的外部干擾、噪音和其他用戶的通信影響。因此,處理增益G反映了此通信系統信噪比改善的程度。

抗干擾容限

抗干擾容限是指FH-CDMA通信系統能在多大幹擾環境下正常工作的能力,定義為:

其中:

G:處理增益

例如,一個FH-CDMA系統的處理增益為35dB。信息數據解調的最小的輸出信噪比

<10dB,系統損耗

=3dB,則干擾容限

=35一(10+3)=22dB。這說明,該系統能在干擾輸入功率電平比擴頻信號功率電平高22dB的範圍內正常工作,也就是該系統能夠在接收輸入信噪比大於或等於-22dB的環境下正常工作。

FH-CDMA偽碼調製

在FH-CDMA通信系統中,每一個信息信號在發射端都用特定的地址碼加以調製,在接收端再用同樣的地址碼解調出信息信號。這裡的調製指的是偽隨機序列碼調製(簡稱偽碼調製),偽碼調製擴展了信號的頻譜,因此FH-CDMA通信從本質上說,是一種擴頻通信。

偽碼調製基本原理

偽碼調製是通過信息信號和偽碼波形相乘實現的,我們知道,在數位訊號中波形相乘等效於碼序列相加(模2加)。因此在數字通信中,偽碼調製就相當於信息碼序列和偽碼序列的模2加。偽碼調製中的信息碼序列和偽碼序列應具有一定的相互制約關係,具體來說有以下兩點:

既然偽碼調製是模2加,那么在相位上信息碼序列和偽碼序列就應該嚴格同步。這就要求偽碼序列和信息碼序列電路只能用一個時鐘。

信息碼序列一個碼元的持續時間一般說來應該等於偽碼序列一個周期的持續時間。也就是說偽碼序列的碼速率應等於信息碼序列的碼速率的P倍,其中P為偽碼序列的周期。由此可知,偽碼序列所需的時鐘頻率應等於信息碼序列所需的時鐘頻率的P倍。因此,偽碼調製的結果是使調製後的信號的頻率變為信息信號頻率的P倍,即起到了擴展頻譜的作用。

m序列的產生

偽碼序列的種類很多,其中m序列簡單、可靠。本文所述的偽碼發生器和跳頻圖案發生器都用m序列。

反饋移位暫存器原理

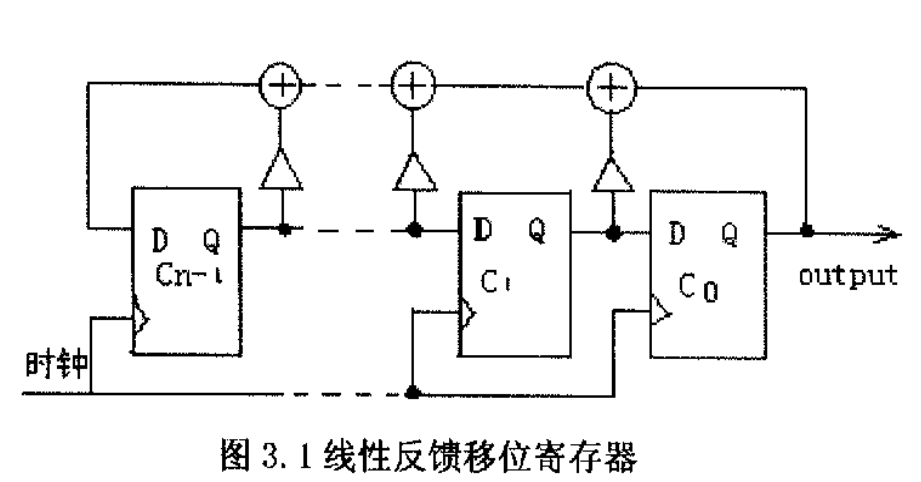

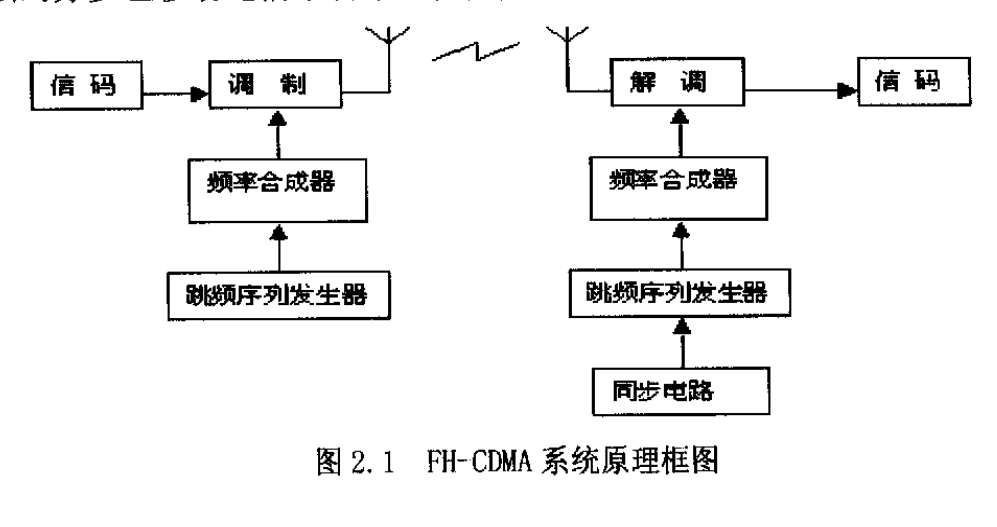

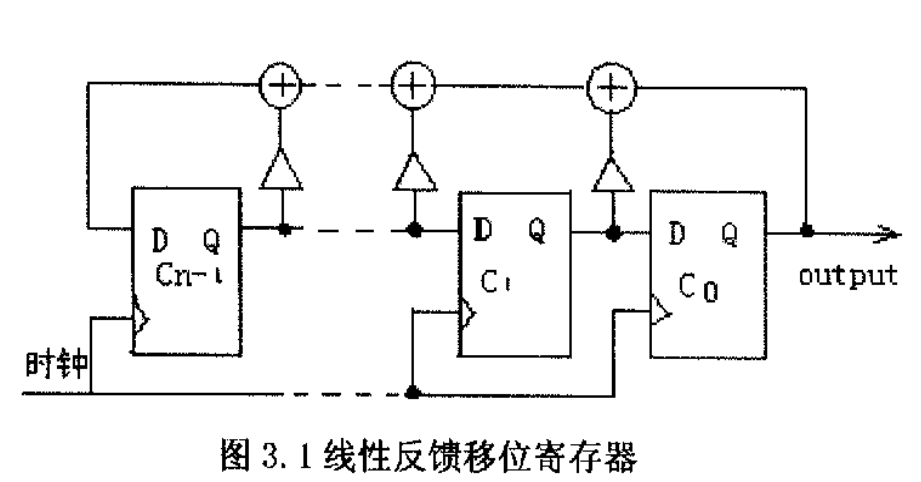

在論述m序列的產生之前,有必要介紹一下線性移位暫存器,線性反饋移位暫存器的一般結構如圖所示。它由n級存儲器、若干模2加法器(組成線性反饋邏輯網路)及時鐘脈衝發生器組成。

下面以四級(r=4)移位暫存器為例說明移位暫存器的工作過程。假定四級移位暫存器的初始狀態為(C0,C1,C2,C3),第一級為C3,第二級為C2,第三級為C1,第四級為C0。當一個時鐘到來時,每級的存數就向右移至下一級,通常末級作為輸出。這時移位暫存器的輸出就是C0。與此同時,第三級和第四級的存數C1,C0就送入模二加法器,模二加法器的輸出即為C4=C1+C0,該輸出反饋到第一級,成為第一級的新存數,這時新狀態為(C1,C2,C3,C4)。當第二個時鐘到來時,移位暫存器的新狀態又變為(C2,C3,C4,C5),此時,C5=C1+C2移位暫存器輸出為C1。隨著脈衝時鐘的不斷到來,移位暫存器的輸出將是CO,C1,C2,C3……稱為一個移位暫存器序列,它們滿足遞歸關係:

由上面分析知道,r個存儲器和若干個模二加法器形成反饋邏輯的移位暫存器稱為r級移位暫存器。它的輸出序列為C0,C1,C2,C3……。如果一個r級移位暫存器的反饋邏輯是線性的,就稱該移位暫存器為線性移位暫存器,它的輸出序列就是一個r級線性移位暫存器序列。

最大長度線性移位暫存器序列

一個r級移位暫存器共有

個不同的狀態,不管初始狀態如何,最多經過

次移位後,前

+1個狀態中必有兩個狀態是相同的。在這

個狀態中,有一個全0狀態,它輸出一個周期為1的0序列。全0狀態表示移位暫存器不工作。顯然這種狀態是我們所不希望的。在討論線性移位暫存器時,一般不考慮這種0序列,但在實際中要特別注意避免這種0序列的出現。

對於四移位暫存器共有16個狀態,除去全0狀態,共有15個狀態。移位暫存器的狀態序列和移位暫存器的輸出序列周期是一致的15個狀態序列的周期是15,所以四級線性移位暫存器的輸出序列周期是15。這是四級線性移位暫存器的最大可能周期,由此可得:r級移位暫存器,除去O狀態輸出序列外,所輸出的序列最大可能周期為27~1。我們把這種具有最大長度周期的線性移位暫存器序列稱為最大長度線性移位暫存器序列,又稱為m序列。前面介紹的四級線性移位暫存器序列就是一個m序列。

m序列是同樣級數的線性移位暫存器所產生的最大長度序列,因此它的效率是最高的,這是m序列的一個優點。m序列的最主要優點是,它具有某種隨機性,尤其是它的自相關函式具有優良的性質,所以在實際中得到了廣泛的套用。

我們在前面已經詳細介紹了m序列產生的過程,其中,我們很容易知道,偽碼發生器(包括下文將要介紹的跳頻圖案發生器)的主要電路是由移位暫存器和若干模2加法器構成的。此處不對移位暫存器再做介紹,僅在附錄1中給出我們所選用的移位暫存器(74LS195)晶片結構、時序關係圖等。

偽碼調製中的分頻技術

分頻原理

由於產生m序列的時鐘頻率(假定為

)應是產生信息碼序列的時鐘頻率(假定為

)的P倍,其中P為m序列的周期。前面說過,我們只能提供1個時鐘(

)用於產生m序列,產生信息碼序列的時鐘(

)只能通過P分頻得到,而不能另設一個時鐘,那樣的話相位就無法一致了。我們知道,通常的分頻是

分頻,而P=

-1,顯然無法直接對時鐘進行P分頻。看來只能另闢路徑了。在m序列中有這樣一個事實,即在m序列的一個周期中有且僅存一個全1狀態(連著r個1),所以每兩個周期的全1狀態的間隔恰好是P位,這說明全1狀態出現的頻率

就轉化為全1狀態檢測問題了。

分頻電路

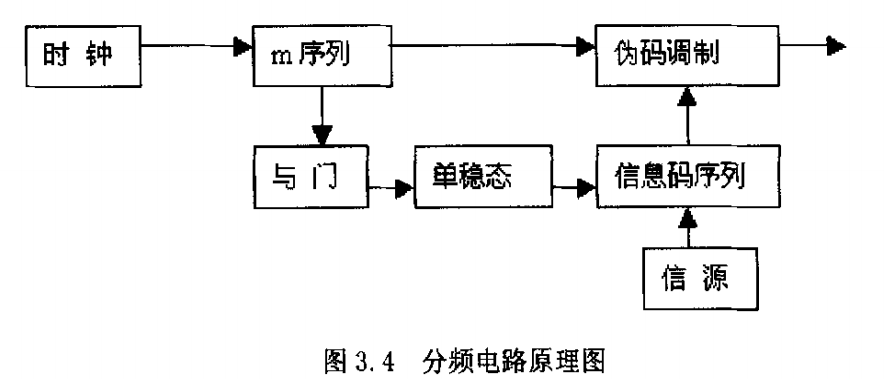

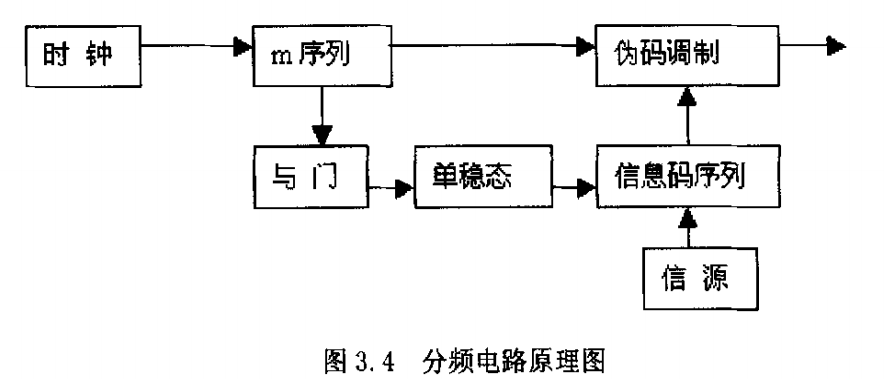

依據上述思想,可以設計出分頻電路原理如圖所示。

圖中讓m序列產生電路的r個並行輸出值通過與門。若與門輸出為高電平(1),則表明出現了全1狀態,與門的輸出脈衝的頻率就是

,這也就是我們所需要的時鐘頻率

(

=

)。與門輸出的脈衝寬度很窄,占空比很小,用它觸發得到的信息碼序列波形很不穩定。通過圖中的單穩態展寬電路可展寬脈衝寬度,增加占空比。由筆者所做實驗可知,用展寬後的時鐘脈衝觸發得到的信息碼序列波形質量令人滿意。